Digital Equipment Corporation (DEC) Alpha - DEC Alpha CPUs and cards

![]()

Pagina in costruzione

Le immagini in bianco e nero verranno sostituite con versioni a colori

Due CPU RISC Alpha: a sinistra un 21064-DB E45L a 275 MHz, a destra un 21164-CA a 333 MHz. Il 21064 EV4 è stato il primo membro della famiglia Alpha. "EV" sta per "Extended VAX" e sottolinea come queste CPU siano nate come evoluzione dei processori CISC impiegati appunto nei sistemi VAX. Il 21064 è stato il primo microprocessore CMOS la cui frequenza di lavoro e la potenza di calcolo siano state paragonabili a quelle dei super-minicomputer e di alcuni mainframe dell’epoca nonché la prima CPU CMOS a superare la "barriera" dei 200 MHz. E’ un processore superscalare a due vie (integer + floating point), superpipelined, con 8+8 KB di cache di primo livello. Contiene circa 1,68 milioni di transistor (circa 2,6 nella versione raffigurata qui, con cache da 16+16 KB. Il processo di fabbricazione è stato dapprima il CMOS4 a 0,75 micron e successivamente la sua modifica CMOS4S a 0,675 micron. Il 21064 usa un socket PGA a 431 piedini.

Vedi la documentazione elencata in: ftp://ftp.netbsd.org/pub/NetBSD/misc/dec-docs/index.html.

Ottimo articolo sulla storia delle CPU Alpha: http://www.alasir.com/articles/alpha_history/index.html.

Alpha Architecture Technical Summary: http://www.alasir.com/articles/alpha_history/press/alpha_intro.html.

Altri articoli sulla storia e l'architettura delle CPU Alpha: http://alasir.com/articles/alpha_history/epilogue_addinfo.html.

Vedi: http://www.hotchips.org/archives/hc4/2_Mon/HC4.S1/HC4.1.1.pdf; http://studies.ac.upc.edu/ETSETB/SEGPAR/microprocessors/21064%20(micro).pdf.

Vedi: http://hal.archives-ouvertes.fr/docs/00/07/35/01/PDF/RR-3188.pdf.

Anche: http://www.ece.umd.edu/~blj/microarchitecture/21064.pb.pdf; http://informatik.uibk.ac.at/teaching/ss2008/seminar/alpha.pdf.

Primo desktop basato su CPU Alpha - First Alpha-based desktop (DEC 3000AXP)

DEC Alpha (conosciuta anche come Alpha AXP) è una diffusa architettura di processori RISC a 64 bit sviluppata e prodotta dalla Digital Equipment Corporation. Questa famiglia di CPU, annunciata nel Febbraio 1992, fu progettata come successore della fortunata linea di elaboratori VAX e venne in seguito utilizzata anche da altri produttori di sistemi sia in workstation che in server. Alpha deriva da un precedente progetto RISC sviluppato e poi abbandonato da DEC alla fine degli anni Ottanta, chiamato "PRISM". Al momento dell’introduzione di Alpha, DEC utilizzava già CPU RISC nei propri prodotti ed in modo particolare i processori MIPS R2000/3000/4000 nelle DECstation. Uno dei motivi che la spinsero a sviluppare questa nuova architettura fu la convinzione che i tradizionali processori CISC della famiglia VAX (in particolar modo l’NVAX) sarebbero stati presto surclassati in termini di prestazioni dalle CPU RISC di seconda e terza generazione come ad esempio il MIPS R4400 e l’IBM POWER2. Tratti distintivi delle CPU Alpha sono l’elevata potenza in virgola mobile e la possibilità di funzionare a frequenze molto elevate (rapportate al momento dell’introduzione sul mercato), caratteristiche che le hanno poste quasi sempre in una posizione di vantaggio -almeno iniziale- rispetto ai processori concorrenti. Lo sviluppo della famiglia Alpha cessò nel 2003 quando HP (che l’anno prima aveva acquisito Compaq la quale a sua volta nel 1998 aveva rilevato il business residuo di DEC dopo la crisi e lo smembramento di quest’ultima nel corso degli anni Novanta) annunciò che i propri prodotti nei settori workstation e server avrebbero impiegato CPU Intel, in particolare Xeon ed Itanium. Alpha, un'architettura estremamente promettente nei primi anni Novanta, ha pagato caro lo scarso supporto commerciale da parte di Digital prima e di Compaq poi, nonché alcuni gravi errori compiuti dai manager DEC, legati a concezioni ormai sorpassate del mercato dei computer.

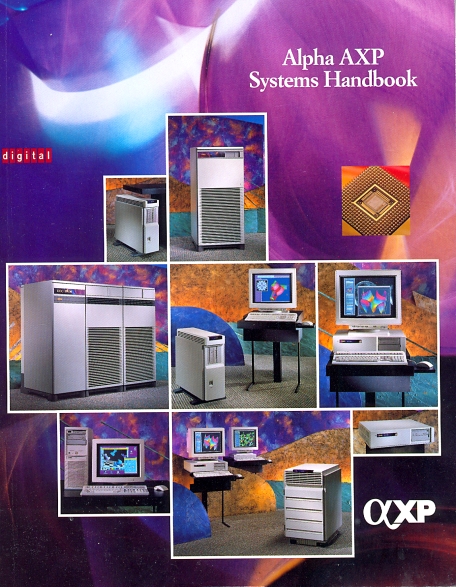

Questo manuale Digital (1993) descrive l'architettura della prima generazione di sistemi (workstation e server) basati su CPU Alpha 21064 o DECchip 21064 (EV4), in particolare il DECpc AXP/150, il DEC 3000, il DEC 4000 ed i server SMP DEC 7000 e 10000. Vedi: http://www.xbitlabs.com/articles/cpu/display/alpha.html (The History of Alpha Processors: Facts and Comments).

La prima macchina desktop DEC basata su processore Alpha è stata nel Novembre 1992 la workstation 3000 Model 500 AXP "Flamingo" che utilizzava una CPU 21064 a 150 MHz (in alto la CPU, qui sopra l'intera motherboard senza la memoria), una macchina TURBOchannel che ereditava molte caratteristiche delle preesistenti VAXstation basate su NVAX oppure MIPS. Le sue caratteristiche erano eccellenti, un po’ meno il prezzo: quasi 39.000 Dollari. La workstation DEC 3000 venne rilasciata assieme al server Alpha/VAX DEC 7000.

Vedi: http://en.wikipedia.org/wiki/DEC_3000; http://www.psych.usyd.edu.au/pdp-11/alpha_specs.html.

Vedi: http://www.linux-mips.org/pub/linux/mips/people/macro/DEC/DTJ/DTJ804/DTJ804PF.PDF (The Design of the DEC 3000 AXP Systems)

Digital AlphaStation 200 4/166 "Mustang" (1995): modulo CPU con processore DEC Alpha 21064 (EV4) a 166 MHz e 512 KB di cache L2.

Vedi: http://en.wikipedia.org/wiki/Alphastation.

Primo sistema DEC AlphaServer - First member of the DEC AlphaServer family

CPU Alpha 21064 a 190 MHz sulla scheda processore B2020A di una DEC AlphaServer 2100 "Sable" (1994, vedi qui per i nomi delle workstation e dei server Alpha). Si trattava di una macchina SMP a due vie con architettura EISA/PCI impiegabile come server midrange generico caratterizzato da un eccellente (per l’epoca) rapporto prezzo/prestazioni (vedi). Il modello 2100 è stato il primo membro della fortunata famiglia DEC AlphaServer.

Versione con Alpha 21064A a 275 MHz e 4 MB di cache L2 (DEC B2024-AA, rev. D03) della scheda CPU per AlphaServer 2100 ("Sable45", 1994/5). Questo processore è identificato dalla sigla EV45 ed è un'evoluzione dell'originario 21064 (o EV4) introdotta nell'Ottobre 1993; ha raggiunto la frequenza massima di 300 MHz. Rispetto al 21064 contiene alcuni importanti miglioramenti architetturali: cache di primo livello più ampie (16 KB contro 8) e protette con controllo di parità; minor numero di cicli di clok richiesti per l'esecuzione delle moltiplicazioni e delle divisioni in virgola mobile; unità di previsione della destinazione dei salti (branch-prediction unit) più efficiente. Il 21064A contiene 2,8 milioni di transistor ed è fabbricato con processo CMOS-5 a 0,5 micrometri.

CPU Alpha 21064 a 233 MHz per DEC AlphaStation 400 4/233 "Avanti" (vedi). Era questa una macchina entry level ISA/PCI che poteva montare indifferentemente una CPU Alpha oppure una scheda con singolo/doppio processore Pentium a 100/120 MHz. Il sistema operativo era Windows NT per Alpha. L’EV45 o 21064A, annunciato al Microprocessor Forum nell’Ottobre 1993, è una versione evoluta dell’EV4 originale fabbricata con processo CMOS5 a 0,5 micron, dotata di cache raddoppiate (16 + 16 KB) e di alcune altre modifiche hardware tese ad aumentarne l’efficienza. Contiene 2,85 milioni di transistor. La gran parte dei chip EV45 sono stati fabbricati da Mitsubishi. La scheda mostra qui fa uso del chipset DEC Apecs 21071, introdotto nel 1994. Originariamente DEC non aveva progettato un chipset standard per il 21064: le macchine basate su questa CPU impiegavano ASIC realizzati ad hoc. In seguito (1994) il successo commerciale ottenuto dal processore e le richieste da parte dei fabbricanti di sistemi portarono alla realizzazione di un chipset, il 21070 Apecs (o 2107x), che divenne lo standard per i sistemi EV4/EV45. Apecs esiste in due versioni, denominate rispettivamente DECchip 21071 e DECchip 21072; la prima, con un bus di memoria a 64 bit, è pensata per le workstation e server di fascia bassa e la seconda (con un bus di memoria a 128 bit) per i server SMP. Il 21071 supporta un massimo di 2 GB di memoria, protetta da parità; il 21072 può gestire un massimo di 4 GB di memoria con ECC. Entrambe queste versioni contengono i medesimi componenti base ed in particolare il controller di cache e memoria COMANCHE, uno o più data-slice DECADE ed il controller del bus PCI (EPIC). DECADE utilizza slice da 32 bit, quindi il 21071 contiene due di questi chip contro i 4 del 21072 (che come ricordato ha un bus di memoria a 128 bit).

Prima macchina Alpha con Windows NT - First Alpha system running Windows NT

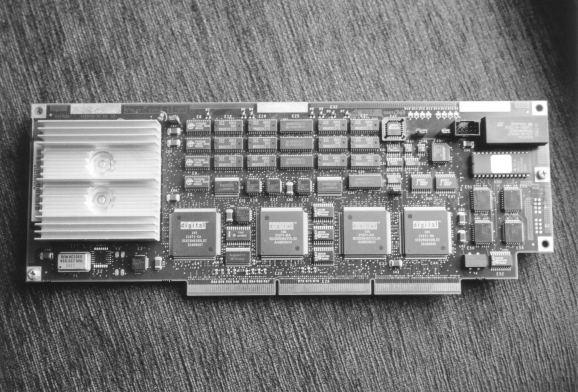

Motherboard di un sistema DEC 2000 (DECpc AXP/150) "Jensen" (1993) - In alto a destra la CPU Alpha 21064 EV4 a 150 MHz, circondata da 512 KB di cache di secondo livello (B-cache) realizzata con chip SRAM da 17 ns. Come si può notare, si tratta di una scheda madre "tipo PC" con un processore non x86: a parte quest’ultimo ed un po’ di componenti attorno ad esso (glue logic), tutto il resto è preso direttamente dal mondo dei personal computer IBM compatibili (vedi il chipset Intel per EISA). Il 2000 AXP-150 (o DECpc AXP/150) è stata nel Settembre 1993 la prima macchina Alpha con architettura standard EISA nonché il primo sistema con CPU Alpha ad utilizzare il sistema operativo Windows NT (vedi).

Un'altra versione della scheda del DECpc AXP/150 (notare la diversa disposizione delle EPROM del BIOS), sempre con CPU Alpha 21064 a 150 MHz. Il nome "Jensen", col quale si è identificato l'AXP/150, era in origine il nome della sola scheda madre.

Vedi: http://www.hpl.hp.com/hpjournal/dtj/vol6num1/vol6num1art4.pdf (The Evolution of the Alpha AXP PC).

Anche: http://www.1000bit.it/ad/bro/digital/djt/dtj_v06-01_1994.pdf.

L’impiego di dispositivi standardizzati consentiva a DEC di contenere il prezzo di vendita di questi sistemi entry level, e di facilitare nel contempo il riutilizzo di periferiche acquistate dai potenziali utenti per l’impiego su PC ad architettura Intel. I sistemi DEC 2000 ebbero un discreto successo, superato però da quello delle più avanzate Personal Workstation basate su 21164 e bus PCI; furono i primi elaboratori di fascia medio – bassa sui quali "girò" la versione Alpha di Windows NT. Dal momento che la CPU Alpha 21064 era incompatibile con il chipset Intel EISA 82350, DEC utilizzò un insieme di buffer ed interfacce tra il suo bus di sistema ed il chipset stesso, in modo tale da simulare la presenza di un "normale" bus 486. Questa soluzione era intrinsecamente inefficiente ed infatti il bus dell’AXP-150 ha una velocità di trasferimento dati di soli 25 MB/s contro i 33 MB/s dei consueti sistemi EISA. In effetti il DECpc AXP/150 impiega un'architettura basata su due distinti bus di sistema: l'Host Bus (H-Bus) che fa da interfaccia tra la CPU e il sottosistema di I/O, ed il Local Peripheral Bus (L-bus) che connette le principali periferiche di I/O e il bus EISA. L'H-bus, che è controllato direttamente dalla CPU tranne durante le operazioni di DMA (quando viene controllato dal chipset EISA) provvede all'emulazione della presenza di un "ordinario" 486DX, richiesta dal chipset Intel 82350DT (vedi sopra). Il Local Peripherals Bus è basato su un componente standard nei PC AT dell'epoca, l'Integrated Peripherals Controller VLSI VL82C106 "Combo Chip".

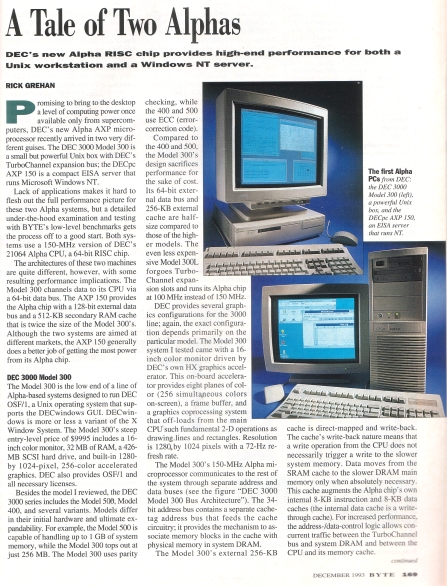

Articolo di Byte, Dicembre 1993, dedicato alle due prime workstation Alpha prodotte da Digital.

Vedi: http://www.alphalinux.org/faq/FAQ-9.html oppure http://en.wikipedia.org/wiki/DEC_2000_AXP.

La macchina è descritta anche qui: http://john.ccac.rwth-aachen.de:8000/alf/axp150/.

Scheda processore di un AlphaServer 1000 4/266 "Mikasa+" con CPU DEC 21064 a 266 MHz (1995, vedi) e chipset Apecs. L’AlphaServer 1000 era un sistema midrange a singola CPU basato su architettura EISA/PCI; la memoria RAM si poteva espandere fino ad un massimo di 1 GB (vedi). La scheda contiene il chipset DEC Apecs 21072 (riconoscibile dalla presenza di due integrati DECADE anziché di uno solo come nella versione 21071 per workstation).

AlphaServer InfoCenter: http://www.internorth.com/server-info/.

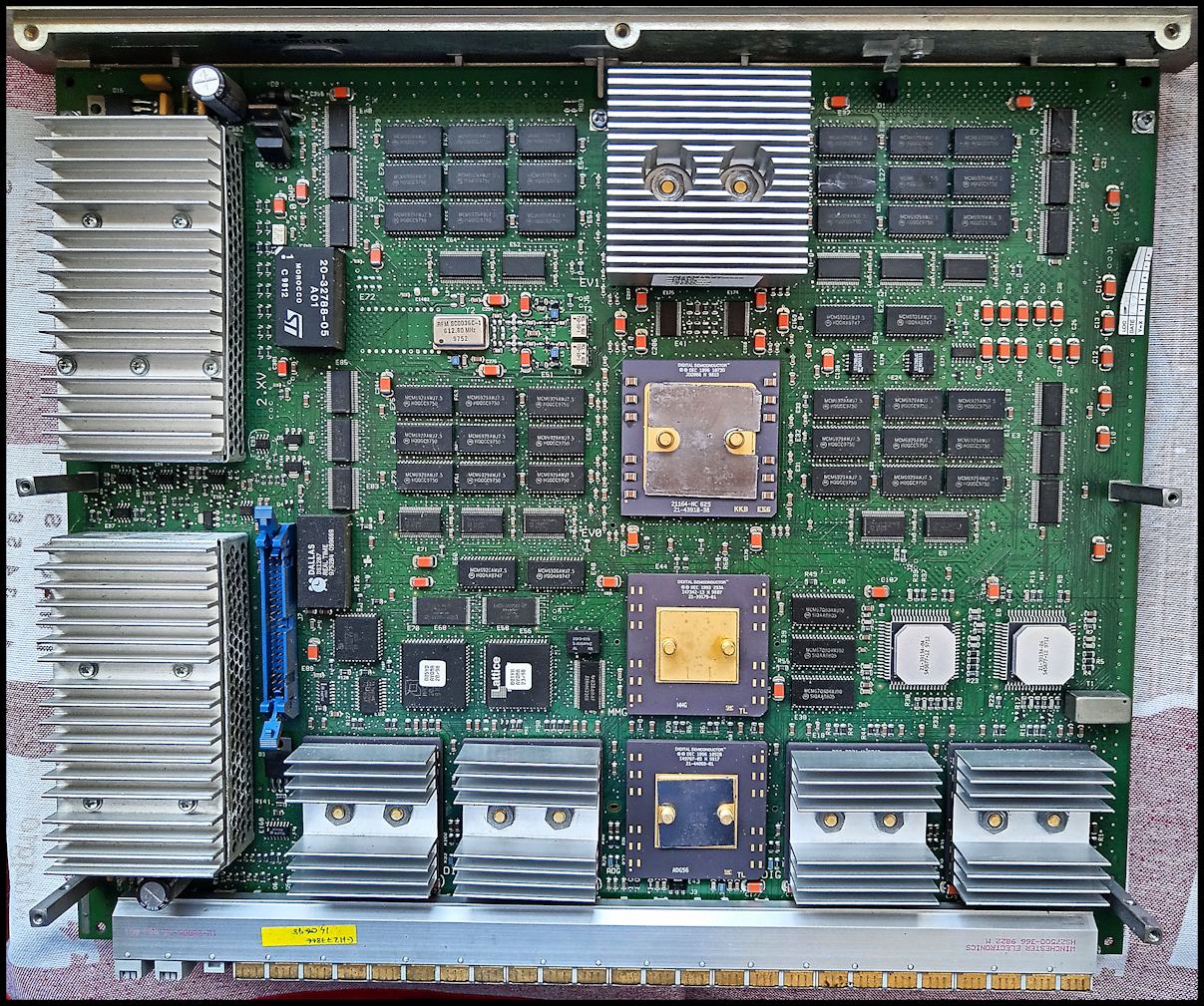

Scheda CPU DEC E2057-AA (KN7AB-AA) per VAX 7000/700 "Laser/Krypton" (1994, vedi) con processore Alpha 21064 a 182 MHz, 4 MB di cache L2 e chipset LEVI. Questo server era una macchina SMP a 1-6 vie di fascia alta, evoluzione della precedente versione /600 ("Laser/Ruby") che poteva montare indifferentemente CPU NVAX+ oppure Alpha EV4 o EV45. La versione con CPU Alpha è anche conosciuta come DEC 7000 AXP. Il 7000/600 con CPU a EV4 182 MHz (Luglio 1993, vedi oppure qui) è stato il primo server di questa fascia basato su processori Alpha. I moduli contenenti i processori (NVAX+ o Alpha) sono connessi da un bus ad alta velocità, pipelined, chiamato LaserBus o LSB che funziona a 50 MHz ed ha una banda di 640 MB/s. L’architettura di bus dei moduli CPU Alpha e NVAX+ è identica, il che consentiva agli acquirenti di queste macchine di trasformarle con facilità passando dall’una all’altra famiglia di processori (vedi per una tabella delle CPU utilizzate nei sistemi VAX in genere). Lo stesso tipo di scheda, però con CPU funzionante a 200 MHz, era impiegato nel server DEC 10000 AXP, il sistema Alpha di maggiore potenza e più alto livello.

CPU DEC Alpha 21164 a 333 MHz di AlphaServer 800 5/333 "Corelle" (1997, vedi, oppure qui) - L’Alpha 21164 (EV5) è una CPU superscalare a quattro vie, due integer e due floating point, introdotta nel 1995 con frequenza massima di lavoro iniziale di 266 MHz, innalzata in seguito fino a 666 MHz (1998). Il 21164 è stato annunciato da DEC nell’Agosto 1994 all’annuale conferenza californiana "Hot Chips". Il suo core è un’evoluzione migliorata ed ottimizzata dell’EV45 appartenuto alla precedente generazione 21064. Contiene una cache on-chip di secondo livello da 96 KB write back di tipo set-associative a tre vie. La cache di primo livello è ampia invece 8 + 8 KB. Il 21164 è formato da 9,3 milioni di transistor realizzati con processo CMOS-5 a 0,50 micron con 4 livelli di metallizzazione in alluminio. E’ stato il primo microprocessore commerciale a superare i 300 MHz di frequenza di clock. Questa scheda utilizza un chipset DEC Alcor2 (21172).

Vedi: http://www.alasir.com/articles/alpha_history/press/ev5_hotchips.html, o http://www.alasir.com/articles/alpha_history/press/ev5_announce.html.

Vedi: http://www.cs.cmu.edu/afs/cs/academic/class/15740-f03/public/doc/alpha-21164-prod-brief.pdf.

Vedi: http://www.hotchips.org/archives/hc8/2_Mon/HC8.S1/HC8.1.2.pdf; http://www.cis.upenn.edu/~cis501/papers/Alpha21164.pdf.

Anche: http://www.hotchips.org/archives/hc6/2_Mon/HC6.S1/HC6.1.1.pdf; http://www.hpl.hp.com/hpjournal/dtj/vol7num1/vol7num1art9.pdf.

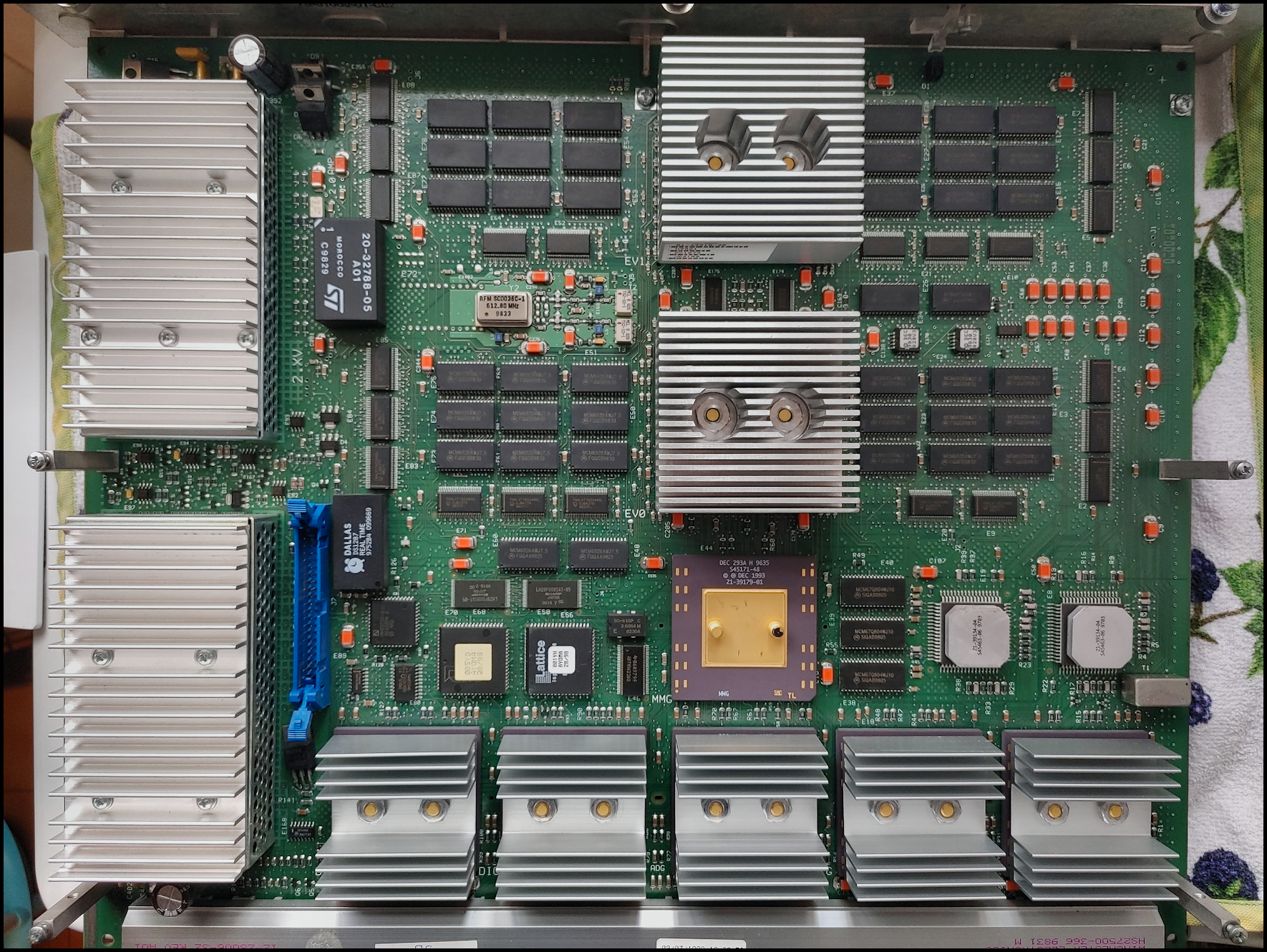

DEC B2040-AB, 1995, scheda processore per Alphaserver 2100 5/250 "Gamma-Sable" con CPU Alpha 21164 (EV5) funzionante a 250 MHz e 4 MB di cache L2. Gli Alphaserver 2100 sono macchine SMP a 1-4 vie con architettura PCI/EISA. L'Alpha 21164 ha fatto il suo debutto all'inizio del 1995 alla frequenza di 266 MHz. In alcune macchine questa CPU funzionava a 250 MHz, come nel caso qui sopra. La prima versione del 21164 ha raggiunto la frequenza massima di 333 MHz; la sua evoluzione 21164A è stata spinta fino a 666 MHz. L'Alpha 21164 impiega due tensioni di lavoro: 2,0 e 3,3 V (quest'ultima per l'I/O). A 300 MHz assorbe 51 W. E' contenuto in un package IPGA (Interstitial-PGA) con 499 piedini. Le CPU 21164 sono state prodotte da DEC nello stabilimento di Hudson (Massachusetts, USA); nel 1996 la Samsung iniziò la fabbricazione in Corea del Sud dei processori 21164A come second-source. La versione 21164A contiene 9,6 milioni di transistor ed è stata prodotta con processo CMOS-6, a quattro strati di metallizzazione in alluminio, a 0,35 e successivamente a 0,30 micron. Impiega un'unica alimentazione a 3,3 V.

Scheda DEC B3002 (KN302-AB) con CPU Alpha 21164 EV5 a 300 MHz per AlphaServer 4100 5/300 "Wrangler" (1997, vedi). Accanto alla CPU c’è una cache di terzo livello ampia 2 MB. L’AlphaServer 4100 era un server midrange SMP a 4 vie (CPU a 300-400 MHz) con un massimo di 8 GB di memoria RAM. Questa scheda CPU è stata la prima prodotta da Digital ad usare una cache di secondo livello sincrona (in luogo della tradizionale cache asincrona). Per il 21164 DEC sviluppò più chipset dalle diverse caratteristiche. Innanzitutto, i server di fascia alta (Alphaserver 8200, 8400) impiegano ASIC progettati e fabbricati ad hoc. In secondo luogo, dal progetto del chipset Apecs (2107x) per 21064 derivarono due distinti chipset conosciuti rispettivamente come DECchip 21171 (Alcor) e DECchip 21172 (Alcor2). Alcor è un'evoluzione del 21071 aggiornata alle specifiche di bus del 21164; impiega due soli tipi di dispositivo contro i tre dell'Apecs ed in particolare un chip di controllo della memoria e del bus PCI ed un numero variabile (massimo 4) di data-slice. Il 21171 implementa un bus di memoria a 256 bit e supporta lo standard PCI-X a 64 bit. Alla fine del 1995 venne introdotto un terzo chipset, orientato alle macchine di fascia bassa, il 21174 Pyxis che supporta un massimo di 512 MB di DRAM (con o senza ECC) con bus di memoria a 128 bit.

Vedi: http://h18000.www1.hp.com/products/quickspecs/SOC/QB0066PF.PDF.

Motherboard di AlphaServer 1200 5/533 "Tincup" (1997) con un modulo CPU Alpha 21164A a 533 MHz e 4 MB di cache L2 (la macchina può funzionare come SMP a 2 vie installando un altro modulo).

Vedi: http://www.compaq.com/alphaserver/download/as1200ug.pdf; http://h18002.www1.hp.com/alphaserver/archive/1200/.

Motherboard di una workstation desktop DEC AlphaStation 500 5/500 "Bret" (1997, vedi), una macchina PCI con CPU Alpha 21164 EV56 a 500 MHz affiancata da una cache di terzo livello ampia 2/8 MB. Annunciata nel Luglio 1996, la versione a 500 MHz del 21164 era il più veloce microprocessore fabbricato fino a quel momento. L’EV56 è un’evoluzione del 21164 EV5 presentata da DEC nell’Ottobre 1995 e realizzata con processo CMOS6 a 0,35 micron (9,66 milioni di transistor integrati). Rispetto all’EV5 contiene alcuni miglioramenti nell’architettura e nel set di istruzioni. I chip EV56, come gli EV5, sono fabbricati da Samsung. Questa motherboard è basata su chipset DEC Alcor (21171) realizzato con ASIC LSI Logic. L’AlphaStation 500 era una workstation desktop di fascia alta (vedi per le prestazioni, oppure le caratteristiche) che quando venne presentata nell’Agosto 1996 (vedi) superava in potenza di calcolo tutte le dirette concorrenti Sun, IBM ed SGI.

Vedi: http://www.alasir.com/articles/alpha_history/press/ev56-500_announce.html.

Scheda madre Microway "Screamer-LX" per OEM (1999/2000), in formato ATX-compatibile, con CPU 21164 EV56 a 600 MHz con 4 MB di cache L3 da 7 ns, architettura ISA/PCI (chipset standard Intel - SMC) e chipset di sistema DEC Pyxis. Microway è stato tra i maggiori produttori di piattaforme OEM basate su processori Alpha. Questo tipo di schede, poco diffuso in Europa, è relativamente comune negli USA dove è stato impiegato da molti integratori di workstation grafiche.

Scheda CPU per AlphaServer 1000 5/500 "Primo" con processore Alpha 21164 a 500 MHz (1997/8), 1 MB di cache L3 e chipset Alcor-2 (21172).

Scheda CPU E2056-DA Turbo-Laser (1995), SMP con due processori Alpha 21164 a 300 MHz e 4 MB di cache di terzo livello ciascuno. Questa scheda era utilizzata nel server AlphaServer AXP 8400, una macchina di fascia alta che poteva contenere un massimo di 12 CPU 21164 e 14 GB di RAM; al momento della sua introduzione (vedi) questo sistema, la cui potenza di calcolo in virgola mobile raggiungeva un valore di picco di 6,6 GFLOPS (vedi), era il più potente computer basato su microprocessore(i). "Oltre" c’erano solo i supercalcolatori.

Scheda SMP E2065-DA con 2 processori Alpha 21164 a 625 MHz (DEC Alphaserver 8000).

Scheda E2065 per Alphaserver 8000 con 2 CPU Alpha 21164 a 500 MHz.

CPU Alpha 21264 EV6 a 500 MHz fabbricata da Samsung - Annunciato nell’Ottobre 1996, il 21264 (EV6) raggiunse la fase di produzione commerciale solamente nel Febbraio 1998, quando DEC già si trovava in fase di liquidazione. Inizialmente le frequenza di lavoro era compresa tra 433 e 600 MHz; in seguito venne innalzata fino ad 1,26 GHz. Rappresenta un notevole passo in avanti rispetto all’EV5, in primo luogo perché ha introdotto nella famiglia Alpha l’esecuzione fuori ordine (out of order execution) e il register renaming.Il 21264 è una CPU superscalare a 6 vie (4 integer, 2 floating point); integra 15,7 milioni di transistor ed è contenuto in un package IPGA a 587 piedini.

Vedi: http://www.compaq.com/alphaserver/download/ev6chip.pdf (The Alpha 21264 Microprocessor Architecture).

Vedi: Alpha 21264 Microarchitecture; http://www.star.bnl.gov/public/daq/HARDWARE/21264_data_sheet.pdf

Vedi: http://www.cs.virginia.edu/~dp8x/alpha21264/presentations/alpha_mmz.pdf; http://impact.crhc.illinois.edu/ece512/papers/21264.pdf.

Anche: http://www2.computer.org/portal/web/csdl/doi/10.1109/40.755465 (è necessaria la registrazione).

Anche: http://www.cs.umbc.edu/help/architecture/alpha21264.pdf; http://cseweb.ucsd.edu/classes/sp00/cse241/alpha.pdf.

Anche: http://www.13thmonkey.org/documentation/Alpha/21264.pdf; http://www.hotchips.org/archives/hc10/2_Mon/HC10.S1/HC10.1.1.pdf.

CPU 21264 a 600 MHz sulla scheda processore di un Compaq Alphaserver ES20 con 8 MB di cache.

Scheda CPU con processore Alpha 21264A a 667 MHz, con 8 MB di cache L2, fabbricata da Compaq per l'Alphaserver ES20/40 (1997).

Modulo CPU con processore Alpha 21264A (EV67) a 667 MHz (Compaq AlphaServer XP1000) e 4 MB di cache L2. Utilizza il chipset DEC "Tsunami" (vedi: http://www.compaq.com/alphaserver/workstations/retired/xpseries/xp1000/whitepapers.html). "Tsunami", anche conosciuto come "Typhoon" (DECchip 21272), è stato il primo chipset per la CPU 21264. Concettualmente deriva dal chipset Alcor2 per 21164A; supporta SMP a due, tre oppure 4 vie con uno o due bus PCI-X a 33 MHz. Il bus di memoria può essere ampio 128, 256 o 512 bit e funziona a 83 MHz (con un'ampiezza di banda massima pari a 5,2 GB/s). Il 21272 è formato da 3 distinti componenti, chiamati C-chip (controller di memoria), P-chip (controller PCI) e D-chip (data-slice). Per ciascuna CPU è richiesta la presenza di un C-chip; il chipset può contenere uno o due P-chip e da due a quattro D-chip a seconda dell'ampiezza del bus di memoria (ciascun D-chip "copre" 64 bit). Dal progetto del Typhoon derivò in seguito il chipset Irongate (AMD-751/761) sviluppato da AMD a supporto del processore Athlon, che pur essendo una CPU x86 impiega il medesimo protocollo di bus dell'Alpha 21264.

Vedi: http://www.compaq.com/alphaserver/download/wp_alpha_tech_apr00.pdf.

Scheda CPU di un server SMP Compaq AlphaServer GS (il modello dovrebbe essere il 140), 1998, con due processori Alpha 21264 (EV6) a 550 MHz.

Scheda CPU di server SMP Compaq AlphaServer ES40 6/667 "Clipper", con un modulo processore 21264A a 667 MHz (può ospitarne fino a 4).

Scheda CPU E2063DB (KN7CG) di Compaq AlphaServer GS60/GS140 (8200/8400, classe "Turbolaser", vedi), con due processori Alpha 21264 (EV6) a 525 MHz e 8 MB di cache L2 ciascuno.

Vedi: http://www.compaq.com/alphaserver/download/gs60e_gs140_tech_sum.pdf.

Nodeboard (modulo processore) di un calcolatore Cray T3E-600 (1995), con 4 CPU 21164 a 300 MHz. Il Cray T3E è un supercomputer a parallelismo massiccio (MPP, Massively Parallel Processor) introdotto da Cray nel Novembre 1995. Può contenere da un minimo di 8 ad un massimo di 2.076 CPU EV5, originariamente a 300 MHz innalzati poi fino a 675 MHz nel modello -1350. Direttamente derivato dal predecessore T3D (1993, basato su processori Alpha 21064, prima macchina Cray a parallelismo massiccio), il T3E è un calcolatore a memoria distribuita (ogni CPU ha la sua RAM locale) nel quale i nodi (processori) sono interconnessi mediante una rete toroidale a tre dimensioni. Ciascun nodo contiene da 64 MB a 2 GB di RAM ed è connesso al resto del sistema tramite un router a 6 vie con una banda di 480 MB/s. Le periferiche, inclusa le memorie di massa (dischi, nastri ecc.) sono invece collegate ad un apposito sottosistema di I/O chiamato GigaRing. Il Cray T3E esiste sia nella versione con raffreddamento ad aria (Air Cooled, AC) che ha un massimo di 128 processori, sia in quella con raffreddamento a liquido (LC) con un massimo di 2.048 CPU disponibili per l'utente (alcuni processori sono riservati al sistema). Un Cray T3E-1200 con 1.480 processori è stato il primo supercalcolatore commerciale a superare, nel 1998, la barriera di 1 TeraFLOP di velocità di calcolo.

Vedi: http://www.spikynorman.dsl.pipex.com/CrayWWWStuff/t3e880.html; http://docs.cray.com/books/004-2518-002/html-004-2518-002/004-2518-002-toc.html.

Anche: http://www.spikynorman.dsl.pipex.com/CrayWWWStuff/Cfaqp3.html.

Vedi: http://www.lrr.in.tum.de/~gerndt/home/Teaching/SS2007/Hochleistungsarchitekturen/05NUMA.pdf.

Vedi: http://cug.org/5-publications/proceedings_attendee_lists/1997CD/S96PROC/383_386.PDF; http://www.nsc.liu.se/systems/retiredsystems/t3e/.

Vedi: http://www2.it.lut.fi/kurssit/04-05/010652100/PDF/Group2_2004.pdf; http://www.filibeto.org/~aduritz/truetrue/supercomputing/cray/datasheets/t3e.pdf.

Vedi: http://www.phys.uu.nl/~steen/web03/t3e.html;

Sull'interconnessione dei processori nel T3E: http://www.cs.uiuc.edu/class/sp08/cs533/reading_list/t3e.pdf.

Sui supercomputer Cray in generale (FAQ): http://www.faqs.org/faqs/computer/system/cray/faq/.

Sui calcolatori paralleli: http://ssd.sscc.ru/PaCT/hardware/computer/; http://polaris.ing.unimo.it/didattica/reti/LucidiPDF/ARCHITETTURE_PARALLELE.pdf.

Anche: http://www.flickr.com/photos/stiefkind/4018952235/; http://www.computermuseum.org.uk/fixed_pages/cray_T3E.html.

Sull'architettura del T3D: http://www.bitsavers.org/pdf/cray/HR-04033_CRAY_T3D_System_Architecture_Overview_Sep93.pdf