Processori Digital Equipment Corporation (DEC) - DEC processors

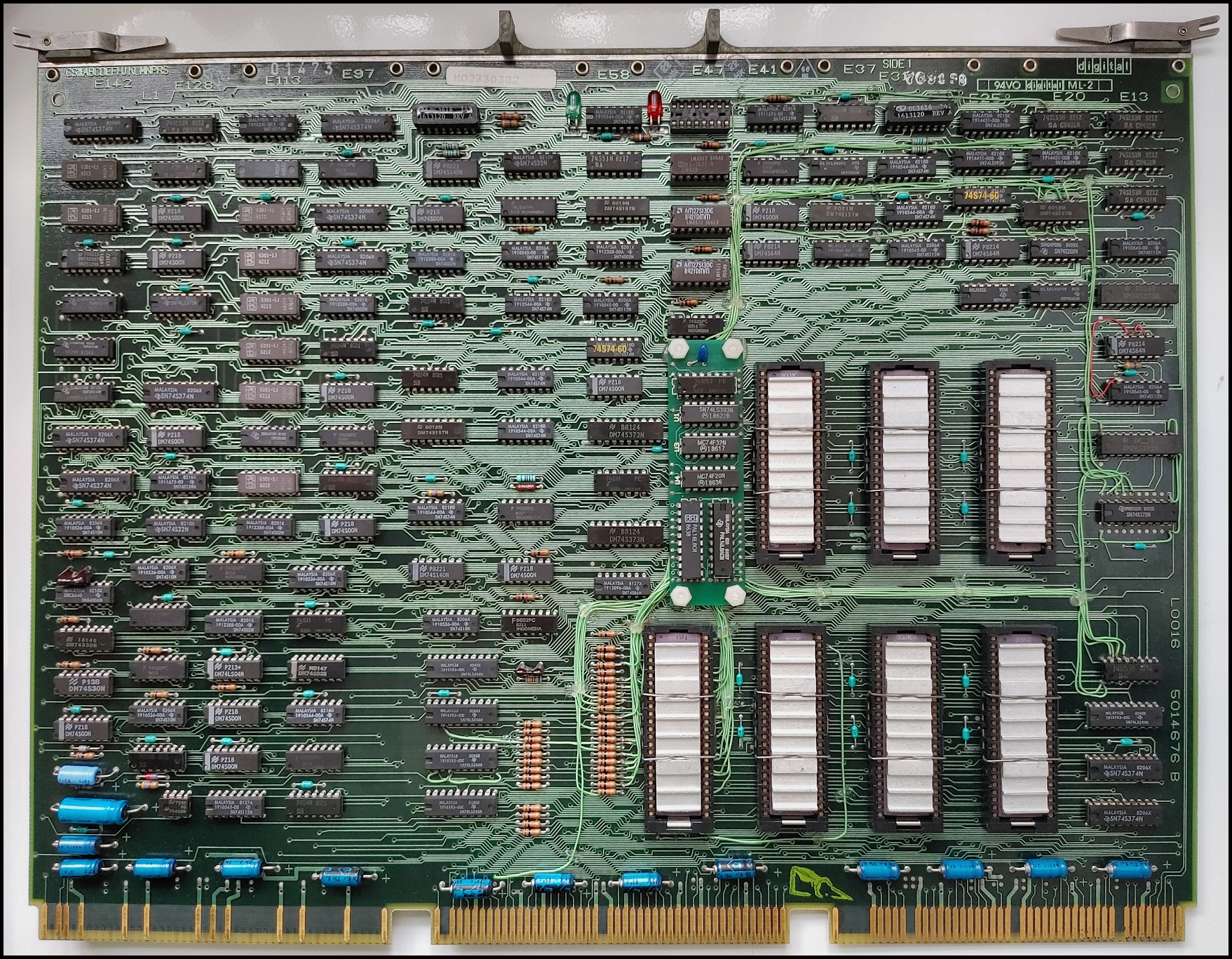

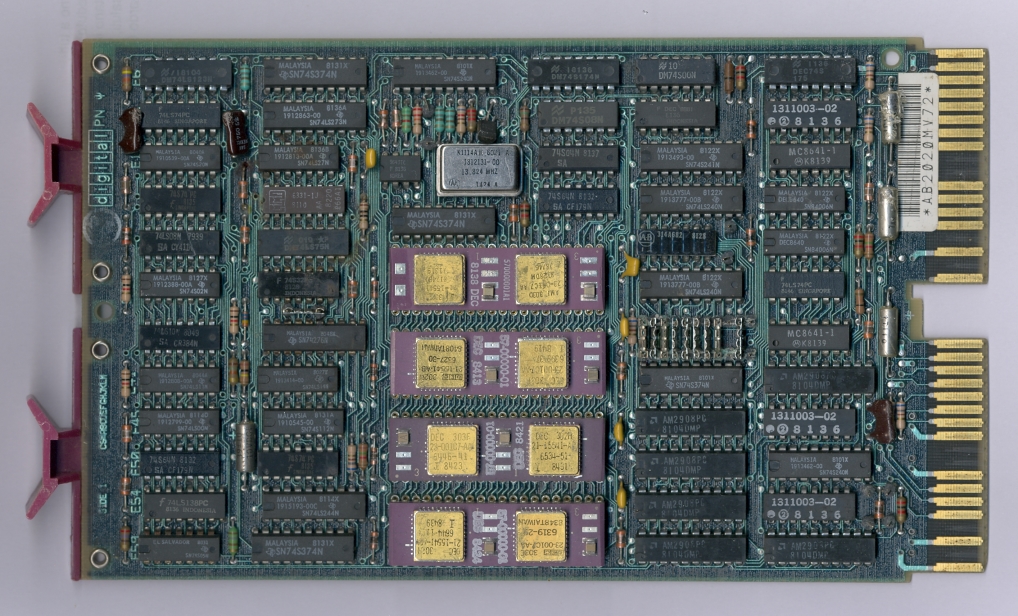

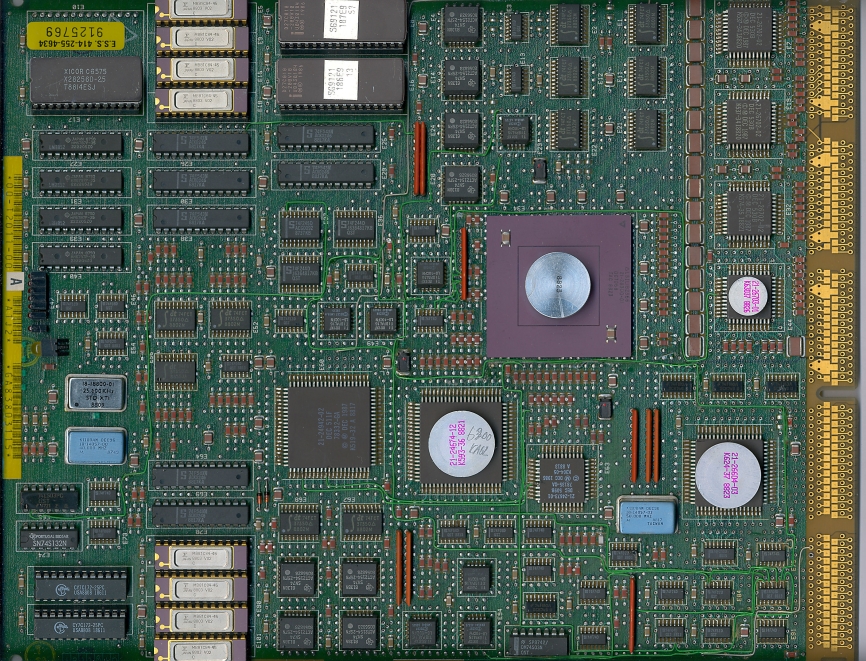

Scheda della CPU di un PDP 11/04 (1979) - Volendo essere precisi non si tratta di un vero "processore DEC", dal momento che questa CPU è realizzata secondo l’uso dell’epoca con componenti standard TTL (ad esempio l’ALU impiega 4 TTL 74181, visibili nella parte destra dell’immagine). Questa scheda è comunque interessante perché dà un’idea di come fossero costruiti i minicomputer negli anni Settanta e nello stesso tempo consente di apprezzare quale sia il risparmio di spazio ottenibile con l’impiego di microprocessori e/o circuiti integrati LSI (vedi qui sotto). Il PDP 11/04 era una versione semplificata del PDP 11/34 senza supporto della memoria virtuale né delle funzioni di memory management (vedi).

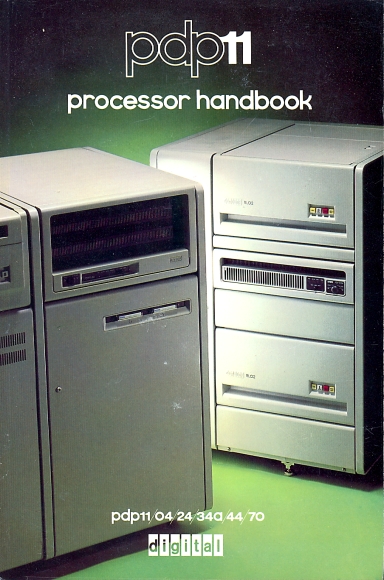

Un manuale Digital (1981) dedicato all'hardware della famiglia PDP 11.

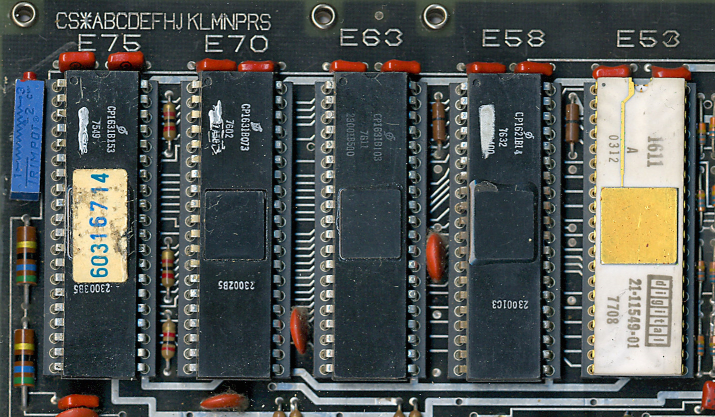

Il PDP 11/44 (qui sopra una scheda della CPU KD11-Z, con 4 ALU bitslice 74181), introdotto nel 1979, è un minicomputer derivato dal PDP 11/34 e considerato un'alternativa a basso costo al modello 11/70. L'11/44 ha una cache da 8 KB e supporta fino a 4 MB di memoria RAM (vedi: http://research.microsoft.com/en-us/um/people/gbell/digital/timeline/1979-4.htm); è stato l'ultimo modello della famiglia PDP 11 realizzato con componenti a media scala di integrazione e bitslice (TTL 74181 nella CPU, Am2901 nella FPU). La scheda raffigurata qui è il datapath M7194.

Vedi: http://www.j-hoppe.de/PDP-11/My_PDP-11_44/my_pdp-11_44.html; http://legacy.pdp11.co.uk/profiles/by-id/24/.

Vedi: http://decpicted.blogspot.com/2010/02/dec-m7094-pdp-1144-data-path.html.

Anche: http://www.conservapedia.com/PDP-11; http://www.psych.usyd.edu.au/pdp-11/models.html.

Anche: http://www.olddec.nl/Thanks-41-Years/PDP11.htm; http://www.corestore.org/pdp.htm; http://www.xs4all.nl/~geerol/en/GAL/index.html.

Collezione di minicomputer DEC PDP 11: http://www.pdp-11.nl/.

Prima implementazione LSI dell’architettura PDP - First LSI-based PDP CPU

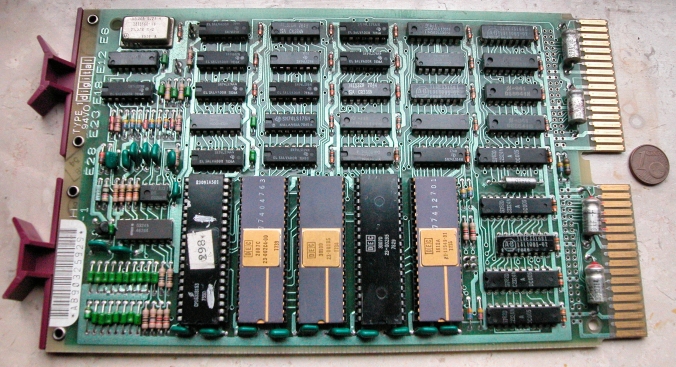

Scheda Unibus DEC M7264-BB o KD11-F (l’esemplare è del 1979). Contiene una CPU DEC LSI-11, che è stata la prima implementazione in forma di microprocessore (anche se su più chip) dell’architettura PDP. Questa scheda esiste in diverse versioni, con o senza RAM (8 KB) a bordo, ed è stata usata nei calcolatori PDP 11/03. La CPU è formata da più circuiti integrati e precisamente: il control chip 23-002C4; il data chip 21-11549-00 o -01 (o 21-001C3-0x); due "microms" o ROM di microprogramma 23-002B5 e 23-001B5 (oppure una, 23-004B5); un’opzione floating point (KEV-11), 23-003B5. La CPU LSI-11 corrisponde, con alcune piccole variazioni, al microprocessore multichip Western Digital MCP-1600 (introdotto nel 1975), conosciuto anche come WD-16. In quest’ultimo il control chip è denominato CP1621, il data chip (RALU) è il CP1611 e la "microm" è il CP1631. Questi microprocessori NMOS, funzionanti a 3,3 MHz, sono CPU a 8 bit che possono essere microprogrammati per emulare una CPU a 16 bit (anche nota come MP-1600).

Scheda DEC M7264 (esemplare del 1977), con CPU LSI-11 e 8 KB di RAM, da un PDP-11/03.

Vedi: http://www.antiquetech.com/chips/CP1600.htm.

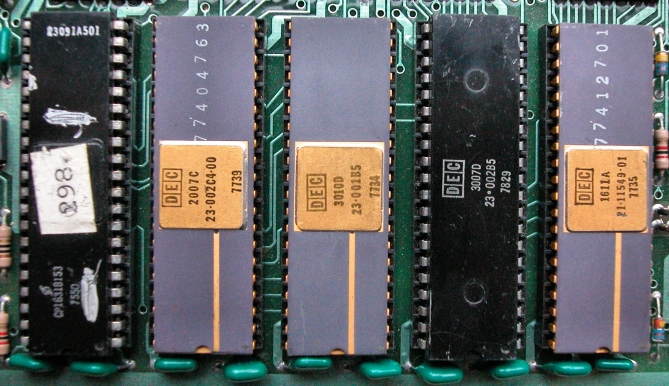

CPU WDC MCP-1600 su scheda DEC M7264 (esemplare del 1977). "MCP-1600" è il nome originario, dato da Western Digital che lo fabbricava, al chipset corrispondente al DEC LSI-11 (vedi sopra). Architetturalmente è una CPU a 8 bit che può essere micro-programmata per eseguire istruzioni a 16 bit; si tratta, in sostanza, di una versione ridotta della microarchitettura DEC PDP-11. L'MCP-1600 è un microprocessore multi-chip, NMOS a 3,3 MHz, composto da cinque integrati: la RALU (Register-ALU) CP1611 (DEC 21-11549-0x), il Data Chip (CU) CP1621 o DEC 21-001C3-0x, le due ROM (Microms, cioè Micro ROM) contenenti il set di istruzioni PDP-11 CP1631-10 (Part I, DEC 23-001B5) e CP1631-07 (Part II, DEC 23-002B5) e la ROM opzionale con le istruzioni PDP-11 "estese" ed il supporto per le istruzioni in virgola mobile, CP1631-15 (DEC 23-003B5 o 23-091A5-01). Nell'originaria implementazione Western Digital (l'MCP-1600 è stato il primo microprocessore prodotto da questa Casa) era formato da 3 chip: CP1611, CP1621 e CP1631. La RALU 1611 contiene 26 registri a 8 bit. Questo processore esiste nella versione a 8 bit (MCP-1600) ed in quella con le Microms contenenti istruzioni a 16 bit, anche nota come MP-1600; esso venne commercializzato da Western Digital con la sigla WD-16. Oltre che dalla DEC, è stato utilizzato in molti controller di processo ed in alcuni microcomputer come l'AM100 di Alpha Micro Systems ed il Pascal MicroEngine 9000 della stessa Western Digital (vedi: http://www.antiquetech.com/chips/CP1600.htm).

Vedi: http://www.cpushack.com/CPU/cpu2.html; http://processortimeline.info/.

Scheda Qbus DEC M7270 (KD11-H) con CPU LSI-11/2 per minicomputer PDP 11/03 (1980) - Uno dei più classici processori Digital. Evoluzione dell’altrettanto noto LSI-11 originale (1975, su scheda M7264), prima implementazione dell’architettura PDP come microprocessore, l’11/2 ha avuto notevole successo nel settore OEM (vedi Heathkit/Zenith Data Systems). Rispetto al predecessore manca della RAM "a bordo". Entrambi mettono a disposizione dell’utente le 83 istruzioni PDP standard, con 8 istruzioni EIS/FIS aggiuntive (laddove, come in questo caso, sia installata l’opzione KEV11), un singolo livello di interrupt, una capacità d’indirizzamento di memoria di 32 kWord ed il supporto per il debugging (MicroODT).

Il chipset dell’LSI-11, fabbricato originariamente da

Western Digital e da quest’ultima commercializzato col nome "WD16"

(o MCP-1600),

è formato da 4 circuiti integrati MOS di base più un quinto opzionale. L'LSI-11/2 ricalca la medesima architettura ed è in effetti una CPU LSI-11

funzionante ad una maggior frequenza di clock. I chip che la compongono sono l’unità di controllo

23-003C4 (WD1621, 23-002C4 nell'LSI-11), il data path 21-15579, all'estrema

sinistra (WD1611, 21-11549 nell'LSI-11) e due memorie ROM col microcodice o

"MICROM" (23-002B5 e 23-001B5,

WD1631). Il quinto chip, quello più a destra nella foto sopra, è l’opzione

KEV11 (23-003B5); il suo socket può tuttavia fungere anche da connessione per

una scheda Qbus aggiuntiva, la KUV11-AA WCS (Writable Control Store) che

consente la personalizzazione del microcodice. Complessivamente la CPU LSI-11/2

contiene 23.000 transistor, di cui 10mila nella ROM del microcodice; è

fabbricata con processo NMOS a 7 micrometri e funziona a 3,3 MHz. Questo

processore, nonostante la sua proverbiale lentezza, è stato uno dei maggiori

successi commerciali della DEC, soprattutto nel campo industriale e del

controllo di processo. Come

conseguenza delle difficoltà finanziarie di Western Digital alla fine degli

anni Settanta, DEC divenne essa stessa un fabbricante di microprocessori per

poter far fronte alla notevole e costante domanda del mercato.

Un'altra versione della scheda DEC M7270 con CPU LSI-11/2.

Vista ravvicinata del processore LSI-11/2. Questo esemplare contiene chip sia DEC che Western Digital (a sinistra, il CP16318153, o CP1631) prodotti in anni diversi (1975, 1977, 1978).

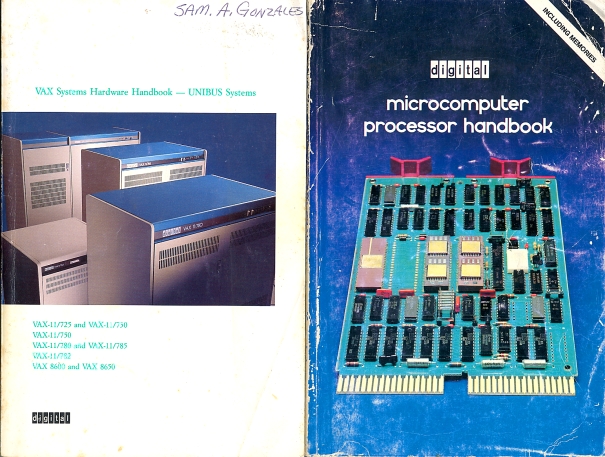

Due manuali Digital che si occupano dei sistemi basati sulle CPU LSI-11 ed LSI-11/2 (a destra, 1980) e dei VAX UNIBUS (a sinistra, 1988). Unibus (scritto talvolta tutto in lettere maiuscole, UNIBUS) è stato il primo bus standard impiegato nei PDP-11 e nei VAX. E' un bus asincrono a 72 linee, di cui 56 di segnale, con indirizzi a 18 bit (che consentono un indirizzamento diretto di 256 KB). Vedi: http://en.wikipedia.org/wiki/Unibus.

Il CP1600 (1976, qui su scheda American Totalisator Co. Inc., 1977) era un microprocessore nMOS a 16 bit sviluppato congiuntamente da General Instrument (GI, talvolta erroneamente scritto "General Instruments") e Honeywell, derivato dall'architettura di sistema del DEC PDP-11 di cui ricalcava molti aspetti (ad esempio il set di istruzioni, l'I/O memory mapped e l'impiego di registri "general purpose"). Strutturalmente è simile al Western Digital MCP-1600 (WD16) ed anche al MicroNOVA di Data General. E' stato utilizzato soprattutto in piccoli computer di processo e, nella versione ridotta CP1610, nella console per videogiochi Mattel Intellivision (vedi). (American Totalisator è stata per anni una divisione di General Instrument.)

Vedi: http://www.nyx.net/~lturner/public_html/CP1600.html; http://www.classiccmp.org/pipermail/cctech/2007-June/081560.html.

Anche (su GI): http://www.nndb.com/company/496/000059319/, http://www.vintagecalculators.com/html/general_instrument.html.

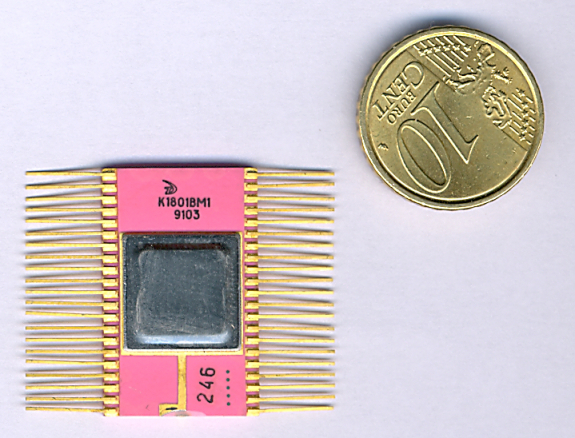

CPU Angstrem K1801VM1 (1980, l'esemplare è del 1991). Questo microprocessore nMOS (5 MHz) a 16 bit fabbricato nell'ex-URSS era basato sull'architettura del PDP-11 e, in particolare, su quella del PDP-11/23 che riproduceva in maniera fedele (pur non essendo considerato un vero e proprio clone delle CPU Digital). Le CPU della serie 1801, introdotte in URSS nel 1980, si basavano su un core (nucleo) a 16 bit ispirato al DEC LSI-11 ed in parte derivato da esso tramite reverse-engineering. Alla fine degli anni Settanta, infatti, il Ministero dell'Industria Elettronica (dal quale dipendevano in Unione Sovietica tutti i fabbricanti di circuiti integrati) aveva deciso di privilegiare la "clonazione" dei microprocessori "occidentali", in particolare dell'LSI-11 che godeva di grande considerazione in URSS, rispetto allo sviluppo di architetture proprie, pensando che in questo modo sarebbe stato più facile e rapido colmare il divario tecnologico con gli Stati Uniti. Durante gli anni Ottanta le CPU 1801 divennero i più popolari microprocessori sovietici e furono utilizzati in una quantità di applicazioni diverse, dagli home computer ai controller di processo alle applicazioni militari. La loro diffusione contribuì alla grande popolarità che l'architettura DEC PDP tuttora ha nei Paesi dell'Est europeo. Che i propri microprocessori fossero oggetto di clonazione nell'Unione Sovietica era poi un fatto ben noto agli ingegneri DEC, che addirittura si premurarono di inserire, nel layout del CVAX, un "avviso" scherzoso in caratteri cirillici (CVAX: when You care enough to steal the very best, vedi: http://micro.magnet.fsu.edu/creatures/pages/russians.html).

"The history of this CPU stems back from the early to mid-70'es, when the group of engineers in Zelenograd's Special Computing Center, led by D.I. Yuditsky, developed their first 16-bit minicomputer, called Elektronika NC-1. This machine, intended to directly compete with SM EVM series, was first released in 1973 and used the in-house developed sectioned 4-bit 587 CPU, sometimes called the first Soviet microprocessor ever. Its descendants proved popular and were widely used in various control systems and telecom equipment. However, sectioned nature of their CPUs made these machines somewhat unwieldy, especially in military applications, and the need for a single-crystal microprocessor was identified. In 1980 the first 1801 CPU intended to fill this niche, K1801VE1, entered production. It was essentially a microcontroller with 256 bytes of on-chip RAM, 2K ROM and other peripheral circuitry, still based on Elektronika NC instruction set, but compatible with a Soviet clone of DEC's Q-Bus that was already adopted as an industry standard, a first sign of the things to come. Its peripheral circuits were underutilized by the industry, as it was mostly used as a general-purpose CPU, rather than a microcontroller, so it was decided to simplify the chip, removing unnecessary devices from the die. But by that time its parent organization, the SCC, has already lost in powergames that plagued Soviet industry. By its nature, Soviet industry was an extremely bureaucratic structure, so decision making process was often driven not by technical or economical considerations, but by the results of the games of influence between various organisations and officials. SCC, even despite its technical successes and popularity of its designs, was not without its opponents and even enemies. While its staff had an aversion to copying and reverse engineering Western technology, many groups within the Ministry of Electronic Industry argued for it as a quicker and more secure way to meet the needs. These groups eventually prevailed, and in 1976 the SCC was essentially disbanded, its technical base passing to the Angstrem plant while some of its research labs were joined into Research Institute of Precise Technics (which didn't really need them), and other forming a research arm of the newly formed NPO Scientific Center. This sudden reorganisation resulted in the abandonment of the Elektronika NC architecture (it continued only in CNCs based on an NC-1 machine, some of which are used up to this day) and adoption of the PDP-11 compatibility as a MEI standard, a process sometimes called PDP revolt in Russian literature. Thus, the microcode for the new simplified CPU was redesigned and made compatible with LSI-11 instruction set. New processor was released in 1982, designated K1801VM1. It was supplemented by the 600-gate KR1801VP1 ULA, which was used to implement various support circuitry, 64 Kib KR1801RE2 ROM chip, and 64 Kib K573RF3 EPROM. Together they constituted the first widely used generation of 1801 family."

Vedi: http://www.cpu-ukraine.com/article/7.html; http://www.cpucollection.ca/Russian_and_ussr.htm.

Anche: http://www.chipdb.org/img-angstrem-k1801vm1-k1801bm1-6350.htm.

Anche: http://en.wikipedia.org/wiki/1801_series_CPU; http://www.cpushack.com/category/cpu-of-the-day/.

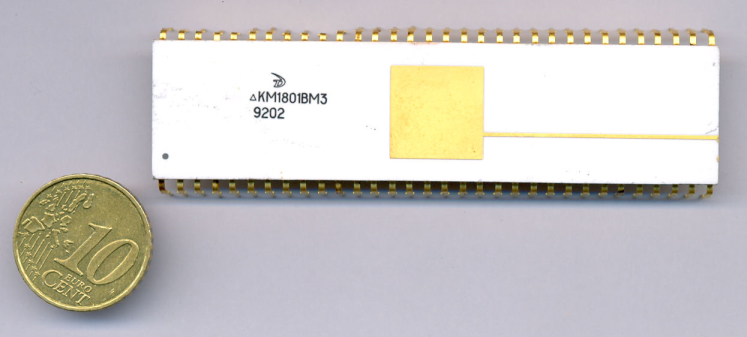

Il KM1801VM3 era un microprocessore nMOS a 16 bit basato sull'architettura PDP-11 e fabbricato nell'ex-URSS tra la metà degli anni Ottanta e l'inizio degli anni Novanta. Può essere considerato una versione dual-chip (questa è la CPU, cui si può affiancare una FPU "VM4" opzionale) del PDP-11/34. La notevole diffusione in ambito industriale e scientifico dei minicomputer DEC ispirò nell'Unione Sovietica la creazione di diversi "cloni" delle rispettive CPU. La versione raffigurata qui, in package CERDIP a 64 pin, funziona a 5 MHz e può indirizzare direttamente fino a 4 MB di RAM (vedi: http://www.cpu-museum.com/Eastern_e.htm). Questo microprocessore non ha niente a che vedere con l'RCA COSMAC 1801, col quale condivide solamente la sigla numerica; è fabbricato dalla Angstrem (vedi: http://www.angstrem.ru).

Vedi: http://www.inp.nsk.su/~kozak/adv/advh2.htm; http://www.cpu-world.com/forum/viewtopic.php?p=24745.

Sulla Angstrem: http://smithsonianchips.si.edu/ice/cd/PROF96/ROW.PDF.

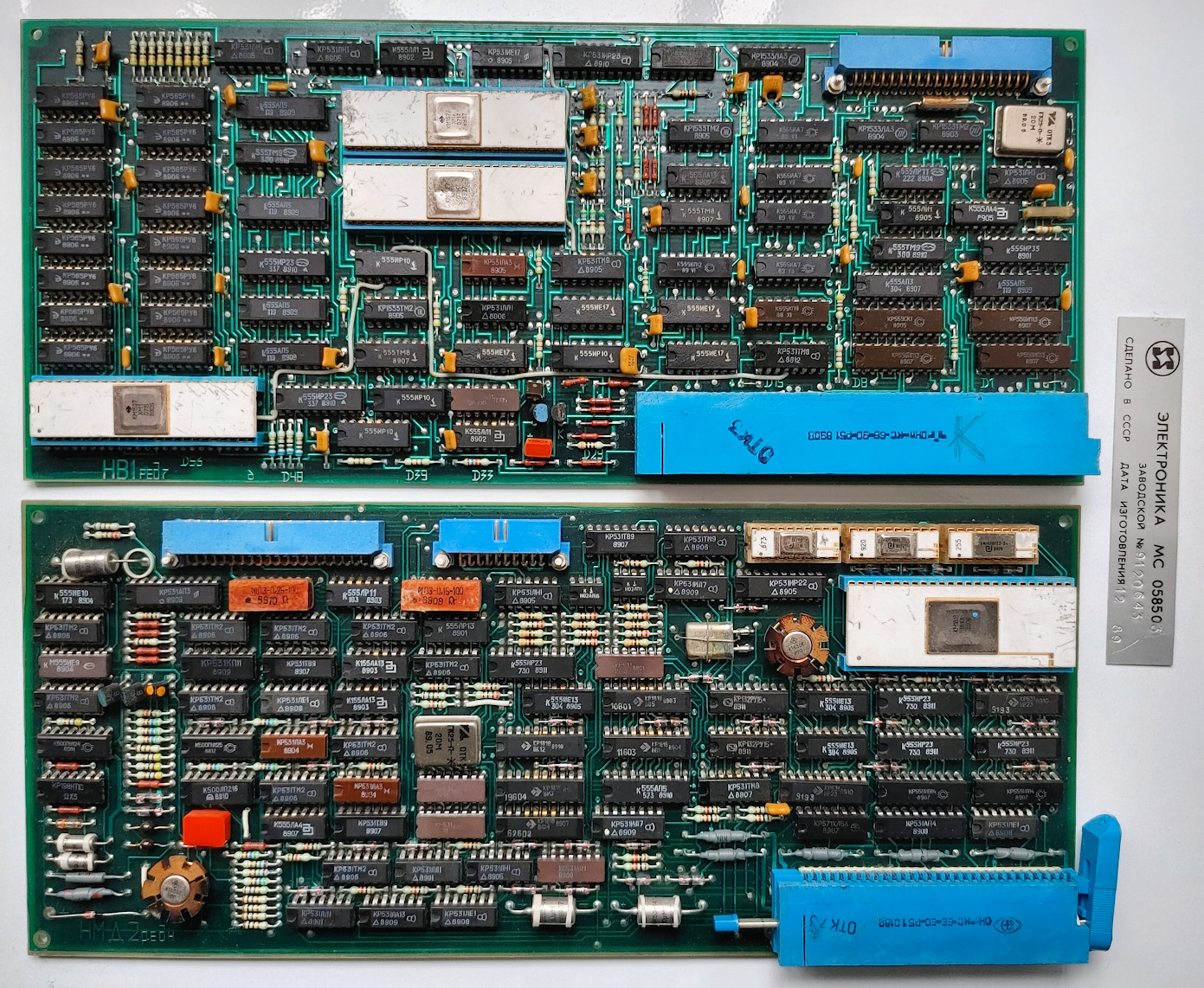

Processore KM1801VM2 a 16 bit sulla scheda CPU (in formato Unibus-compatibile, con 64 KB di RAM a bordo) di un microcomputer sovietico Elektronika DVK-3M2 (in Russo ДВК, Диалоговый вычислительный комплекс, che significa Dialogue Computing Complex) compatibile con l'architettura DEC PDP-11. Il DVK è anche noto come MS-0501.

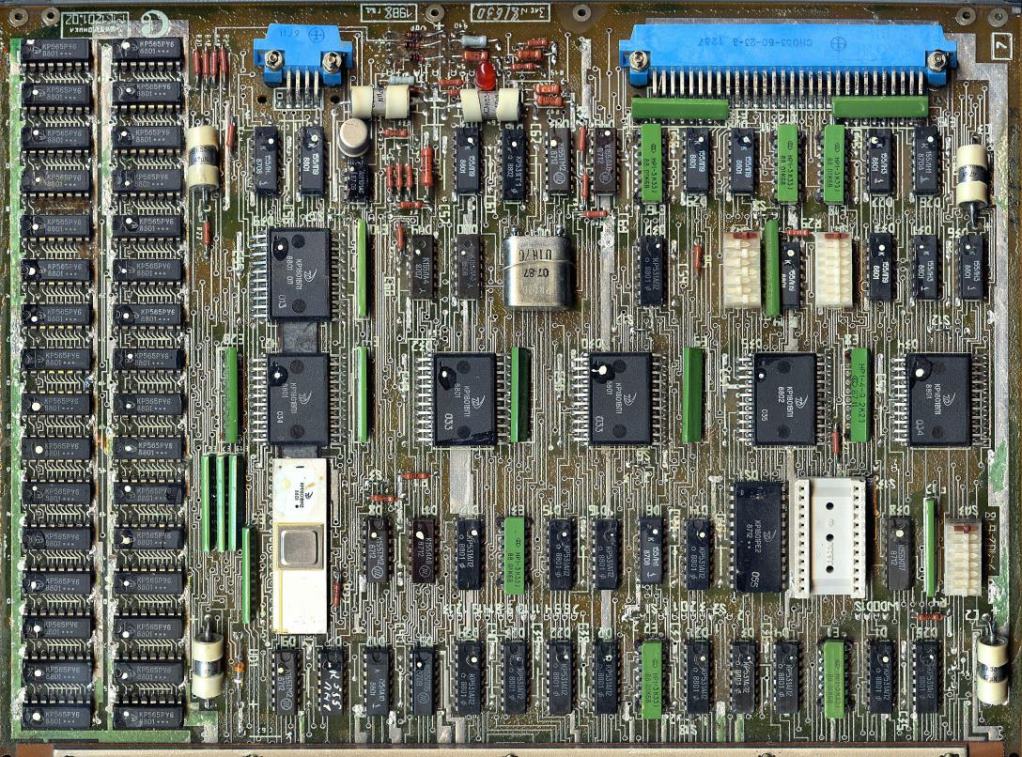

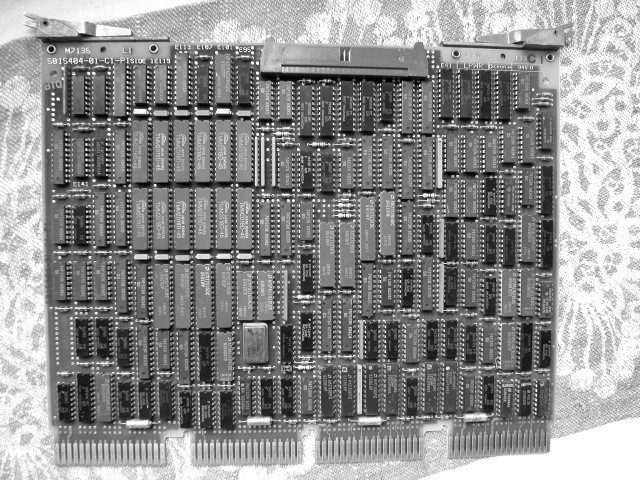

Scheda Unibus di fabbricazione sovietica, 1989, con microprocessore KM1801VM3, 256 KB di RAM e vari chip di supporto, tra cui alcuni gate array (ULA) KR1801VP1 da 600 gate utili. Questa scheda è in sostanza un clone della CPU del PDP-11/23 ed è stata usata in alcuni modelli di mini- e microcomputer prodotti nell'ex URSS appartenenti alla variegata famiglia Elektronika, in particolare nell'Elektronika DVK-3M e nel DVK-4, o Kvant 4C (il DVK-3 è a sua volta un clone, con alcune estensioni, del SM EVM, una macchina con architettura PDP-11 molto diffusa nei Paesi dell'Est). Com'è noto, in Unione Sovietica vennero clonate, principalmente mediante reverse engineering, alcune diffuse architetture di minicomputer "occidentali", in particolare la PDP-11 della DEC e l'HP 3000. Nel caso del PDP-11 è stata riprodotta l'intera architettura di sistema basata su Unibus, creando una serie di schede compatibili con le controparti statunitensi.

Vedi: http://www.leningrad.su/museum/show_calc.php?n=241; http://www.leningrad.su/museum/show_calc.php?n=242.

Dettaglio della scheda visibile sopra, con l'indicazione del modello, dell'anno di produzione e del paese di provenienza (a sinistra).

FPU VM4 (BM = VM in caratteri cirillici) per il microprocessore KM1801 raffigurato sopra, 1989.

Vedi: http://cpu-ukraine.com/?module=collection&item=44&page=4 (lo indica come un Engineering Sample).

FPU per PDP 11/44 (1979) - Il PDP 11/44 è una macchina Unibus estensione del fortunato PDP 11/34 che include nella dotazione di base una memoria cache, una FPU in standard IEEE 754 e la possibilità di espandere la RAM di sistema fino a 4 MB. L’unità in virgola mobile (FPU) FPP-11F è realizzata con bitslice AMD Am2901.

Classificazione dei sistemi VAX

Tutte le macchine VAX possono essere fatte rientrare in una delle seguenti quattro categorie (vedi).

Macchine con bus SBI

A questa categoria appartengono i cosiddetti "Big Four": il VAX 11/780 (Star), il VAX 11/750 (Comet), l’11/730 (Nebula) e il VAX 8600 (Venus) il cui nome può trarre in inganno (avrebbe dovuto più propriamente chiamarsi VAX 11/790). Tutte queste macchine, non SMP, sono basate sul bus SBI ovvero su bus da esso direttamente derivati. All’SBI si connettono gli appositi adattatori per MASSBUS, UNIBUS, CI e così via.

Macchine con bus BI/XMI

A questa categoria appartengono tutti i VAX realizzati attorno ad un bus VAXBI o XMI, singolo oppure multiplo, al quale si connettono adattatori di periferica ovvero adattatori per altri bus (UNIBUS, CI ecc.). Le macchine di questa famiglia sono pensate come sistemi SMP (anche se possono funzionare con una singola CPU). Tutti i VAX della serie 8000, con l’eccezione dell’8600, sono macchine BI. I VAX della serie 6000 ed il VAX 9000 sono invece macchine XMI.

Macchine ibride VAX/Alpha

A questa categoria appartengono i VAX 7000/10000, che utilizzano il bus di sistema LSB. Quest’ultimo non è stato progettato come bus per VAX bensì come bus per i processori Alpha; per questa ragione le macchine 7000/10000 fanno uso di adattatori XMI e di schede CPU (come ad es. la KA7AA) che impiegano particolari soluzioni hardware per poter connettere un processore VAX al bus LSB.

Macchine MicroVAX

Generalmente si considerano appartenenti a questa quarta famiglia tutti i sistemi VAX più piccoli dell’8200 e del 6000.

Cronologia delle macchine VAX

1975 Annuncio delle specifiche dell’architettura VAX.

1978 Introduzione del VAX 11/780, considerato il primo calcolatore commerciale a raggiungere la velocità di 1 MIPS. L’11/780 è utilizzato come termine di paragone per definire la potenza di calcolo dei VAX, che nel suo caso è convenzionalmente fissata a 1 VUP. Supporta un massimo di 4 MB di RAM.

1980 Introduzione del VAX 11/750 (0,6 VUP)

1982 Introduzione del VAX 11/782 (1,8 VUP), versione a doppia CPU dell’11/780.

1982 Viene presentato il VAX 11/730 (0,3 VUP), primo VAX ad implementare "di serie" tutte le istruzioni ed i tipi di dati floating-point indicati nelle specifiche dell’architettura.

1984 VAX 11/785 (1,5 VUP), rivisitazione migliorata del VAX 11/780.

1984 VAX 11/725 (0,3 VUP), versione più compatta del VAX 11/730.

1984 Introduzione del processore MicroVAX I.

1984 Introduzione del VAX 8600 (4 VUP).

1985 VAX 8650 (7 VUP), versione potenziata dell’8600.

1985 Introduzione del MicroVAX II (0,9 VUP).

1986 VAX 8200 (1,2 VUP), CPU V-11: primo VAX ad abbandonare la compatibilità col PDP-11.

1986 VAX 8300 (1,3 VUP), CPU V-11: versione migliorata dell’8200.

1986 VAX 8800 (12 VUP): macchina SMP ad elevate prestazioni.

1986 VAX 8700/8500 (6 VUP): versione a singola CPU dell’8800.

1987 Introduzione della prima workstation con architettura VAX, la VAXstation 2000 (0,9 VUP).

1987 MicroVAX 3500/3600: primo VAX ad utilizzare il processore CVAX (2,7 VUP).

1988 Introduzione del VAX 6200, uno dei maggiori successi commerciali di DEC.

1989 Introduzione del VAX 9000, sistema SMP ad alte prestazioni molto costoso e di scarso successo.

1990 Introduzione della serie VAX 4000 (5-45 VUP), CPU Rigel, Mariah ed NVAX, che si impone come famiglia di minicomputer dal grande successo commerciale.

1990 VAX 6000 (72 VUP), primo VAX ad utilizzare il chip Mariah e successivamente l’NVAX.

1991 Introduzione dei VAX 7000/10000, ibridi VAX/Alpha basati sul bus LSB e CPU NVAX+ e NVAX++.

1997 Fine dello sviluppo da parte di Digital dei sistemi VAX.

Scheda (M7465) della CPU di un VAX 11/780 "Star" (1977, questo esemplare è del 1980). L'11/780, presentato nell'Ottobre 1977, è stato il primo membro della famiglia DEC VAX. E' interamente realizzato con integrati logici TTL a bassa e media scala di integrazione; il clock della CPU (nota con la sigla KA780) ha una frequenza di 5 MHz (200 ns). La RAM, interamente basata su circuiti MOS, poteva essere ampia fino ad un massimo di 16 MB (512 MB era invece il limite teorico), valore molto elevato per l'epoca; era altresì presente una piccola cache ampia 2 Kword. L'11/780 impiega il bus di sistema SBI (Synchronous Backplane Interconnect) e, per l'I/O, i bus Unibus e Massbus. Questa macchina è diventata - e tale è rimasta per molti anni - il punto di riferimento per la valutazione delle prestazioni dei minicomputer, DEC e non solo. Convenzionalmente, in benchmark quali SpecMark-89, SpecInt92 e SpecFP92 si considera la velocità del VAX 11/780 pari a 1 MIPS.

Vedi: http://www.old-computers.com/history/detail.asp?n=20&t=3.

Anche: http://research.microsoft.com/en-us/um/people/gbell/Digital/timeline/1977-3.htm.

Anche: http://www.compaq.com/alphaserver/vax/timeline/1975.html.

Anche: http://www.corestore.org/vax780.htm.

Anche: http://www.flickr.com/photos/astio/3110723303/ (installazione completa di un VAX 11/780).

Vedi: http://www.tomshardware.com/picturestory/508-20-mainframe-computer-history.html.

Una delle schede che compongono l'unità in virgola mobile DEC FP780. Questa in particolare è la scheda M8289 FP Accelerator Controller. E' basata su logica TTL a bassa e media scala di integrazione, tra cui ALU a 4 bit 74181. L'FP780 era un'opzione per i sistemi VAX 11/780 che permetteva di velocizzare di parecchie volte l'esecuzione delle operazioni in virgola mobile (standard IEEE 754).

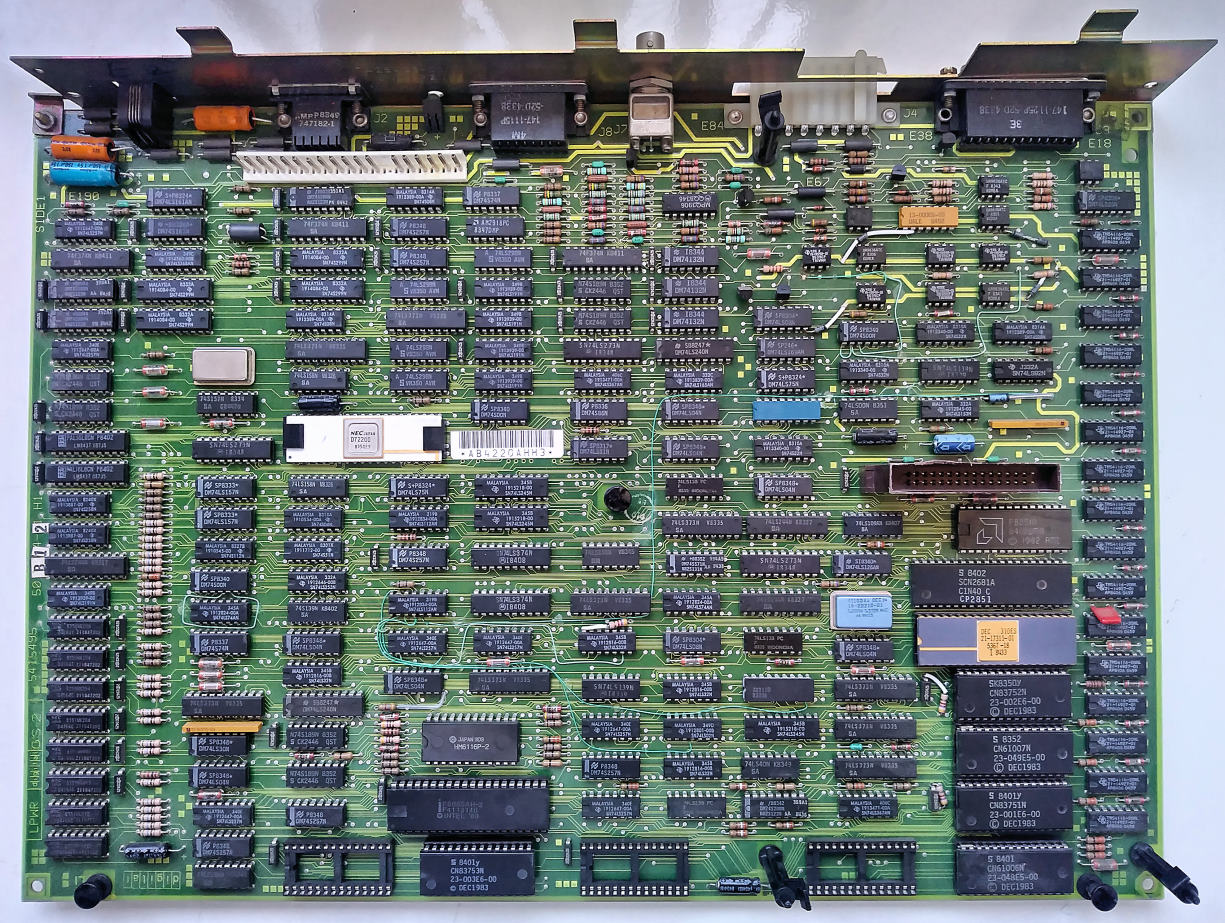

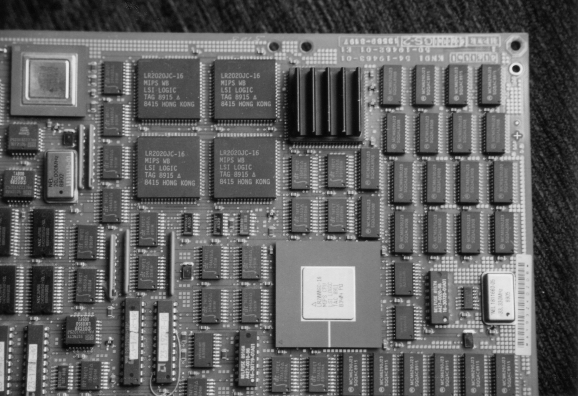

Scheda Unibus parte della CPU del DEC VAX 11/750 "Comet" (1980) - Questa è precisamente la scheda "L0002 DPM" (Data Path Module) che contiene l’ALU a 32 bit, i registri d’uso generale, il microsequencer, lo stack, la logica di decodifica delle istruzioni ma non il microprogramma, che in queste macchine era aggiornabile ed installato su una diversa scheda. L’11/750 (1980) fu il secondo membro della famiglia VAX dopo l’11/780; leggermente più lento di quest’ultimo, aveva però nei suoi confronti l’enorme vantaggio della compattezza, dal momento che si trattava del primo minicomputer a 32 bit reali realizzato con circuiti LSI (precisamente dei gate array TTL, corrispondenti nell’immagine in alto ai rettangoli di colore chiaro, che sono dissipatori di calore). La moneta da 1 Euro in basso dà un’idea delle dimensioni. Vedi: http://en.wikipedia.org/wiki/VAX-11#VAX-11.2F730.

Vedi: http://en.wikipedia.org/wiki/VAX (articolo generico sulla famiglia VAX)

The VAX History: http://www.webmythology.com/VAXhistory.htm.

Descrizione della macchina: http://research.microsoft.com/~gbell/Digital/timeline/1980-4.htm.

Un interessante sito dedicato all’11/750: http://home.iae.nl/users/pb0aia/vax/index.html.

Ottimo sito per chi si interessa alle macchine VAX: http://ed-thelen.org/comp-hist/VAX-11-750.html.

The VAX 11/750 FAQ: http://home.claranet.nl/users/pb0aia/vax/750faq.html.

VAX Maintenance Handbook: http://vt100.net/manx/details/1,2827.

Interessante collezione di sistemi DEC: http://www.rdrop.com/~jimw/jcgm-min.shtml.

Un sito curato e con molte immagini sull’11/750: http://www.computer-refuge.org/compcollect/dec/vax/11750/index.html.

La pagina del Retronomicon dedicata alle macchine DEC: http://retrocomputing.c3po.it/Retronomicon/html/dec.htm.

Storia dei VAX: http://williambader.com/museum/vax/vaxhistory.html.

The VAX Hardware Reference: http://www.netbsd.org/docs/Hardware/Machines/DEC/vax/vax700.html.

Riassunto dell’evoluzione dei VAX: http://www.beagle-ears.com/lars/engineer/comphist/vax.htm.

Scheda Floating Point Processor (FP750) per VAX 11/750. E' realizzata con la medesima tecnologia gate array TTL della CPU (immagine precedente). Introdotta nel 1981, l'opzione FP750 offriva prestazioni pari a circa il 60% di quelle dell'unità floating point FP780. Era costituita da un'unica scheda, quella visibile qui, e poteva eseguire calcoli in virgola mobile a singola e doppia precisione secondo lo standard IEEE 754. Il microcodice è contenuto nelle 10 ROM visibili nella parte destra della scheda, che costava (nel 1981) circa 8.500 Dollari (vedi questo articolo di Computerworld).

Controller di memoria (scheda L0016) proveniente dalla CPU di un VAX 11/750.

FPU di un VAX 11/730 "Nebula" (1982) - L’11/730, chiamato "miniVAX", era il membro più compatto della prima generazione di macchine VAX nonché il primo VAX interamente contenuto in un singolo armadio (cabinet). La CPU a 32 bit era basata su un’implementazione bitslice con AMD Am2901 (vedi sotto). Questa scheda è una FPU ad 80 bit (64 per la mantissa e 16 per l’esponente) realizzata con una serie di 20 ALU Am2901 da 4 bit ciascuna. Benché relativamente lento (0,3 VUPS) all’inizio degli anni Ottanta l’11/730 appariva come un piccolo miracolo tecnologico, dal momento che racchiudeva un sistema VMS multiutente completo in sole tre schede. In Italia conobbe una certa diffusione nelle aziende di medie dimensioni, nelle Università ed in diverse banche. Questa scheda proviene da un 11/730 installato presso il CED della BNL e demolito nel 1998.

L'architettura (ISA, Instruction Set Architecture) a 32 bit VAX, introdotta nel 1977 col VAX 11/780, è diventata col passare degli anni il modello ed il termine di paragone delle macchine CISC. Essa venne progettata allo scopo di estendere, e nello stesso tempo sostituire, le varie ISA dei minicomputer PDP ed in particolare quella del PDP-11. Le sue due caratteristiche principali sono la memoria virtuale (da cui la sigla VAX, Virtual Address eXtension) e l'ortogonalità del set di istruzioni (il che significa che ogni istruzione può impiegare uno qualsiasi dei modi di indirizzamento della memoria su qualunque tipo di dati). Come si può vedere in questa pagina l'architettura VAX è stata implementata in molte diverse forme e tecnologie (TTL, ECL, CMOS), prima come CPU formate da elementi a bassa e media scala di integrazione e successivamente come gate array e microprocessori VLSI (MicroVAX e derivati). Ogni versione successiva ha mantenuto la compatibilità software con quelle precedenti, garantendo in tal modo agli utenti la possibilità di continuare ad usare, su macchine più potenti, i programmi esistenti. Lo sviluppo dell'architettura VAX è cessato nel 1989 quando Digital ha introdotto i primi modelli di workstation RISC basati su CPU MIPS; la commercializzazione (da parte di Compaq, che nel frattempo aveva rilevato la DEC) delle macchine VAX è cessata alla fine del 2000.

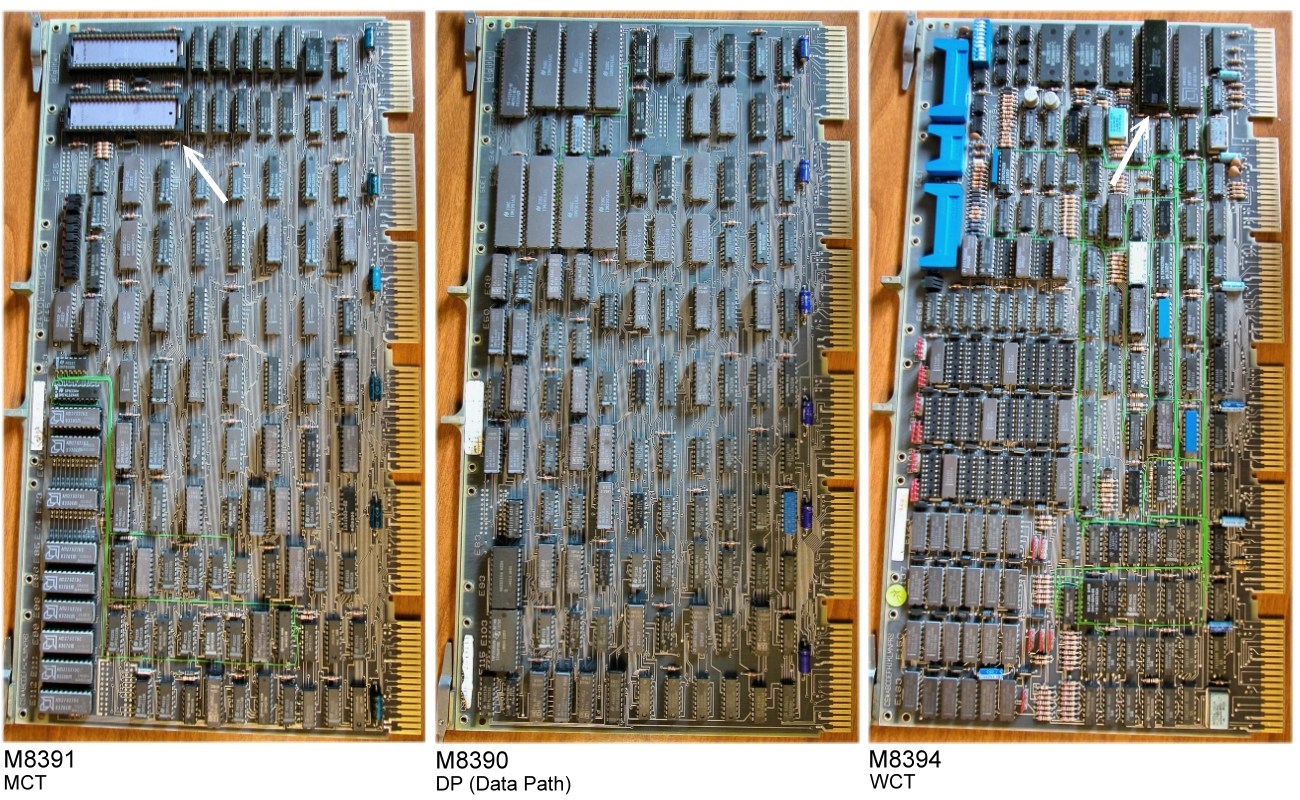

DEC M8390, Data Path (ALU) dei VAX 11/725 ed 11/730 (1982) - L’ALU (unità aritmetico/logica) è realizzata con bitslice 2901 fabbricati dalla second source National Semiconductor.

"Foto di gruppo" per le 3 schede che compongono la CPU KA730, utilizzata nel VAX 11/730: M8390, M8391, M8394. I principali componenti funzionali sono la CPU vera e propria (Data Path) con il relativo microcontroller/microsequencer, la logica di controllo della memoria e del bus di sistema (UNIBUS) e il microprocessore (un Intel 8085) che gestisce la console. Qui di seguito riporto la descrizione tratta dal manuale DEC (VAX 11/730 Central Processing Unit Technical Description), disponibile ad esempio in questo sito: http://bitsavers.trailing-edge.com/pdf/dec/vax/730/:

Uno schema funzionale della CPU è riportato nel medesimo manuale:

Il VAX 11/730 era un modello entry-level, precisamente il più piccolo dei VAX UNIBUS (le dimensioni fisiche corrispondono a quelle del PDP 11/44). Anche se affidabile e poco costosa se paragonata ai suoi "fratelli maggiori", questa macchina era nota soprattutto per la sua proverbiale lentezza: le sue prestazioni erano solo di poco superiori a quelle del MicroVAX I (occorrevano ad esempio circa 15 minuti per eseguire un boot a freddo con il sistema operativo VMS 5.1). La maggior parte dei VAX 11/730 vennero venduti in configurazione minima, con la sola CPU comprensiva del controller di dischi RB730, un'unità a dischi rimovibili RL02 da 10 MB, un'unità a nastro TU80 ed un'eventuale unità a disco rigido Winchester RA80 da 120 MB.

Prima CPU VAX realizzata con circuiti ECL - First ECL-based (gate array) VAX CPU

Una delle schede della CPU (KA86) del VAX 8600 "Venus" (1984) - Il VAX 8600 (vedi) era una macchina server ad alte prestazioni (circa 4 volte più veloce del VAX 11/780) la cui CPU utilizzava gate array in tecnologia ECL bipolare, fabbricata col processo a 3 micron MOSAIC-I, prima realizzazione di questo genere in ambito DEC (seguiranno gli 8800/8700 ed il 9000). L’8600 condivideva con i fortunati predecessori 11/780 ed 11/785 il particolare bus di sistema chiamato SBI (Synchronous Backplane Interconnect). Il VAX 8600 è stata fra l’altro il primo sistema VAX ad utilizzare la tecnica del macropipelining. Qui è raffigurato il Cache Memory Controller (MMC) L2030. Vedi: http://en.wikipedia.org/wiki/VAX_8000.

Vedi: http://h18002.www1.hp.com/alphaserver/vax/archive/vax8600.html; http://www.computerhistory.org/collections/accession/102626798.

Vedi: http://ifctfvax.harhan.org/Quasijarus/vaxhw/overview.html; http://pdp-11.ru/simh_trailing-edge_com/vax.html.

Anche: http://query.nytimes.com/gst/fullpage.html?res=9803EFDF1339F932A35752C1A962948260.

Copertina del Digital Technical Journal (DTJ) dedicato al VAX 8600. I circuiti integrati (gate array ECL) sono qui in package CLCC, mentre la maggior parte dei sistemi 8600 commercializzati contiene integrati in package PGA.

Scheda della CPU di un VAX 8700 (1984) - La CPU del VAX 8700 "Nautilus" (così come quella del più grande 8800, SMP) è basata su macrocell in tecnologia LSI ECL da circa 1.200 porte logiche ciascuno con un cycle time di 45 ns. L’architettura dell’8700 impiega una pipeline a 5 stadi ed un doppio bus: una connessione ad alta velocità tra processore e memoria detta NMI bus ed il bus VAXBI per la connessione con le periferiche. L’8700 è dotato di 64 KB di cache e può avere un massimo di 128 MB di RAM ECC. Le CPU vera e propria è formata da 8 schede connesse al backplane bus tramite connettori ZIF. Una completa descrizione tecnica della macchina si trova nel numero 4, Febbraio 1987, del Digital Technical Journal, disponibile in formato PDF a questo indirizzo: http://maben.homeip.net/static/S100/DEC/magazine/index.html. La scheda raffigurata qui è il Microsequencer F1008.

Controller di memoria (scheda F1021) di un VAX 8500 "Flounder" (1985), con gate-array ECL fabbricati da Motorola (uno dei dissipatori di calore è mancante). L'8500 era una versione ridotta, più economica ma anche più lenta, del VAX 8550. Il "rallentamento" era ottenuto a livello di microcodice con l'inserimento di istruzioni "inutili" (NOP) anziché riducendo il clock della CPU (vedi ad es.: http://nixforums.org/about128808-asc-45.html).

Numero di Febbraio 1987 della pubblicazione Digital Technical Journal, che tratta dell'architettura dei calcolatori VAX della "Serie 8000".

Scheda F1002 parte della CPU di un VAX 8500. Si tratta di uno shifter a 32 bit utilizzato anche per le operazioni di moltiplicazione e divisione tra interi.

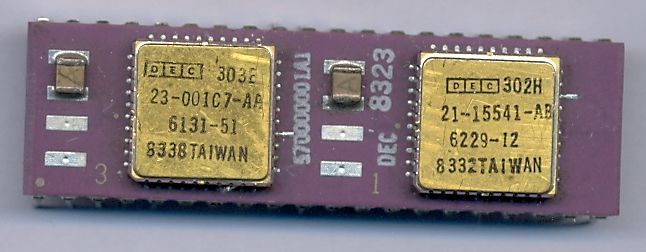

Scheda CPU (Qbus quad heigh) di un DEC PDP-11/23 Plus (1981, vedi) - Basata sul processore DCF-11 o semplicemente F-11 che si vede al centro dell’immagine. Il nome Digital è "KDF11-B"; la scheda contiene due controller per comunicazioni seriali (i chip neri a sinistra in alto, prodotti da Intersil) e le ROM per effettuare l’avvio o "boot" della macchina, a sinistra in basso. In questo elaboratore le operazioni in virgola mobile possono essere accelerate da un apposito circuito (KEF-11) che s’installa nel socket da cui, in questa foto, parte il cavo grigio che si vede nella parte alta dell’immagine e che fa a sua volta capo alla scheda FPF-11, non visibile, la quale funge da acceleratore floating point alternativo ad alte prestazioni. L’11/23, caratterizzato da un buon rapporto prezzo/prestazioni, è stato uno dei PDP più comuni in Europa, soprattutto in ambito universitario. Come il predecessore LSI-11, il processore F-11 (introdotto nel 1979) era suddiviso in tre chip, uno con funzioni di controllo (replicabile), uno contenente le unità di esecuzione vere e proprie (ALU) ed un terzo infine con la MMU. L'F-11 è stato in ordine cronologico il secondo microprocessore DEC ed il primo interamente sviluppato (a livello di progettazione logica) dalla DEC stessa. Esso implementa l'intera microarchitettura del PDP-11/34, incluse le istruzioni in virgola mobile (FP-11, che non vengono però eseguite direttamente in hardware, mancando la FPU) e la MMU (KT-11). Le istruzioni facenti parte del Commercial Instruction Set (CIS) richiedono la presenza di una ROM aggiuntiva per il relativo microcodice.

DEC F-11 chip identification

DC302: data chip (DC), 6K transistor (anche 302H)

DC303 (o 303B): control chip (CC), 23K transistor - can be replicated (up to 9 per processor)

DC304: memory management unit (MMU), 10K transistor

Questi chip erano fabbricato da AMI con processo NMOS a 6 micron. La CPU funzionava a 3,6 MHz.

Dettaglio di una CPU DEC F-11 (esemplare del 1983).

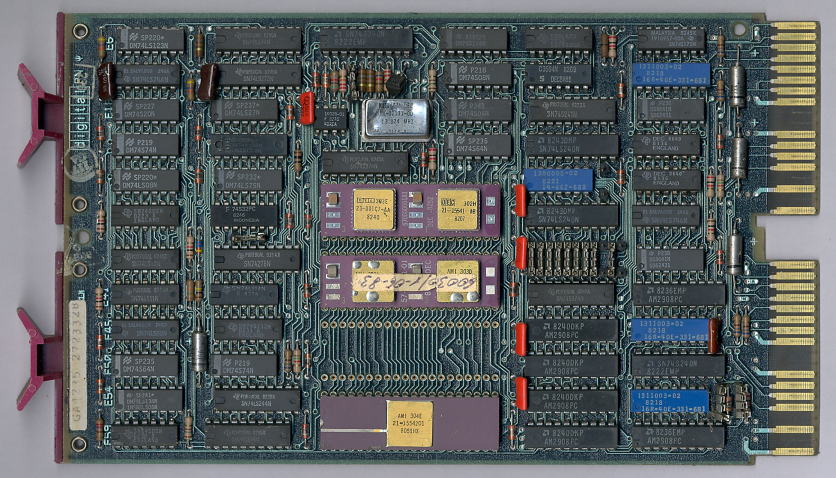

Scheda DEC M8186 (KDF11-A) con CPU F-11 (1982). Era utilizzata nei minicomputer PDP-11/23. In questo esemplare è installata l'opzione KEF11 per i calcoli in floating-point (secondo chip dall'alto) e manca l'opzione CIS. Quest'ultima impiega due socket, cosicché nel modello -A non può essere installata insieme alla KEF11, cosa invece possibile nelle schede KDF11-B che hanno 5 socket. Il primo chip in alto è la CPU DCF11 (21-15541AB Data Path + 23-001C7 Control Chip); quello più in basso è invece la MMU. A questa scheda può essere accoppiata una FPU su scheda separata, la FPF11, che richiede la presenza di una MMU aggiuntiva.

Vedi: http://decpicted.blogspot.com/2010/01/dec-m8186-1123-cpu-module-kdf11.html.

Anche: http://www.cpu-galaxy.at/Boards/Boards_CPU/Boards_CPU.htm.

Anche: http://www.cpu-collection.de/?l0=co&l1=DEC&l2=PDP-11.

Scheda CPU KDF11-A, DEC M8186, con opzione CIS (Commercial Instruction Set). Come detto sopra, quest'ultima non consente l'installazione dell'opzione floating-point KEF11 dal momento che occupa due socket, precisamente i due più in basso. L'opzione CIS consente di accelerare l'esecuzione di programmi scritti in linguaggio COBOL.

DEC M7133, scheda CPU per PDP-11/24 (1980) con processore F-11 (vedi: http://simh.trailing-edge.com/semi/f11.html), oppure anche: http://decpicted.blogspot.com/2010/01/dec-m7133-digital-pdp-1124-cpu.html.

Motherboard di un DEC Professional-350 (Pro-350). Il Pro-350 (1982 - vedi), come il "fratello minore" Pro-325 ed il più veloce Pro-380 (con processore J-11 e clock a 8 MHz), era un personal computer DEC basato sull'architettura PDP-11 ed in particolare sul microprocessore F-11. Con queste macchine, così come col DecMate basato sull'architettura del PDP-8 e col Rainbow (dotato di CPU i8088/Z80 e sistema operativo CP/M), DEC intendeva fare concorrenza al PC XT di IBM ed ai suoi numerosi "cloni", nonché alle workstation grafiche di fascia bassa. In realtà esse rappresentarono un insuccesso commerciale, causato dalla mancanza di software commerciale disponibile per questa piattaforma (in particolare nel settore business) e dalla difficoltà nell'effettuare il porting (conversione) dei programmi disponibili per MS-DOS e CP/M. I DEC Professional non ebbero dunque diffusione né come personal computer da ufficio (settore dominato dai sistemi x86) né come workstation entry-level (settore che, fino alla nascita dei primi microprocessori RISC ed all'avvento dell'Intel 80486 e del Pentium, fu dominato dai processori Motorola 68K). Il sistema operativo per i Pro-325/350 era il P/OS (Professional/Operating System) di DEC, una versione adattata del più famoso RSX-11M per PDP-11. Su queste macchine potevano "girare" anche l'RT-11 e la versione 2.9 di BSD Unix. Il DEC Professional-350 utilizza un particolare bus di espansione a 90 linee, detto CTI (Computer Terminal Interconnect). Sulla motherboard ci sono 6 connettori CTI con meccanismo ZIF (Zero-Insertion Force).

Vista ravvicinata del microprocessore DEC F-11 utilizzato nel Professional-350. E' la medesima CPU del PDP-11/23.

Descrizione dei PDP-11/23: http://www.hampage.hu/pdp-11/1123.html.

Storia del PDP-11: http://williambader.com/museum/vax/pdphistory.html.

Qualche immagine della macchina: http://www.oldcomputers.arcula.co.uk/up112.htm.

Pagina dedicata a questo sistema: http://www.employees.org/~kirk/page0204.html.

The PDP-11 Family: http://www.employees.org/~kirk/page0204.html.

Will's PDP-11/23 Information Page: http://www.fpns.net/willy/pdp11/pdp11.htm.

Documentazione tecnica sul PDP-11: http://www.dadaboom.com/pdp11/.

Pagina dedicata ai PDP-11: http://www.pdp11.co.uk/category/by-kwd/qbus/.

Pro-350: vedi http://www.vintage-computer.com/dec_pro_350.shtml; http://hkzlab.spatof.org/ALBUM/dec_pro_350/.

Anche: http://www.old-computers.com/museum/computer.asp?c=115&st=1; http://www.digitalbits.org/index.php?pid=23.

Anche: http://lordkalvan.vox.com/library/post/nablopomo---dec-professional-350.html.

Coppia di schede (in alto il controller video Hi-Res, in basso il controller dei dischi rigidi) provenienti da un Elektronika MC-085/50, clone sovietico di fine anni Ottanta (queste schede sono del 1989) del DEC Professional 350.

Questa è la scheda floating point FPF-11 (DEC M8188) collegata alla CPU mostrata sopra. Si tratta di un acceleratore hardware in virgola mobile basato sul bitslice AMD Am2901.

Vedi: http://decpicted.blogspot.com/2010/02/dec-m8188-pdp-1123-fpf-11-floating.html.

Scheda di terminale VT-240 con CPU 8085 (in basso) e DEC T-11 o DC310 a 7,5 MHz (a destra). Quest'ultimo processore, dedicato alle applicazioni embedded, rappresenta il primo microcomputer single-chip sviluppato dalla DEC. E' stato prodotto a partire dal 1992 ed impiegato, oltre che nel terminale VT-240, in alcuni modelli di controller di dischi e come processore ausiliario nell'Atari Game System 2. Si tratta di una CPU NMOS che integra circa 13.000 transistor ed ha un assorbimento di potenza molto ridotto, circa 1 Watt. Esiste in 3 diverse versioni fabbricate dalla stessa DEC, a 7,5 e 10 MHz (modelli 21-17311-01 e 21-17311-02), e da Synertek (modello 21-17311-00 a 7,5 MHz). Sulla scheda è anche presente un controller grafico NEC 7220 High Performance Display Controller (vedi).

Primo microprocessore DEC CMOS - First DEC CMOS microprocessor

CPU di un PDP-11/83, M8190 o KDJ11-B (1985). Basato sul microprocessore J-11 ("Jaws", in alto, vedi), l’11/83 era un PDP di fascia alta, che supportava soluzioni avanzate quali la memoria cache (montata su questa stessa scheda), la FPU a bordo e il sistema Private Memory Interconnect, un canale di comunicazione privilegiato ad alta velocità tra CPU e memoria. Il J-11 (1983) era essenzialmente un’implementazione in forma di microprocessore del PDP 11/70, con supporto per l’SMP e la memoria cache. L'esecuzione delle istruzioni in virgola mobile poteva essere accelerata con l'aggiunta di una FPU opzionale. Come il predecessore F-11 anche il J-11 supportava il set di istruzioni "commerciali" CIS (mediante l'aggiunta di un'apposita ROM di microcodice). Il J-11 è un microprocessore multi-chip, formato da due unità di base distinte (Control Chip e Data Chip) e da un'eventuale terza unità, la FPU (FPA, Floating-Point Accelerator).

DEC J-11 chip identification

DC334: data chip (DC), 40K transistor, Harris "D4-6900-5"

DC335: control chip (CC), 80K transistor, Harris "D4-6901-5"

DC334 + DC335 = dual-chip ceramic module DEC "DCJ11-AC 57-19400-09"

DC321: floating-point unit (FPA), 34K transistor, DEC "21-21858-08"

DC351: DMA controller gate array, LSI Logic L1A0305, "21-22800-01"

DC350/DC394: system and cache controller gate array, Toshiba TC176080AY-0001, "212420001"

I chip DC334 e DC335 erano fabbricato da Harris con processo CMOS "double poly - P-well" a 4 micron. Il chip DC321, introdotto nel 1984, era invece fabbricato direttamente da DEC con processo ZMOS (NMOS a doppia metallizzazione, 3 micron). Questo chip venne in seguito utilizzato come base per lo sviluppo delle FPU nel MicroVAX e nel processore V-11. La CPU funzionava a 3,75 MHz poi innalzati a 4,25, quindi fino a 18 (come nel caso del PDP 11/83).

Processore KDJ11-A o M8192 (1984/5). Questa scheda CPU era la versione economica della KDJ11-B raffigurata sopra, e veniva montata nei PDP-11/73 (1984). Basata sul medesimo processore J-11, mancava infatti di alcune soluzioni avanzate utilizzate invece dalla più costosa "sorella maggiore". All’epoca i PDP-11/73 ed 11/83, basati sull’impiego di componenti VLSI, erano noti come "MicroPDP". Il processore J-11 "Jaws", introdotto nel 1983, conteneva 120.000 transistor ed era suddiviso in due chip: il control chip (in alto) con funzioni di microsequencer e memoria per il microcodice e l’execution unit, contenente l’ALU, la MMU e la logica di prefetching delle istruzioni. E’ stato la prima CPU di questa famiglia ad essere realizzata con tecnologia CMOS. Gli integrati del J-11 erano fabbricati da Harris Semiconductors.

Scheda Sunburst-II (bus CAMAC) con CPU DEC J-11 e 2 MB di RAM, 1988. Il CAMAC (Computer Automated Measurement And Control) è un bus standard largamente impiegato nel controllo di processo e nell'acquisizione dati, in particolare nel campo della fisica nucleare. Definito nel 1972 (EUR 4100) è uno dei più "antichi" standard informatici ancora in uso. Il bus CAMAC consente le comunicazioni tra uno o più moduli di interfaccia ed acquisizione dati ed un processore di controllo ("crate controller"), che a sua volta si connette ad un calcolatore esterno. Su questa scheda c'è anche un console/interface controller (DLART) DEC DC-319, impiegato in molti sistemi PDP-11. I due connettori grigi a sinistra costituiscono un'interfaccia Qbus completa.

Vedi: http://www-esd.fnal.gov/esd/catalog/intro/introcam.htm.

Esempi di moduli CAMAC: http://www-ese.fnal.gov/eseproj/BTeV/BTeV_Russia/default.html.

DEC DC-319: http://www.ibiblio.org/pub/academic/computer-science/history/pdp-11/hardware/micronotes/numerical/micronote33.txt.

Scheda Stromberg-Carlson con CPU J11.

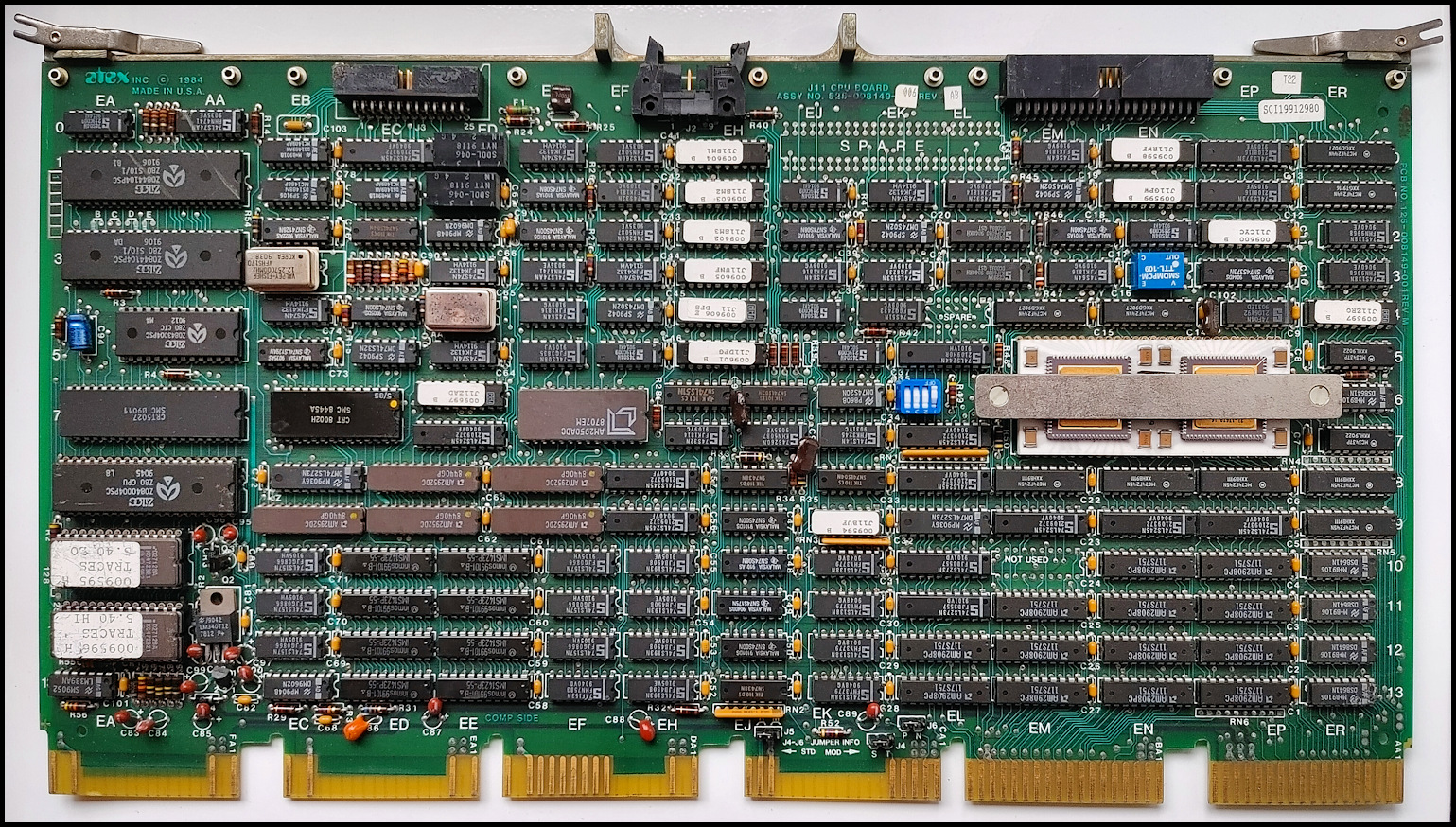

Single-board computer ATEX su scheda Unibus (1984), con CPU J11 e varie periferiche.

Scheda DEC M7554 (KDJ11-D/S) con CPU J11 (DCJ11-AC) a 15 MHz senza unità floating-point e 512 KB di RAM, utilizzata nei minicomputer DEC PDP 11/53 e nel DECserver 500/550. Il modello 11/53 è stato introdotto nel 1987 come versione ridotta (senza FPU né cache) dell'11/73. Le variante "Plus" (11/53+) ha più memoria RAM (1,5 MB) a bordo della scheda processore (KDJ11-DB).

Vedi: http://www.village.org/pdp11/faq.pages/11model.html; http://www.pdp-11.nl/.

Scheda DEC M7616 (KXJ11-CA), DCJ-11 CoProcessor. Si tratta di un I/O processor multifunzione per PDP-11 e VAX basato sulla CPU J-11. Contiene 128 KB di RAM.

Scheda DEC L0111-YC con CPU J-11. Si tratta di un processore di I/O (I/O Control Processor, o IOCP) impiegato nei cluster controller DEC HSC-70, -80 e -90. "HSC" è l'acronimo di Hierarchical Storage Controller. Queste apparecchiature erano processori di I/O specializzato che connettevano uno o più minicomputer VAX (6000, 7000, 8500 e 8600) ad array di dischi RA90 o RA92. La famiglia di controller HSC fa uso del protocollo proprietario MSCP (Mass Storage Control Protocol) introdotto dalla DEC ed introdotto col modellol HSC-50. L'MSCP è un protocollo a pacchetti progettato in maniera tale da minimizzare la necessità d'intervento della (o delle) CPU del sistema nel processo di gestione dei dischi e delle altre unità di memoria di massa, ad esempio riducendo il più possibile il numero delle richieste di interrupt necessarie per completare un'operazione di lettura da disco. I controller MSCP fanno uso di due "code" (queue) separate, una per i comandi inviati dalla CPU e l'altra per le risposte del sottosistema di I/O. Il formato dei pacchetti dell'MSCP è molto simile a quello delle connessioni VMScluster, quindi risulta semplice integrare uno o più controller HSC in un cluster VMS. DEC ha realizzato un'articolata serie di controller MSCP, sia per sistemi Unibus (come l'UDA50) che per macchine basate su Q-bus (ad esempio il diffuso M7555 RQDX).

Vedi: http://www.ricomputermuseum.org/Home/equipment/dec-hsc90-cluster-controller.

Scheda madre del personal computer DEC Professional 380 (Pro-380, 1985) con CPU J-11 funzionante a 10 MHz. I Pro-380 venivano spesso utilizzati come console per i VAX della serie 8000. Pur condividendo lo stesso processore con il PDP-11/73, le prestazioni del Pro-380 sono sensibilmente inferiori a causa della ridotta frequenza di clock (nel PDP-11/73 la CPU lavora a 16 o 18 MHz).

Vedi: http://www.bitsavers.org/pdf/dec/pdp11/pro3xx/.

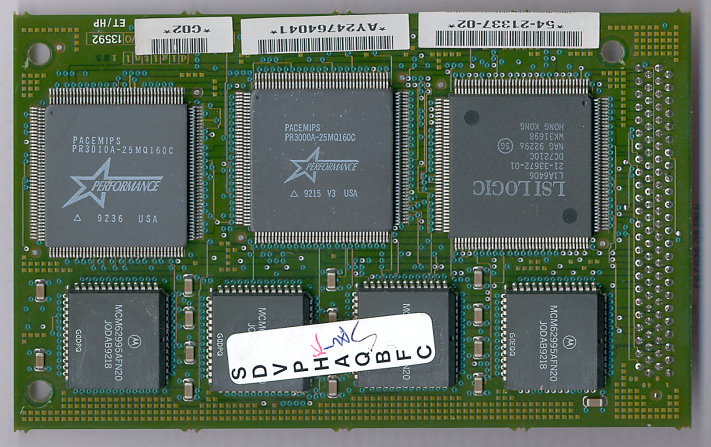

Prima versione del MicroVAX - First version of the MicroVAX CPU

CPU DEC MicroVAX I con FPU di tipo "F" e "G", KD32 o KA610 (1984/5). Questa scheda è stata la prima versione commerciale del MicroVAX (che solo con la release "II" è diventato una CPU single chip). Con un ciclo macchina di 250 ns, il MicroVAX originale o "MicroVAX I" era realizzato con un gate array LSI fabbricato da SEEQ (il componente quadrato) che implementava l’unità aritmetica/logica o ALU, affiancato da una quantità di circuiteria TTL standard a bassa e media scala di integrazione. MicroVAX I utilizza un subset (sottoinsieme) delle microistruzioni dell’architettura VAX vera e propria e, a differenza della versione successiva "II", non ha un modo di compatibilità con il PDP-11. Il microcodice del MicroVAX I è formato da 8K parole di 39 bit ciascuna. Su questa scheda è montata una cache di primo livello di 8 KB. Il processore MicroVAX I è stato utilizzato soprattutto nelle macchine DEC VAXstation I "Seahorse". Poteva indirizzare al più 8 MB di RAM; le prestazioni di questa CPU erano pari a circa 0,3 VUP. C’è, bisogna dirlo, una certa confusione sulla denominazione "MicroVAX". Vi è chi considera come primo membro della famiglia MicroVAX il MicroVAX II, e ciò a motivo del fatto che quest’ultimo è stato la prima incarnazione single chip di tale famiglia, nata con lo scopo di proporre l’architettura VAX, pur con qualche modifica, come standard industriale a 32 bit nel mondo dei microprocessori. Da un punto di vista tecnologico il processore MicroVAX raffigurato qui è una CPU multichip suddivisa in due schede QBUS: il modulo 7135 DAP o DAta Path (in figura) ed il modulo 7136 MCT, controller della memoria. L’unione delle due è nota come KA610. Buona parte della CPU stessa è contenuta in un gate array (vedi sopra) realizzato con processo NMOS a 4 mm (il MicroVAX II è fabbricato col processo ZMOS brevettato da DEC). Il MicroVAX II, 1985, è al contrario una CPU single chip (78032 o DC333) con FPU esterna (78132 o DC337), derivante in buona parte dal progetto del processore V-11.

DEC MicroVAX chip identification

SEEQ TQ8801: MicroVAX processor gate array (execution unit)

Dettaglio dell'Execution Unit del processore MicroVAX (Seeq TQ8801), 1984, con a sinistra le ROM del microcodice.

Questa è la seconda scheda della coppia che compone la CPU MicroVAX, e precisamente il Memory Controller M7136. All’epoca in cui venne progettato il MicroVAX non era tecnicamente fattibile l’integrazione di tutte le funzioni dell’architettura VAX in un unico circuito VLSI. Per questa ragione nel MicroVAX molte istruzioni che compongono il set originale del VAX sono ottenute non direttamente in hardware bensì mediante emulazione (software). Ciò riduce inoltre notevolmente la dimensione del microcodice della CPU.

Due manuali Digital che si occupano dell'hardware dei sistemi VAX; quello a sinistra, in particolare (1984) tratta delle macchine con bus VAXBI (vedi: http://en.wikipedia.org/wiki/VAXBI).

Un'ottima fonte di informazioni sugli aspetti tecnici delle macchine DEC sono i vari numeri, disponibili gratuitamente online in formato PDF, del Digital Technical Journal (DTJ): http://www.dtjcd.vmsresource.org.uk/. In particolare sono interessanti questi numeri:

VAX 8600 Processor, DTJ Number 1 August 1985 (PDF, 14.28MB)

MicroVAX II System, DTJ Number 2 March 1986 (PDF, 8.51MB)

VAX 8800 Family, DTJ Number 4 February 1987 (PDF, 9.89MB)

CVAX-based Systems, DTJ Number 7 August 1988 (PDF, 11.14MB)

VAX 6000 Model 400 System, DTJ Volume 2 Number 2 Spring 1990 (PDF, 8.67MB)

VAX 9000 series, DTJ Volume 2 Number 4 1990 (PDF, 12.4MB)

NVAX-microprocessor VAX Systems, DTJ Volume 4 Number 3 1992 (PDF, 9.56MB)

Prima implementazione VLSI dell’architettura VAX - First VLSI implementation of the VAX microarchitecture

Scheda DEC KA820-AA (1985) - Basata sul bus VAX-BI, contiene una CPU V-11 "Scorpio" a 5 MHz (vedi). Questo processore era utilizzato nel minicomputer VAX 8250/8350 (1986). Il V-11 è stata da un punto di vista storico la prima implementazione dell’architettura VAX in forma di microprocessore VLSI, benché il MicroVAX sia stato presentato con circa un anno e mezzo d’anticipo (1984). La CPU V-11, orientata ai sistemi di medio livello ed alle soluzioni embedded, è composta da quattro distinte unità: i chip di ROM/RAM di controllo DC327 (in alto a sinistra), l’unità di esecuzione integer (IE, DC328, immediatamente alla destra della precedente, 60 mila transistor: supporta tutte le 304 istruzioni del set VAX completo), un’unità di gestione della memoria, della cache e di traduzione degli indirizzi, che funge anche da controller di I/O (M, DC329, subito sotto, 54 mila transistor) ed un acceleratore per le operazioni in virgola mobile (F o DC330, a destra circondato dalla cache, 29.600 transistor). Il progetto "Scorpio" segna l’ingresso del VAX nel mondo VLSI ed è accompagnato da una notevole modernizzazione del processo produttivo, sia nella fase di progettazione con l’impiego di un nuovo CAD chiamato CHAS, sia in quella di realizzazione dei circuiti integrati, fabbricati ora col processo ZMOS brevettato da DEC (il primo processo MOS a due livelli di metallizzazione ad essere utilizzato nella pratica). La CPU V-11 fece il suo debutto alla frequenza di 5 MHz; le versioni più recenti (1987) sono state spinte fino a 6,25 MHz. Nel complesso assorbe circa 16 W. Venne impiegata, con discreto successo commerciale, nei sistemi 8200 ed 8300, che con i VAX di fascia alta (8500 ed 8800) condividevano il nuovo bus ad alte prestazioni VAX-BI, appositamente progettato per il supporto di configurazioni multiprocessore, ma non la tecnologia di realizzazione del processore (ECL, più veloce, nei sistemi 8500/800). Nel 1987, quando già si era affermato il più potente MicroVAX II, i processori V-11 furono destinati ad equipaggiare sistemi entry level come l’8250 e l’8350. L’importanza storica del processore "Scorpio" consiste principalmente nel fatto che con esso inizia l’era delle CPU progettate e realizzate interamente da DEC: fino a quel momento, infatti, solamente il disegno concettuale dei processori era opera diretta della Digital, che si appoggiava a terze parti (esterne) per la fabbricazione dei processori stessi. V-11 è una CPU poco nota, almeno qui in Europa, e relativamente rara perché il suo debutto è stato oscurato da quello, avvenuto pochi mesi dopo, del più semplice ma anche potenzialmente più veloce microVAX I. Lo del V-11 iniziò alla fine del 1983 sotto la guida di Bill Johnson e durò circa 18 mesi; il progetto concettuale della CPU fu presentato nel 1984 all’International Solid State Circuits Conference (ISSCC). Il microcodice del processore V-11 è modificabile (patchable), come quelli delle macchine VAX tradizionali; per questo motivo, i chip DC327 (cinque in totale) contengono a fianco di una ROM da 16K una parte di memoria RAM (1K) ed un’ulteriore piccola memoria CAM (Content Addressable Memory, 32 word da 14 bit l’una).

DEC V-11 chip identification

DC327: ROM/RAM, 208K transistor

DC328: execution unit (IE), 60K transistor (instruction buffer, microsequencer, execution unit, MTB)

DC329: system control chip (M chip), 54K transistor

DC330: floating point unit (F chip), 29,6K transistor

Tutti questi chip erano fabbricati direttamente da DEC con processo ZMOS (NMOS a doppia metallizzazione, 3 micron). La CPU funzionava a 5 MHz poi innalzati a 6,25.

Una bella foto (molto migliore della mia!) di questa scheda è visibile qui: http://www.cpu-galaxy.at/Boards/Boards_CPU/Boards_CPU.htm. Nello stesso sito, in questa pagina, c'è un bel dettaglio del chip DC327.

Il processore KA820 è descritto in dettaglio nel VAXBI Options Handbook, Chapter 10, DEC 1986.

Primo MicroVAX single chip - First MicroVAX single-chip microprocessor

Scheda Qbus DEC M7606-AA o KA630-AA con CPU MicroVAX II (1986, vedi). Questa prima versione della M7606 è anche nota come KA630-A ed è stata usata nei sistemi MicroVAX II "Mayflower". Il MicroVAX II (78032 o DC333), CPU a 32 bit, è stato il primo microprocessore single chip con architettura VAX e anche il primo microprocessore commerciale dotato di memory management unit (MMU, unità gestione della memoria) integrata nel chip. Questa scheda utilizza l’LMI (Local Memory Interconnect), un sistema di comunicazione tra CPU e memoria a 3 vie (attraverso il bus di sistema, per mezzo del Qbus oppure grazie ad un apposito cavo che si connette direttamente alle schede RAM compatibili). Sulla scheda trova anche posto 1 MB di memoria RAM locale. L’M7606 "prima versione" è stata la prima scheda DEC ad utilizzare l’allora nuovissima CPU MicroVAX II. Quest’ultima era realizzata con processo ZMOS a 3 micrometri e funzionava originariamente a 5 MHz. Fisicamente era suddivisa in due chip VLSI: la CPU vera e propria e la FPU (78132 o DC337). Il MicroVAX II è dettagliatamente descritto nel numero di Marzo 1986 del Digital Technical Journal. Vedi: http://www.microvax2.org/.

Copertina del numero 2, Marzo 1986, del Digital Technical Journal dedicato al MicroVAX II.

Seconda versione (KA630-B) della scheda DEC M7606 (1987), nota anche come M7606-A1. Funzionalmente è equivalente alla M7606-AA originaria. E’ stata impiegata nelle VAXstation II e nelle VAXstation II/GPX "Caylith" e, più in generale, nei sistemi basati su CPU KA630 venduti dopo il Febbraio 1987.

Vedi: http://www.vaxination.ca/vms/microvax/mv_ii.html; http://www.microvax2.org/; http://hampage.hu/dr/ka630.html.

Vedi: http://bitsavers.vt100.net/pdf/dec/vax/630/EK-KA630-UG-001_Feb86.pdf.

Anche: http://www.vaxination.ca/vms/microvax/mv_ii.html.

DEC MicroVAX II chip identification

DC333: MicroVAX II CPU, 125K transistor, "21-20887-01"

DC337: MicroVAX II FPU, 34K transistor, "21-22797-00"

DC379 + DC380: MicroVAX Interface gate arrays, LSI Logic L1A0485 "21-23413-01" + L1A0486 "21-23389-01"

DC319(AP): Console interface/controller, DEC "21-17312-00"

Tutti questi chip erano fabbricati direttamente da DEC con processo ZMOS (NMOS a doppia metallizzazione, 3 micron). La CPU funzionava a 5 MHz.

Vedi: http://simh.trailing-edge.com/semi/uvax.html.

Primo microprocessore VAX CMOS - First CMOS VAX microprocessor

Primo microprocessore commerciale con cache dati e istruzioni - First commercial micro with both I and D caches

Motherboard della workstation VAXstation 3100/40 "PVAX" (1989) - Utilizza una CPU CVAX a 11 MHz (scheda KA42-A) e hard disk SCSI. La 3100 è stata tra le VAXstation più popolari, soprattutto in ambito universitario. Benché fosse considerata una macchina entry level aveva delle prestazioni molto buone ed un ottimo rapporto qualità/prezzo.

Si veda ad es.: http://home.iae.nl/users/pb0aia/vax/dsvs3100.html (documento ufficiale DEC), oppure i siti dedicati come: http://home.iae.nl/users/pb0aia/vax/vs3khw.html e http://sites.inka.de/pcde/collection/vax3100.html.

DEC CVAX chip identification

DC341: CVAX CPU, 180K transistor, "21-24674-14" (orig.) oppure "21-24474-15", "21-25091-01"

DC513: CVAX FPU (CFPA), 34K transistor, "21-24674-17" oppure "21-26604-06", "21-26604-07"

DC509 (optional): CVAX clock chip, 0,35K transistor, "21-24673-01"

Originariamente il CVAX venne fabbricato da DEC con processo CMOS a doppia metallizzazione a 2 micron (denominato CMOS1); le CPU così ottenute funzionavano a 10-14 MHz. In seguito il processo di fabbricazione venne portato a 1,5 micron (CMOS2) e la frequenza di lavoro elevata fino a 16,67 MHz (1987). Lo stesso vale per il chip CMCTL (CVAX Memory Controller, DC557). Le versioni a 1,5 micron della CPU e della FPU sono rispettivamente note come CVAX-60 e CFPA-60, identificate dalle sigle DC580 e DC581. Nel 1990 infine venne rilasciata una versione single chip del CVAX nota come "SOC" (System On Chip, DC222) e formata dalla riunione in un unico componente della CPU, della FPU e del clock chip. Il SOC funzionava a 25 MHz ed era realizzato con processo CMOS3 a 1 micron, tripla metallizzazione.

CPU DEC M7620-AA o KA650-AA con processore CVAX (1987, vedi) a 11,11 MHz. Utilizzata nelle macchine MicroVAX 3500 e 3600 "Mayfair II", questa CPU utilizza una cache di primo livello write through da 1 KB, direct mapped, ed una di secondo livello da 64 KB. Il CVAX o DEC 78034 (introdotto nel 1987), funzionante a 10 - 14 MHz, è stata la prima CPU MicroVAX realizzata con processo CMOS (a 2 micron, doppia metallizzazione) nonché il primo processore di questa famiglia ad incorporare una cache di primo livello. Architetturalmente rappresenta un notevole miglioramento del MicroVAX II: ad esempio, sia l’unità integer che la FPU sono sensibilmente più efficienti e veloci (circa 2,5 volte più veloci del MicroVAX II). La scheda incorpora uno specifico chipset progettato da DEC e formato dal System Support Chip (CSSC), dal Memory Controller (CMCTL) e dal Qbus Interface Chip (CQBIC). Alcune versioni integrano un controller Ethernet (SGEC). La CPU KA650 esiste in due versioni identificate rispettivamente come "-AA" e "-BA", equivalenti a livello hardware (la versione KA650-BA veniva venduta con una licenza single-user, o "workstation license" anziché multiutente ("full license"), del sistema operativo).

Il processore CVAX è stato il primo microprocessore sviluppato da DEC con una cache L1 incorporata (ampia 1 KB). Una particolarità di questa CPU consiste nell'uso di una cache basata su DRAM anziché su SRAM (come nella maggior parte dei microprocessori). Tale tipo di memoria venne scelto in quanto, benché più lento della SRAM, richiedeva meno transistor per bit e consentiva così di contenere le dimensioni del chip ed il numero di transistor totali.

Vedi: http://hampage.hu/dr/ka650.html; http://hampage.hu/oldiron/e_vaxen.html; http://www.mcmanis.com/chuck/Computers/vaxen/.

Sulla storia del Qbus: http://hampage.hu/dr/qbus.html.

Scheda Qbus DEC M7624 o KA640 con processore CVAX, utilizzata nei MicroVAX 3300/3400 "Mayfair". Ha a bordo 4 MB di RAM, un controller DSSI ed un controller Ethernet. Le schede Qbus con processore CVAX impiegano una particolare architettura nella quale la CPU è direttamente connessa ad un bus locale, la cui estensione è limitata alla scheda stessa; un apposito ASIC provvede a fare da interfaccia tra questo bus locale ed il bus di sistema. Nei modelli più economici, come ad esempio la KA640, al bus locale è collegato esclusivamente questo dispositivo: tutte le altre interfacce (rete, DSSI ecc.) si trovano "a valle" di esso e non possono effettuare operazioni di DMA con la memoria centrale, ma soltanto coi propri buffer. Tale limitazione non esiste nelle schede di fascia più elevata (KA660) in cui anche i controller Ethernet, SCSI e DSSI sono connessi al bus locale (si dicono quindi "nexi" in gergo DEC). Le schede Qbus con CPU CVAX non sono progettate per supportare configurazioni a più processori (SMP).

Dettaglio degli integrati, in package CERQUAD, che formano il processore CVAX. La CPU ha 84 pin e contiene circa 180.000 transistor; la FPU ha 68 pin (60.000 transistor); il controller di memoria CMCTL ha 132 pin e contiene circa 25.000 transistor. La CPU CVAX funziona a 20 MHz con un ciclo di 100 ns (il ciclo di bus dura 200 ns). L'interfaccia verso il bus di sistema Qbus (Q-22) è rappresentata dal chip CQBIC, che ha un package a 132 piedini e contiene circa 40.800 transistor.

DEC M7625-AA (KA655-A), scheda CPU per MicroVAX 3800 "Mayfair III" (1989) con processore CVAX+ funzionante a 16,67 MHz (60 ns) e 64 KB di cache esterna. I minicomputer MicroVAX 3800/3900, introdotti nell'Aprile del 1989, rappresentavano la "fascia alta" della famiglia MicroVAX ed erano progettati per competere con gli AS/400 di IBM. La CPU CVAX+ era una versione aggiornata dell'originale CVAX; la scheda KA655 da parte sua è una diretta evoluzione della KA650 (vedi sopra). Il microprocessore CVAX+ è in sostanza un CVAX fabbricato con processo CMOS a 1,5 micrometri, originariamente noto col nome "CVAX-60". Lo stesso processo venne adottato anche per la FPU (o CFPA) e per il controller di memoria (CMCTL).

Vedi: http://www.hackcanada.com/hackcanada/photograffiti/hihkal/microvax3800/index.html.

Vedi: http://www.netbsd.org/docs/Hardware/Machines/DEC/vax/microvaxes.html#microvaxes:microvax_3800.

Anche: http://www.mitlimited.com/MicroVax-3800-3900.htm; http://hampage.hu/vax/e_1989.html.

Qui sopra si può vedere

un processore CVAX+ a 16,67 MHz (60 ns) su scheda CPU KA62B per sistemi VAX 6000/300

"Hyperion" (Gennaio 1989). Prendendo come riferimento il componente quadrato più grande di

tutti, i chip costituenti il CVAX+ sono: il microprocessore vero e proprio (in

alto a sinistra), il generatore di clock (immediatamente a destra) e l’unità

in virgola mobile (a sua volta alla destra del precedente). Ancora più a destra

si riconosce il system controller (CMCTL).

Scheda CPU DEC T2011 (KA62A-AA) per VAX 6000/200 "Calypso" con processore CVAX (78034, DC341) a 80 ns, 12,5 MHz, e bus XMI. Introdotto nell'Aprile 1988 il modello 200 era la versione più piccola del VAX 6000; supportava da 1 a 4 CPU CVAX e fino a 256 MB di RAM ECC. Sulla scheda CPU vi sono 256 KB di cache L2 (160 ns). La parte della scheda in alto a destra è nota come "XMI corner" e contiene la logica di interfacciamento al bus. Sulla scheda sono presenti la CPU DC341 (identificata dalla sigla 21-24674-12), la FPU (CFPA) DC513 o 21-26604-03, il generatore di clock DC509 ed il system controller 78332 (21-24942-02), tutti realizzati con processo CMOS a 2 micron, doppia metallizzazione.

Vedi: http://simh.trailing-edge.com/semi/cvax.html.

Anche: http://research.microsoft.com/en-us/um/people/gbell/Digital/timeline/semicond.htm.

Questa è una scheda CPU

(KA60) della workstation DEC VAXstation 3520/40 "Firefly"

(vedi). Presentata

nel 1987, era una macchina dalle elevate prestazioni basata su una

configurazione SMP a due (3520) oppure a quattro vie (3540). Le CPU erano in

questo caso processori CVAX 78034, prima incarnazione CMOS dell’architettura

MicroVAX. La prima versione della workstation Firefly aveva invece due CPU

78032. Le

macchine 3520/40 impiegavano un particolare bus proprietario, detto MBUS, capace sulla carta di circa 26 MB/s

(la velocità effettiva era tuttavia assai minore). L’MBUS è un writeback

cache bus, il che significa che ciascun elemento del sistema ad esso collegato

possiede una sua propria cache locale, ed è in grado di intercettare le

operazioni (transazioni) che riguardano i dati collocati in tale cache,

potendoli così fornire in luogo della memoria di sistema. Questo meccanismo in

linea di principio dovrebbe migliorare di molto le prestazioni globali, ma nella

realtà a causa di un complicato intreccio di "colli di bottiglia"

l’incremento effettivamente conseguito non è proporzionato al costo

dell’architettura MBUS.

Scheda CPU Qbus DEC M7626 o KA660, con processore CVAX "SOC" (System On Chip), originariamente installata su un VAX 4000/200 "Spitfire" (1989). Il "SOC" è un microprocessore che integra in un singolo chip la CPU CVAX (DEC 78034), la FPU (CFPA), il generatore di clock e 8 KB di cache di secondo livello. E' fabbricato col processo CMOS di terza generazione brevettato da DEC (CMOS-3), a 1 micron con 3 livelli di metallizzazione. Introdotto alla fine del 1989, funziona a 25 MHz ed è stato impiegato nei server entry-level, nelle workstation e come CPU embedded in alcuni terminali grafici e stampanti laser fabbricati da DEC negli anni Novanta.

DEC CVAX "SOC" chip identification (with support chipset)

DC222: CVAX SOC CPU, "21-32064-07"

DC557: VAX main memory controller (CMCTL), "21-28310-01"

DC527: Q22 bus interface (CQBIC), "21-25972-02"

DC511: System Support chip (SSC), "21-24942-03"

DC541: Second Generation Ethernet Controller (SGEC), "21-28059-03"

DC542: Single Host Adapter chip to Interface DSSI (SHAC), "21-27667-02"

Scheda CPU KA550 proveniente da un minicomputer fault-tolerant VAXft modello 410 "Cirrus 2" (1991). con due CPU CVAX SOC a 28,57 MHz (35 ns di ciclo) accoppiate ciascuna a 128 KB di cache L2. I VAXft (1990-1993) formavano una famiglia di macchine ad architettura VAX a 32 bit, CPU CVAX o NVAX e sistema operativo VMS (con specifiche librerie di supporto) concepite come sistemi pienamente fault tolerant secondo il paradigma cosiddetto "lock step": brevemente, la macchina era formata da due computer identici funzionanti in parallelo, che eseguivano contemporaneamente le medesime istruzioni sugli stessi dati; la ridondanza delle CPU permette di individuare e correggere eventuali errori e, nello stesso tempo, assicura che la macchina rimanga in funzione nel caso in cui uno qualunque dei sottosistemi di cui è composta (CPU, memoria, I/O) si guasti. Il processore CVAX SOC integra in un singolo componente una CPU CVAX 78034, la FPU, il generatore di clock e 8 KB di cache di primo livello.

Vedi: https://www.hpl.hp.com/hpjournal/dtj/vol3num1/vol3num1art8.pdf; https://www.computerhistory.org/collections/catalog/102754382.

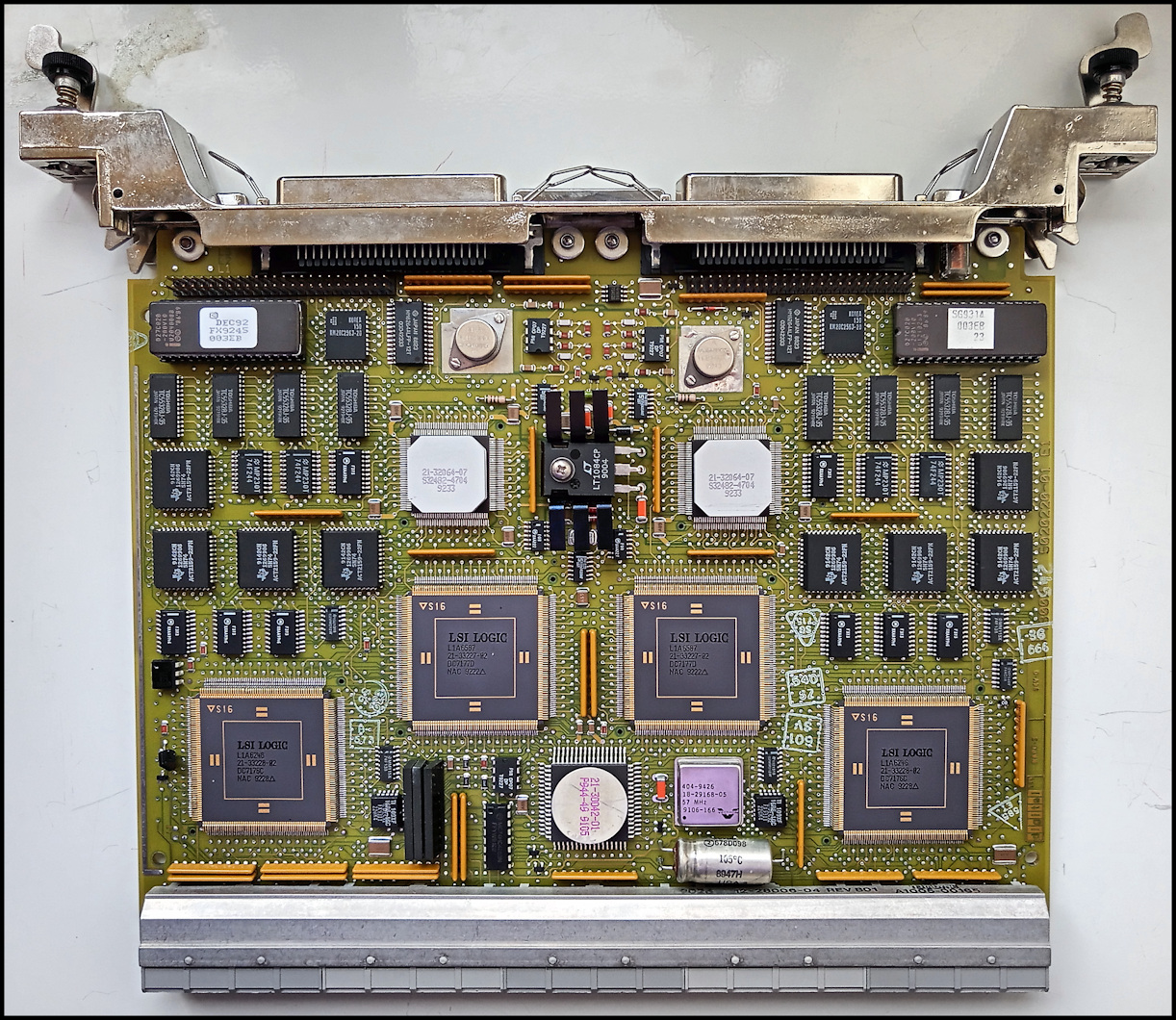

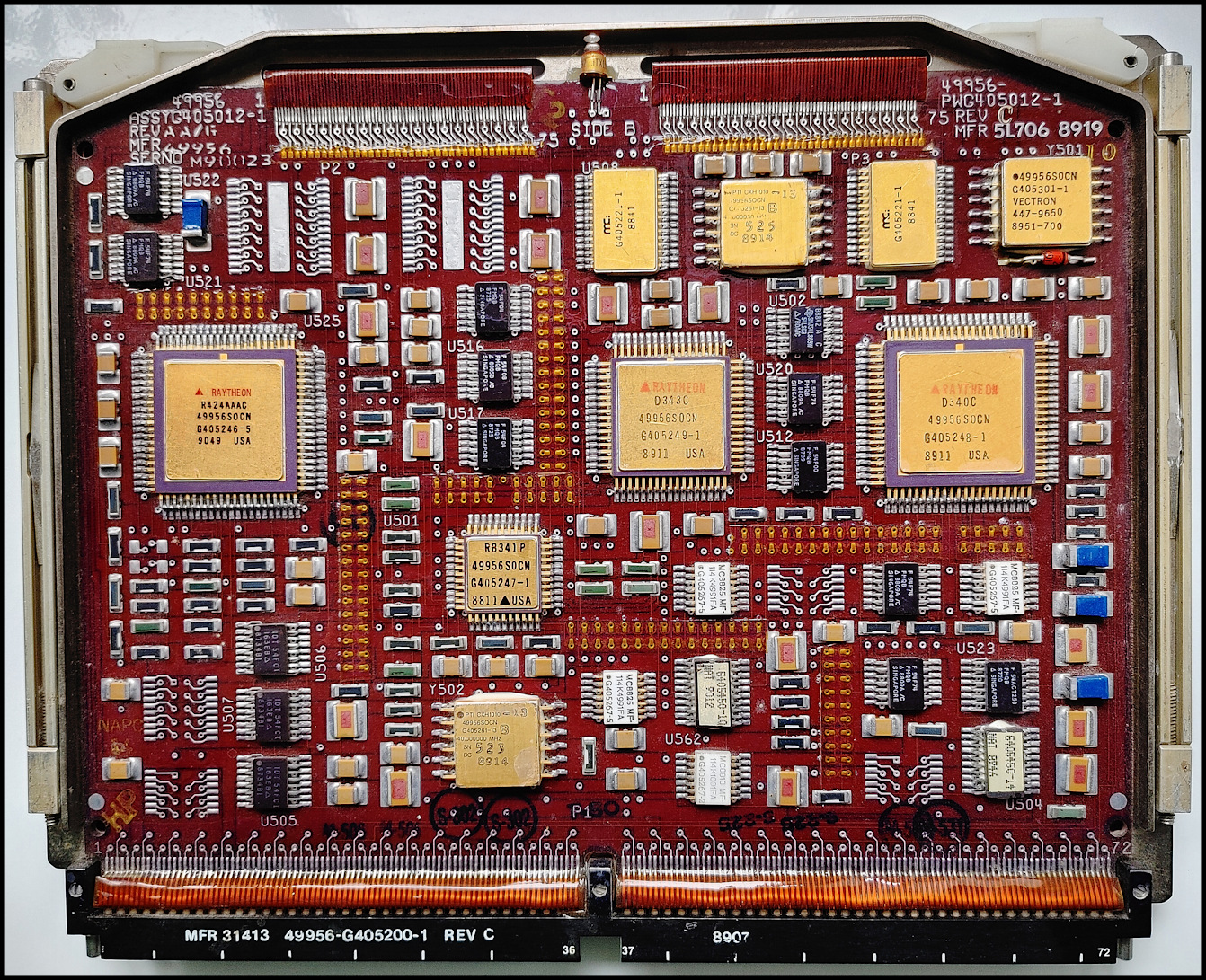

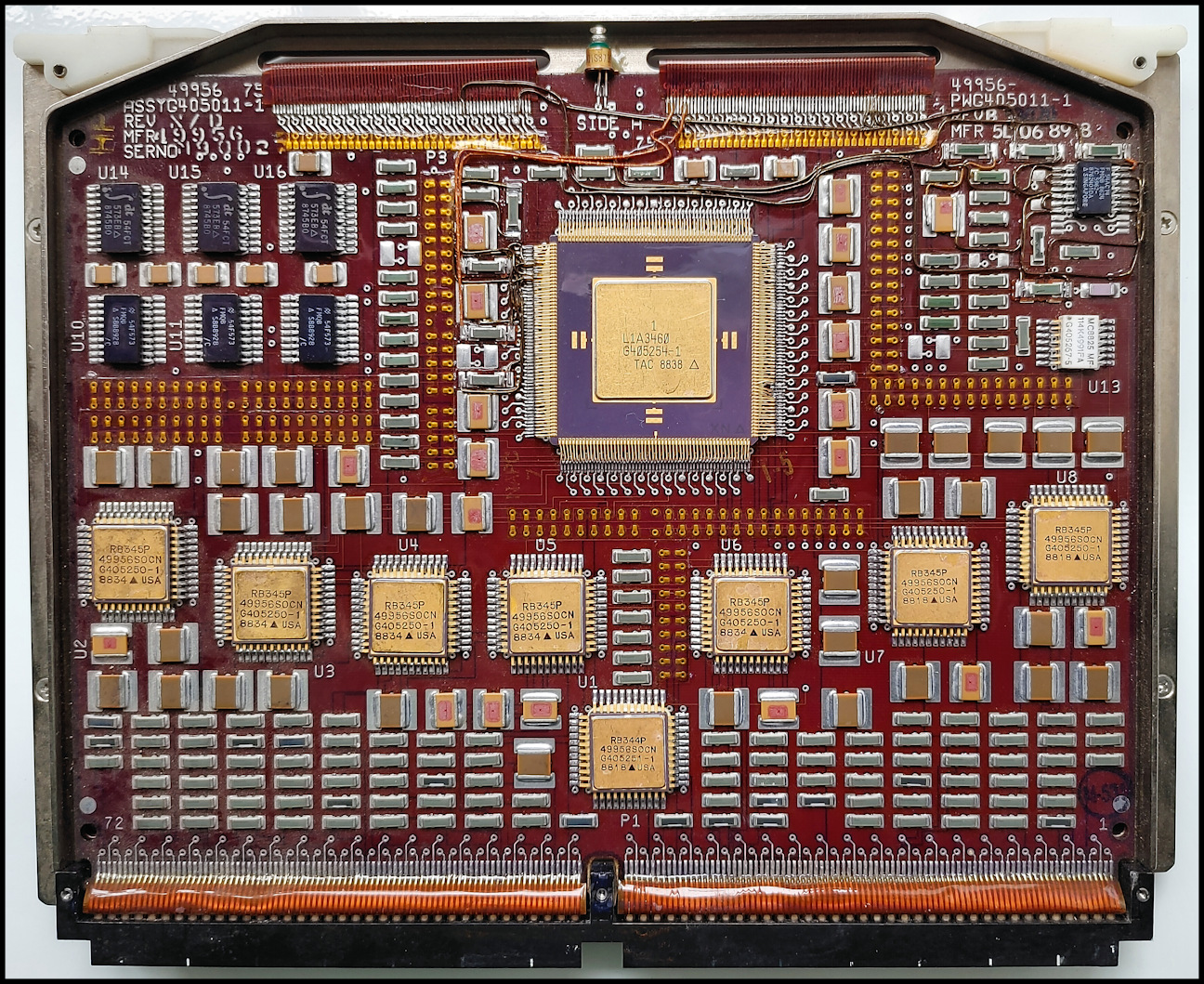

Modulo processore di un calcolatore Raytheon MILVAX (Military VAX), 1988/89. Contiene una CPU CVAX (D340C) con la relativa FPU (D343C), in package militare della stessa Raytheon. Il MILVAX o MILitary VAX Computer System, realizzato da Raytheon su licenza DEC ed assemblato in uno chassis per avionica USAF ATR, venne utilizzato per anni in svariate applicazioni aerospaziali e militari di terra: ad esempio, nello Space Shuttle, nel sistema di sorveglianza JSTARS, negli apparati di controllo degli ICBM (missili balistici intercontinentali, in sistemi radar EWS - Early Warning System degli Stati Uniti e della NATO più in generale). Un MILVAX costava circa il 30% in più delle sue controparti civili, e poteva eseguire gli stessi software. Indubbiamente si tratta della più particolare "incarnazione" dell'architettura VAX. Queste schede sono rare ma non rarissime come talvolta si afferma nei forum, perché nel corso della sua vita operativa il MILVAX venne prodotto in almeno 5.000 esemplari, alcuni dei quali tuttora in uso. Trovare un sistema completo è invece più difficile... Vedi: http://www.electricstuff.co.uk/milboards.html, https://www.youtube.com/watch?v=55z_0BYb5is.

Una scheda dello stesso tipo è visibile qui: https://www.computerhistory.org/collections/catalog/102757133.

Vedi: https://patents.google.com/patent/US5117360A/en (JSTARS), https://afspacemuseum.org/wp-content/uploads/histories/TheCape.pdf.

L'altro lato del modulo. I componenti, qui il più grande è un gate array di LSI Logic, hanno package ceramici a montaggio superficiale Rad-Hard (Radiation Hardened), che offrono una protezione dalle radiazioni significativamente superiore rispetto a quelli tradizionali. Questa caratteristica è importante negli apparati destinati all'industria militare ed aerospaziale. Il modulo è composto da due schede collegate da un connettore piatto ad alta densità (in alto) e montate su un telaio di alluminio che funge da dissipatore di calore. La forma di tale telaio aumenta inoltre l'efficacia del raffreddamento forzato ad aria, altro aspetto importante in un sistema avionico complesso come questo.

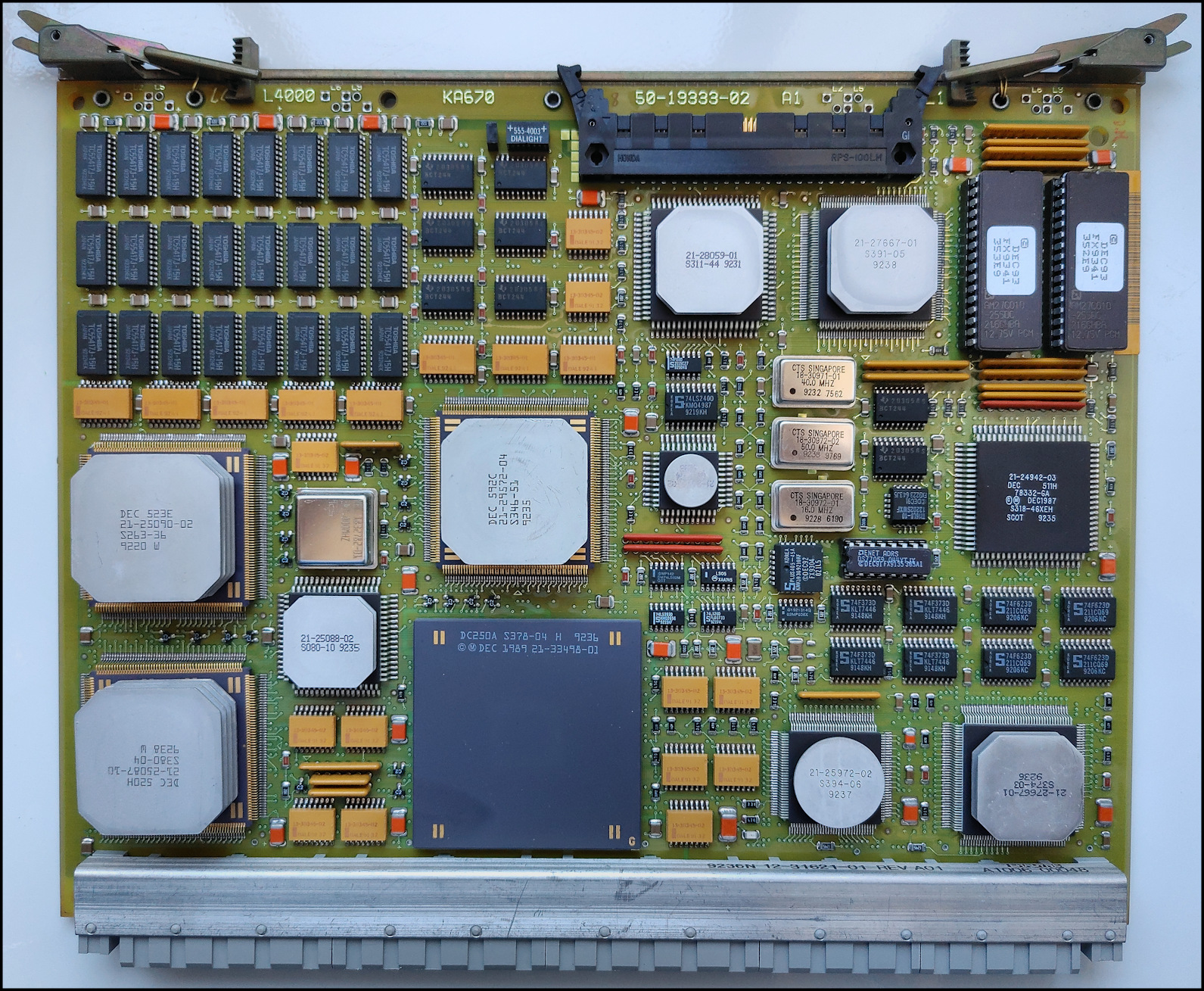

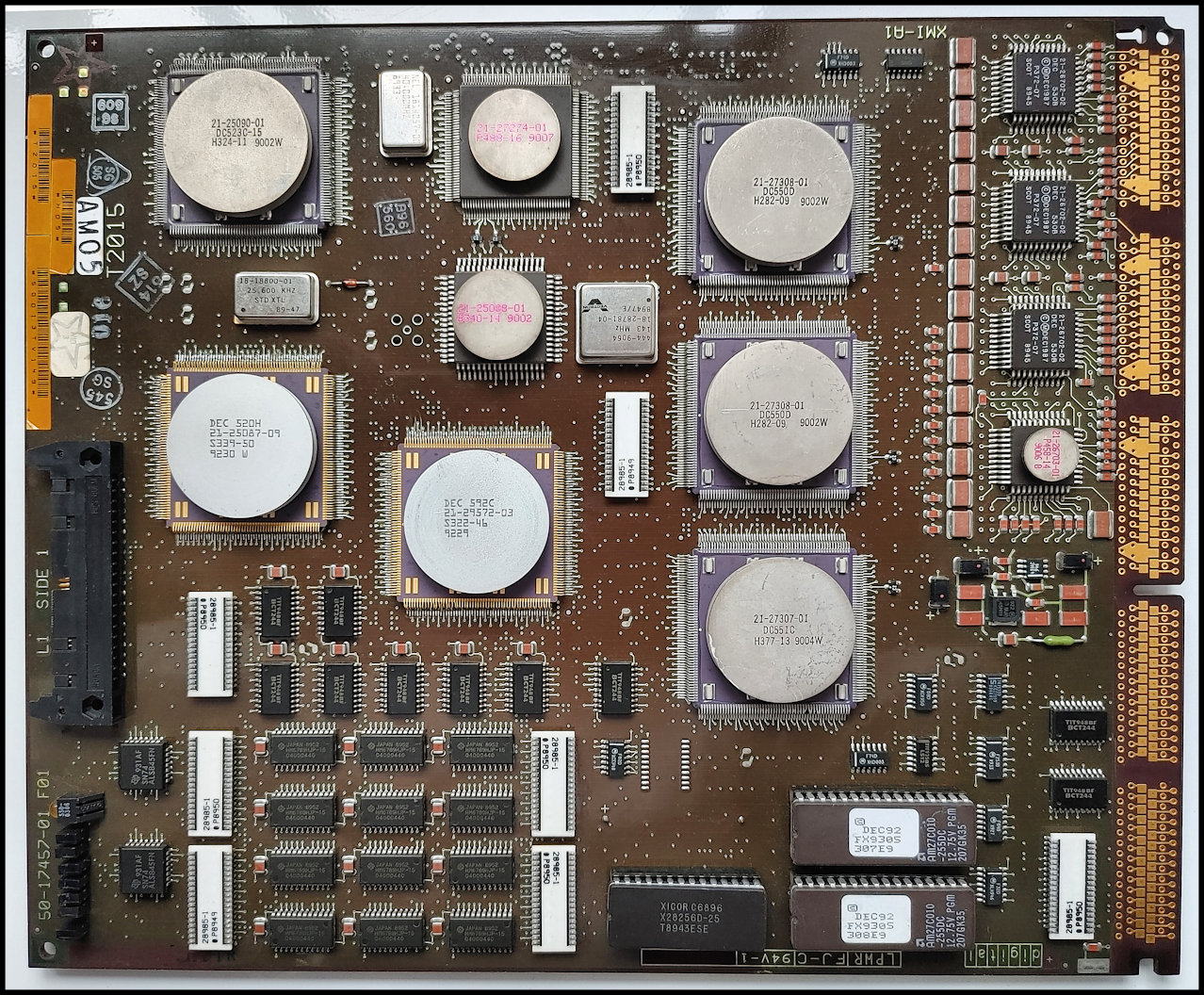

CPU DEC KA670-AA (L4000) appartenuta ad un VAX 4000/300 "Pele" (1990, vedi). La CPU è un processore Rigel a 55 MHz. I diversi chip che si vedono nell’immagine sono (in senso orario partendo da sinistra in alto): l’interfaccia del bus DSSI per le memorie di massa (SHAC); il controller del bus Q22 (QBIC); il memory controller (G chip) e sotto di esso quello della cache di secondo livello (C chip); il generatore di clock; il processore Rigel vero e proprio (P); la FPU (F); la cache di secondo livello; il controller Ethernet (SGEC), un secondo controller DSSI, al suo fianco le ROM con il firmware di sistema e immediatamente sopra l’SCC (System Controller Chip). Terzo scalino evolutivo lungo il cammino di crescita dell’architettura MicroVAX è stato il processore di terza generazione Rigel (questa la sequenza: MicroVAX - MicroVAX II - CVAX - Rigel - Mariah - NVAX - NVAX+), presentato nel 1987 ed entrato in produzione nel 1989. La CPU Rigel (funzionante a 25 – 55 MHz, con alcuni esemplari “spinti” fino a 60) ha conosciuto notevoli problemi di realizzazione, a motivo della dimensione del die insolitamente grande per l’epoca, che ne hanno ritardata la "discesa in campo". Anche per questo motivo, nonché per l’avvento dell’ancor più potente NVAX, non ha mai conosciuto il successo commerciale del CVAX, rimanendo legata a poche macchine (tra cui la più famosa e diffusa è senz’altro la VAXstation 4000/60). Rigel è suddiviso in più chip, come d’altra parte tutte le incarnazioni dell’architettura MicroVAX antecedenti l’avvento di NVAX: la CPU vera e propria (DC520, nome in codice "REX", 320mila transistor), la FPU (DC523, "KIWI", 135mila transistor), il cache controller (DC592, "COW", 220mila transistor) cui si aggiunge il generatore di clock (DC521). Ad esso sono dedicati uno specifico componente di supporto, detto RSSC (Rigel System Support Chip), ed un dispositivo più o meno analogo utilizzato nelle macchine VAX 4000 come interfaccia di sistema, detto "Ghidra". La CPU contiene 2 KB di cache (unificata) di primo livello e supporta un massimo di 128 KB di cache esterna di secondo livello. I chip Rigel sono stati prodotti con processo CMOS a 150 nm.

DEC Rigel chip identification, with support chipset

DC520: Rigel CPU a 143 MHz (REX, P-chip), 320K transistor, "21-25087-10", 224 pin flat ceramic

DC523: Rigel FPA (KIWI, F-chip), 135K transistor, "21-25090-02"

DC592: Rigel Cache Controller (COW, C-chip), 220K transistor, "21-29572-04"

DC521: Rigel clock generator, 0,35K transistor, "21-25088-02"

DC561: main memory controller (G-chip), "21-33498-01"

Gli altri chip sulla scheda KA670 corrispondono a quelli della KA680 (vedi).

Questi chip erano fabbricati da DEC con processo CMOS2 a doppia metallizzazione, 1,5 micron. La CPU Rigel funzionava a 35-40 MHz. Architetturalmente essa deriva dal processore del VAX 8800.

Immagine più dettagliata della stessa scheda CPU L4000/KA670.

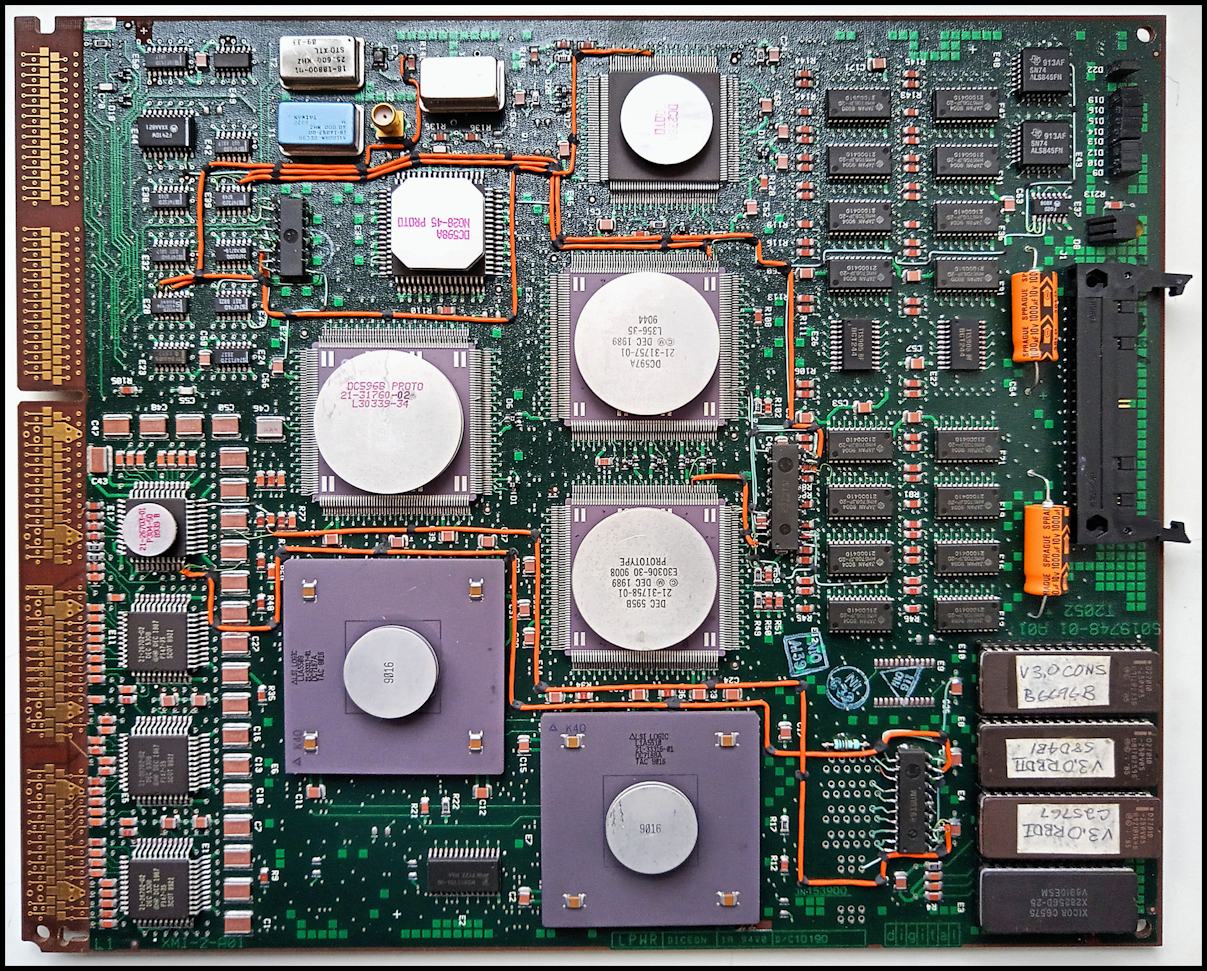

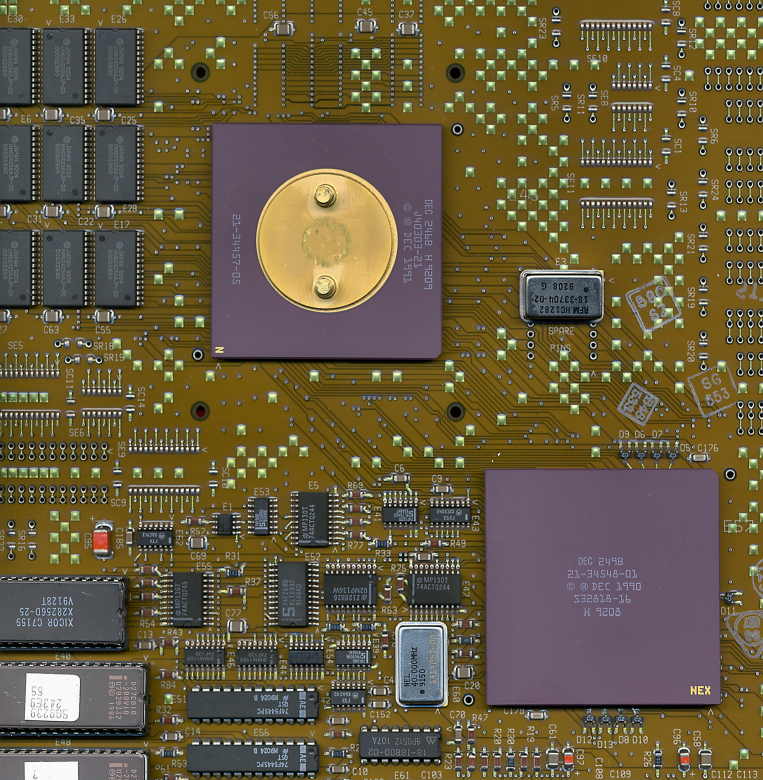

La CPU mostrata nella foto qui sopra è l’evoluzione di Rigel chiamata "Mariah", montata in questo caso sulla motherboard (DEC KA46) di una workstation VAXstation 4000/60 "PMariah" (Novembre 1991, vedi); funziona a 55 MHz ed ha una cache integrata di primo livello da 4 KB cui se ne affianca una di secondo livello su scheda (i cui chip sono visibili nella parte bassa dell’immagine) ampia 256 KB. La VAXstation 4000/60 era una macchina ad architettura TurboChannel che ha avuto un discreto successo commerciale; fu seguita dalla più potente versione /90 "Cougar" (1992) basata invece su processore NVAX.

DEC Mariah chip identification

DC595(D): Mariah CPU, "21-31758-03"

DC596(D): Mariah FPU, "21-31760-01"

DC597: Mariah cache controller, "21-31757-01"

System controller gate array: Toshiba TC140H68CY-0002, "213577501"

Questi tre chip vennero fabbricati da DEC con processo CMOS3 a tripla metallizzazione, 1 micron. La CPU Mariah è in sostanza una versione migliorata del Rigel funzionante a 62-71 MHz con supporto per cache di tipo writeback.

Motherboard DEC KA43-A di workstation VAXstation 3100/76 con CPU Rigel (1990) - La VAXstation 3100/76, nome in codice "RigelMax" era una workstation di fascia medio/alta equipaggiata con processore Rigel (28 ns, vedi), 128 KB di cache di secondo livello, 8-32 MB di RAM e hard disk SCSI. Come scheda video si poteva montare la DEC SPX accelerata in hardware ed ottimizzata per il CAD (arrivava ad una risoluzione massima di 1.280 x 1.024). Questo tipo di macchine era dotato del sistema operativo VMS oppure del più recente ULTRIX, sempre di DEC; recentemente un buon numero di esse è stato recuperato dagli appassionati di retrocomputing con l’installazione di NetBSD oppure di Linux.

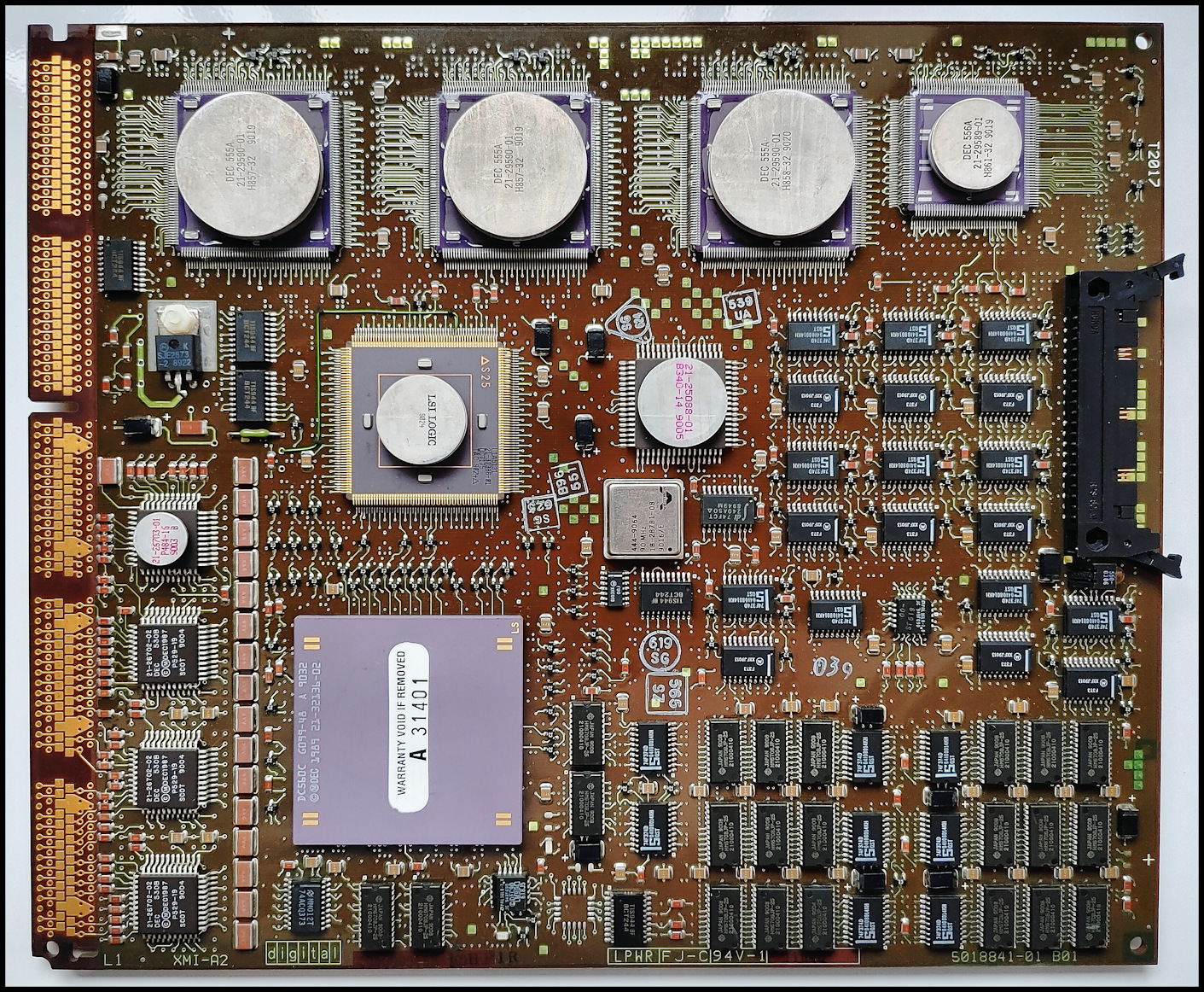

CPU del VAX 6000/500 "Calypso/XMP", con processore Mariah a 71 MHz (1990). I VAX 6000 erano sistemi multiprocessore di fascia alta destinati all’uso come server oppure nei centri di calcolo di grandi aziende od enti pubblici. Impiegavano l’architettura ad elevate prestazioni XMI.

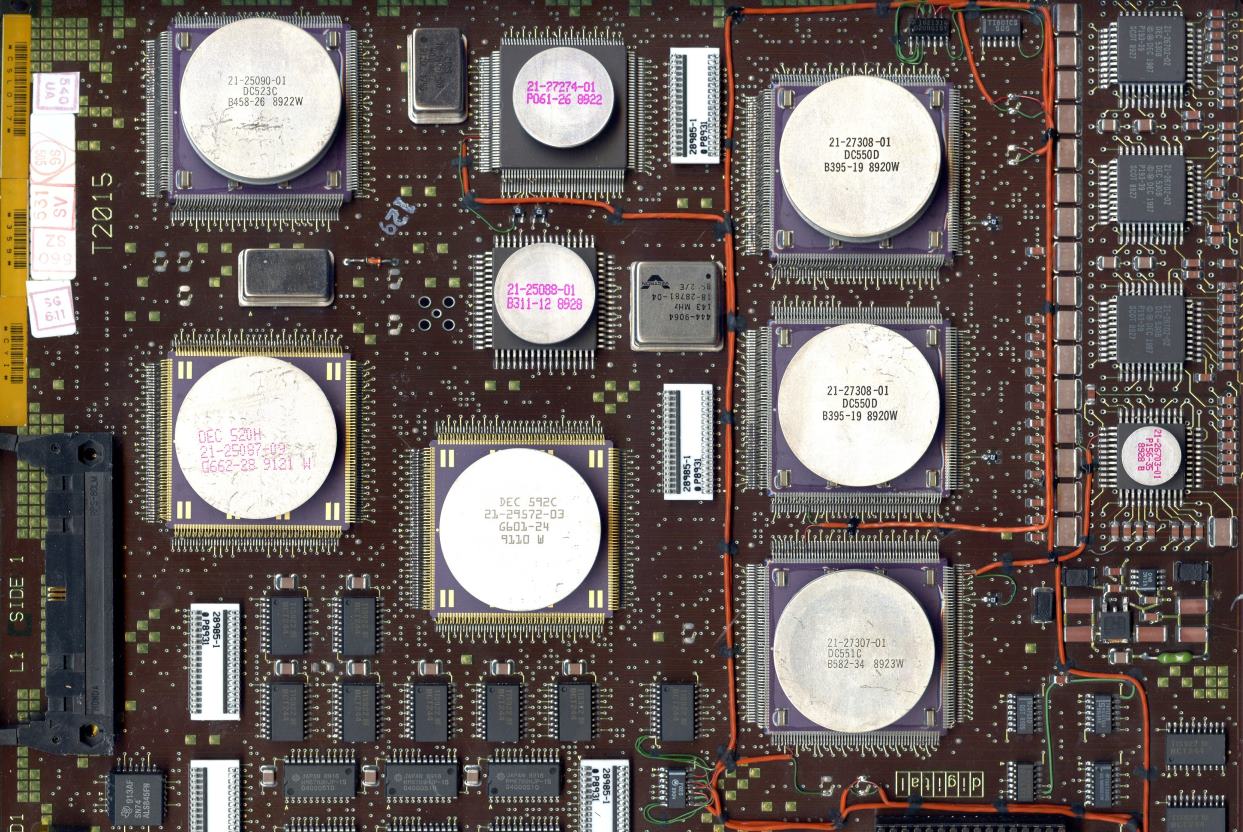

Dettaglio degli integrati che compongono la CPU Mariah a 71 MHz (scheda DEC T2052, XMI-2-A01) di un VAX 6000 modello 500 (o, brevemente, 6500 - vedi: http://www.compaq.com/alphaserver/vax/archive/vax6000_500.html). Il processore Mariah è un'evoluzione della precedente CPU Rigel, ed in particolare rispetto a quest'ultima utilizza una cache di primo livello (L1) di tipo write-back. Le prestazioni medie sono di circa 13 volte superiori a quelle di un VAX 11/780. Il processore Mariah era fabbricato con processo CMOS-3 a 1 micron ed è stato utilizzato, oltre che nel VAX 6000/500, nel MicroVAX 3100/80 e nella VAXstation 4000/60. Tre sono gli integrati che lo compongono: la CPU vera e propria (DC595), la FPU (DC596) ed il cache/memory controller (DC597). Nella VAXstation 4000/60 quest'ultimo non è presente ed un sottoinsieme delle sue funzioni è implementato in un apposito chip (System Controller). La CPU contiene 4 KB di cache L1; 512 KB di cache L2 trovano invece posto sulla scheda. La FPU è semplicemente la versione CMOS-3 di quella del predecessore Rigel.

Dettaglio della CPU Mariah sulla scheda CPU (T2015) di un VAX 6000-510, funzionante a 72 MHz. Alla scheda è collegato un acceleratore Nemonix (non visibile, nella parte destra dell'immagine si riconoscono però le modifiche necessarie alla sua installazione). Una macchina completa con questa stessa configurazione è visibile qui.

Scheda DEC T2052 (KA65-AA) per VAX 6000-500 con prototipo di CPU "Mariah" (1990). Tale CPU era, in sostanza, un aggiornamento del processore Rigel al processo produttivo CMOS3, che includeva anche un passaggio dalla cache write-through alla più performante write-back, allo scopo di prolungare la vita operativa della famiglia VAX 6000 e di migliorarne le prestazioni, alleggerendo il carico sul bus XMI.

Scheda DEC T2052 (KA65A-AA) con CPU "Mariah" per VAX 6000-500, nel contenitore originale.

CPU DEC T2015 per VAX 6000-400 e -500.

DEC T2017 Vector Processing Unit per VAX 6000-510 (in origine accoppiata alla CPU T2015 dell'immagine precedente), 1990, vista frontale. E' un'opzione piuttosto rara per la famiglia VAX 6000, indirizzata al calcolo scientifico/ingegneristico ed all'elaborazione numerica di segnali; si tratta di una FPU aggiuntiva specializzata nell'elaborazione di dati in forma vettoriale e matrici. Si collega alla CPU T2015 con una connessione dedicata (connettore nero, a destra). Per essere sfruttata, richiede l'utilizzo di apposite librerie FORTRAN o C. La velocità di calcolo è nell'ordine di qualche decina di MFLOP.

DEC T2017, vista del retro.

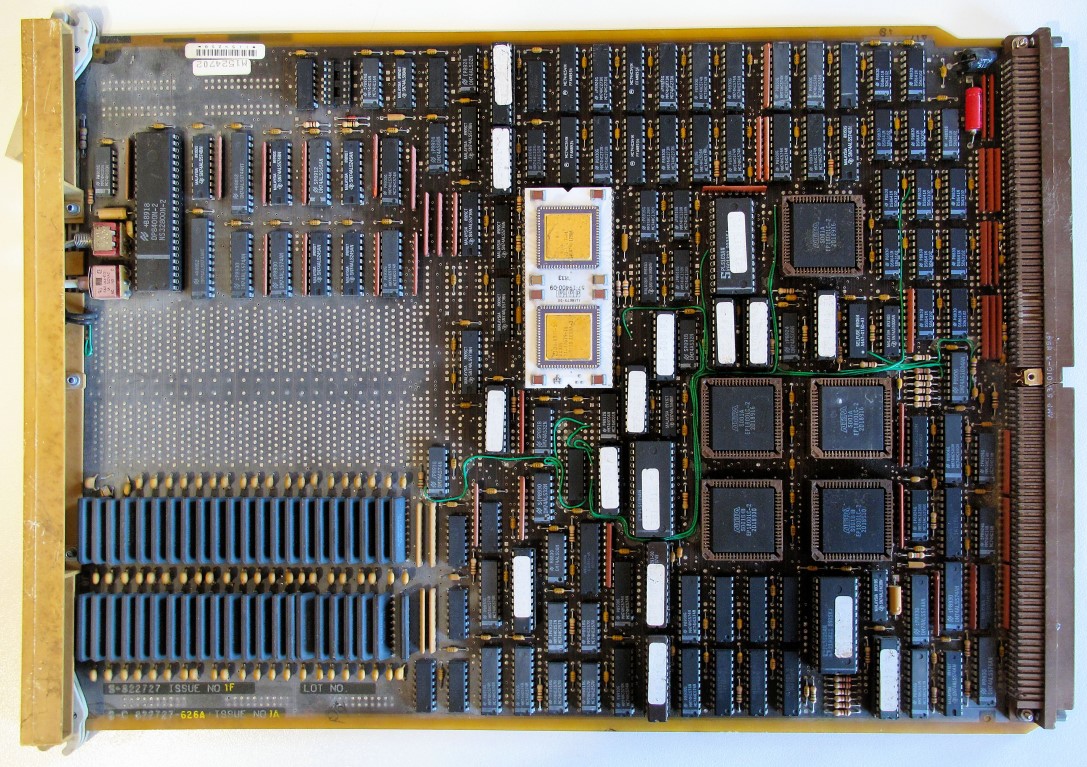

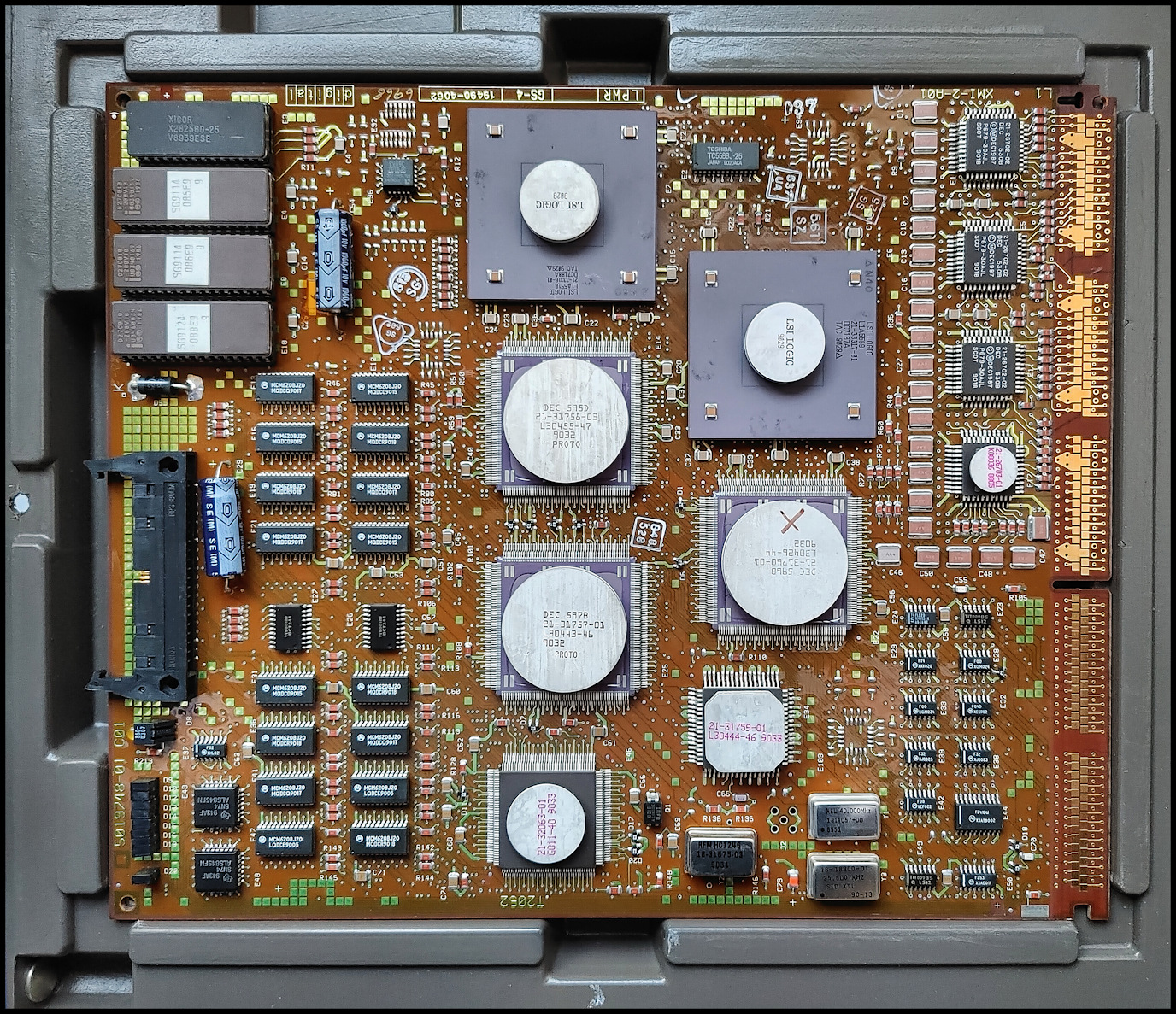

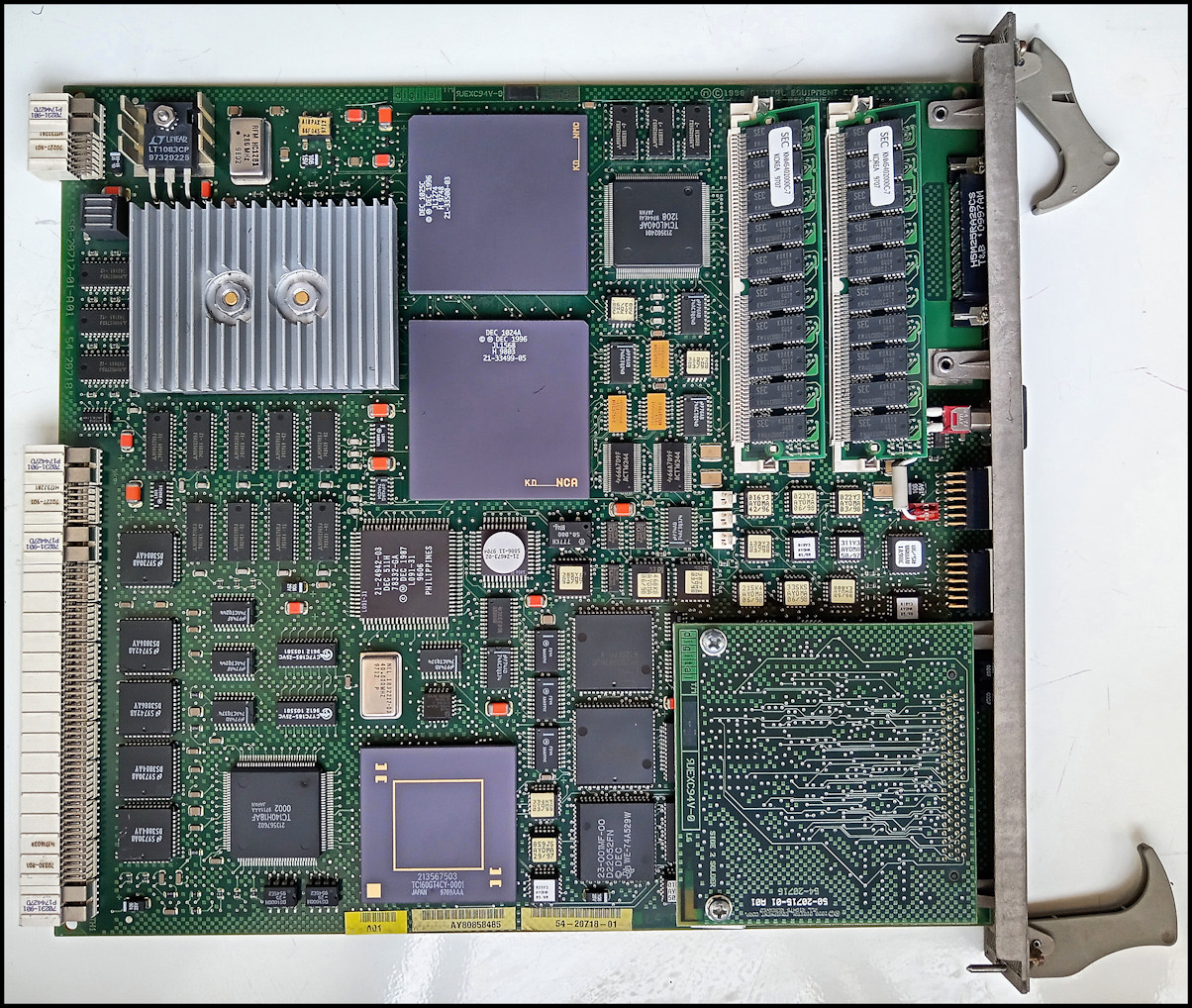

Scheda CPU DEC KA680-AA,

L4002 (1992, vedi) - Si tratta di un processore per macchine VAX

4000/500 "Omega/N"; sulla scheda

trova posto un processore NVAX a 75 MHz (a sinistra, con dissipatore di calore).

L’NVAX è stato l’ultimo gradino evolutivo dell’architettura VAX, nonché,

al momento della sua presentazione nel 1991, la più veloce CPU CISC disponibile

sul mercato. Sviluppato parallelamente al RISC Alpha 21064 con processo

produttivo simile e risorse tecnologiche ed umane paragonabili, l’NVAX è da

molti considerato il massimo ottenibile in ambito CISC. Contiene all’incirca

1,3 milioni di transistor realizzati con processo CMOS4 a 0,75 mm,

tripla metallizzazione, ridotti a 0,50 nella versione "Plus" (CMOS5).

Quanto a complessità l’NVAX è paragonabile all’Intel 80486; come

prestazioni e soluzioni architetturali gli risulta però sicuramente superiore.

Si tratta di un processore single chip (che contiene tanto l’unità in virgola

mobile quanto il controller della cache) basato su architettura di tipo macro

pipelined con branch prediction, fortemente ottimizzata per l’esecuzione delle

istruzioni VAX con l’impiego del minor numero possibile di cicli di clock. La

FPU dell’NVAX è identica a quella del predecessore Rigel. L’NVAX funziona a

75 – 90 MHz; l’NVAX+, che è a sua volta compatibile "pin to pin"

con l’Alpha 21064 il che consentiva il rapido aggiornamento dei sistemi VAX

7000, arriva a 143 MHz. Come il processore Rigel si ispirava all’architettura

del VAX 8800 "Nautilus", così l’NVAX, il cui progetto iniziò nel

1987, trae spunto da quella del VAX 9000 "Aquarius", alla quale è

tuttavia superiore in termini di prestazioni “pure” (il VAX 9000 era un

server di grandi dimensioni a CPU multiple realizzate con gate array ECL). L’NVAX possiede due livelli di cache integrata,

una da 2 KB per le istruzioni ed una seconda, unificata per dati ed istruzioni,

da 8 KB; un terzo livello, di tipo writeback, è collocato esternamente al

processore ed è realizzato con integrati SRAM da 8 – 12 ns per un’ampiezza

di 128 – 512 KB. L’NVAX assorbe circa 18 W alla frequenza di lavoro di 75

MHz. È stato utilizzato in una vasta gamma di macchine DEC: dai sistemi entry

level 4000/400 – 600, alle macchine di fascia media VAX 6000/600, fino ai

server 7000 e 10000, questi ultimi al top della gamma proposta da Digital. I due

grandi componenti quadrati a destra della CPU sono rispettivamente il controller

di I/O o NCA (in alto) ed quello della memoria, NMC (sotto). Si tratta di due

dispositivi custom VLSI realizzati da DEC con processo CMOS3 a 1 mm,