Vintage IBM technology!

![]()

Pagina in costruzione

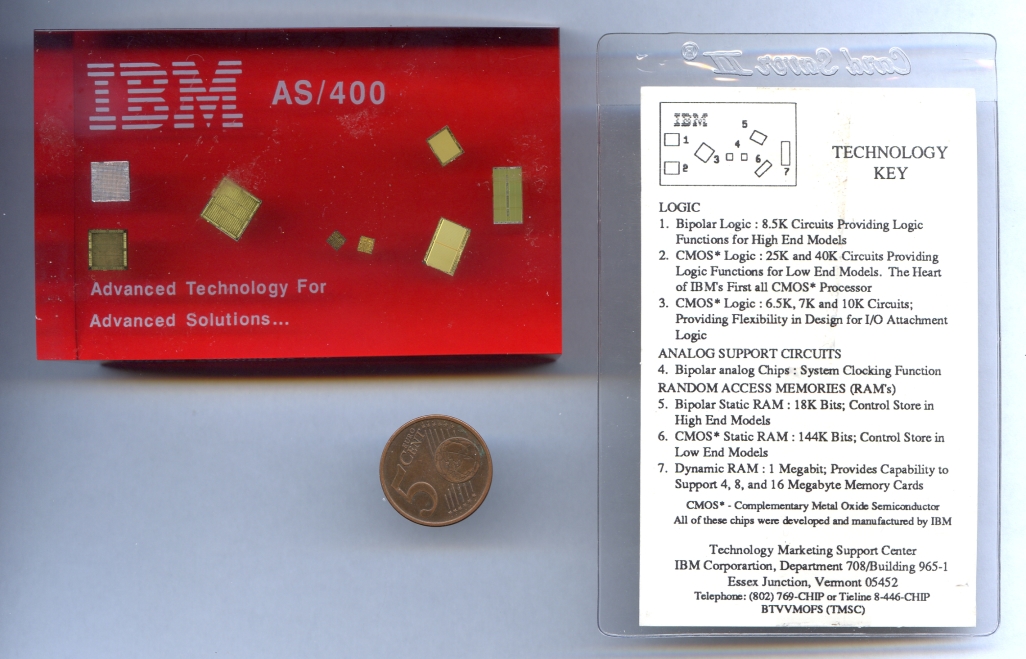

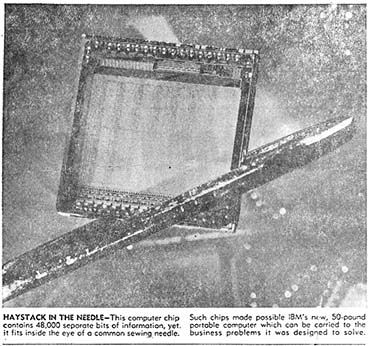

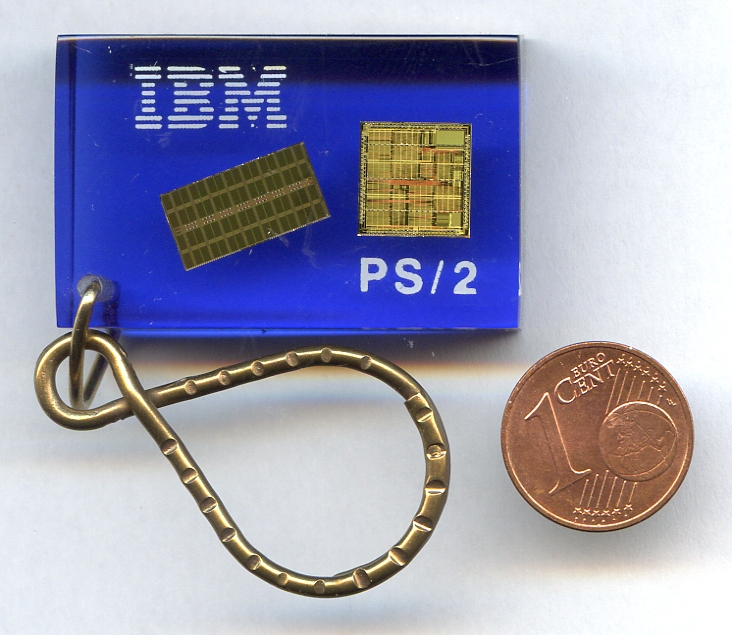

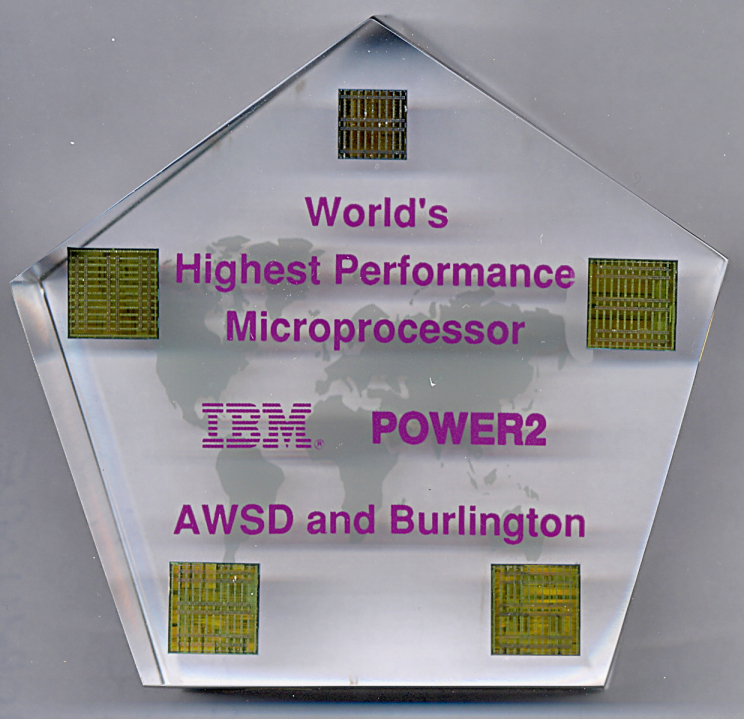

I hope this page can give a vivid view of many different technologies developed, improved and widely used by Big Blue, aka IBM, through the years. IBM "objects" are often little more than a mystery or merely a guess for the collector, given the lack of viable technical infos about their inner guts and workings at the ground (physical) level. Nonetheless IBM hardware always fascinated me because it's the expression of an enormous work of Research & Development: I started my IBM collection 20 years ago and I have many more items -complete systems, parts, boards, chips, manuals- not yet photographed nor listed here. IBM pioneered a number of different fields that are now all key parts of our common concept of "computer": CMOS circuitry and memories, hard disks, networking and so on. Last but not least the PC in itself, with a lot of related standards, most of which were once ubiquitous, is a creation of IBM engineers. Example: when You're storing something on your multi-TB HDD, remember that IBM invented the hard disk (IBM RAMAC)! Sorry, the items are un-categorized and un-sorted but You can try these shortcuts to some nice CPU listed here (don't miss the rest of the page...): POWER-2 CPU chips in lucite, 4331 CPU card, 4341 CPU card, 4381 MCM, System/38 A700 CPU, 9021 TCM, ES/9000 9021 TCM, ES/9000 9121 TCM, S/390 9672 TCM, z900 MCM, S/390 Multiprise CPU module, unknown but **nice** IBM prototype board, PS/2 Model 90 CPU Complex Type 0. Here You can see a promotional AS/400 lucite paperweight with embedded chips here. The ATX-4 technology used in the IBM ES/9000 mainframe CPU's bipolar chips is illustrated by this lucite paperweight. Don't miss the 1st 1 Mbit DRAM chip made commercially available by IBM. The 3370 disk drive control electronic is a nice example of the once ubiquitous (in IBM products I mean) MST technology, and here is a wafer of MST chips. The 3740 Data Entry System CPU card shows alot of old styled 40-pins white DIPs. Also in the page there are several nice examples of exotic IBM chip packages. More IBM items are scattered through the site so check the other pages if You are interested.

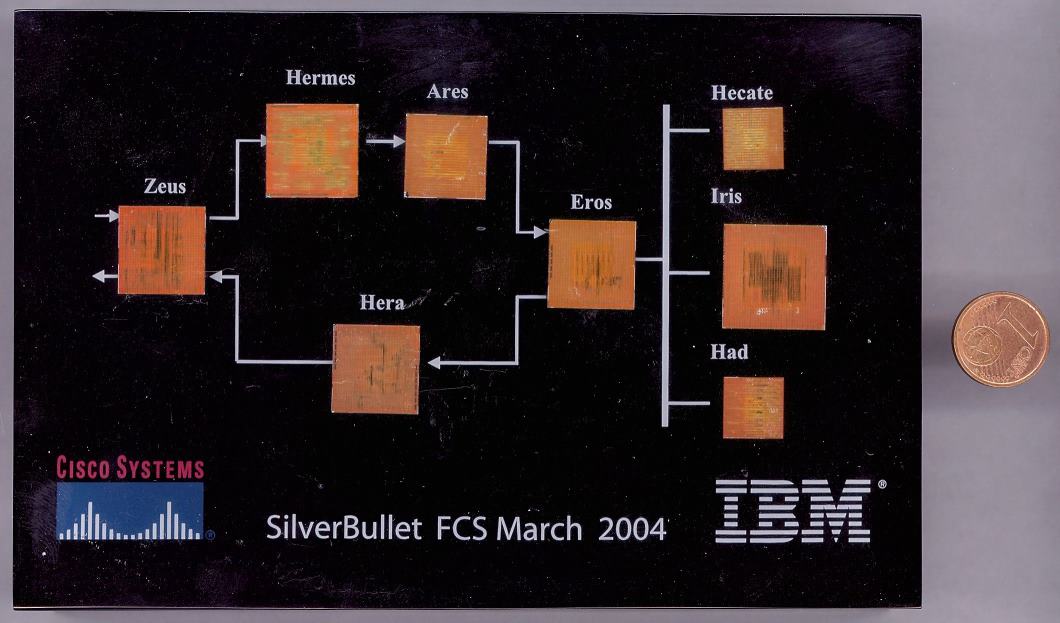

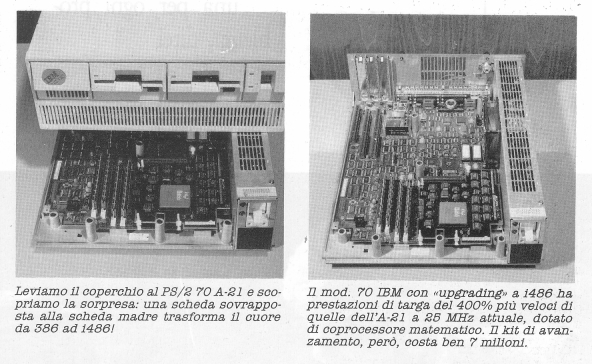

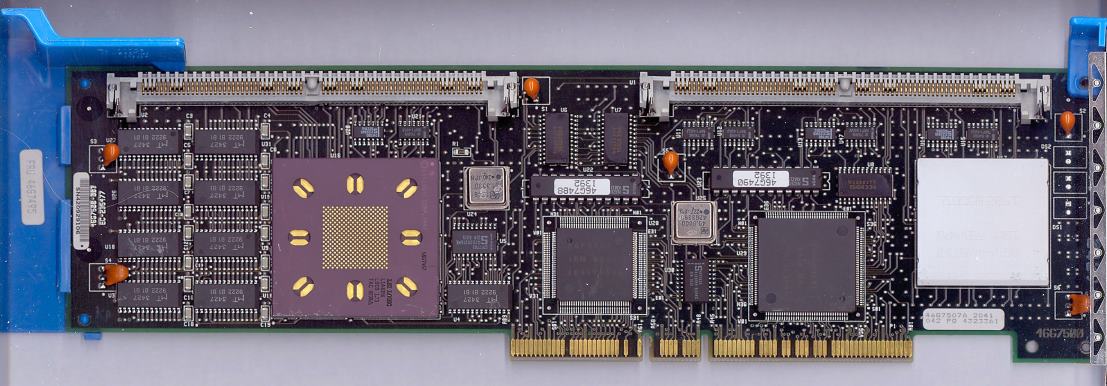

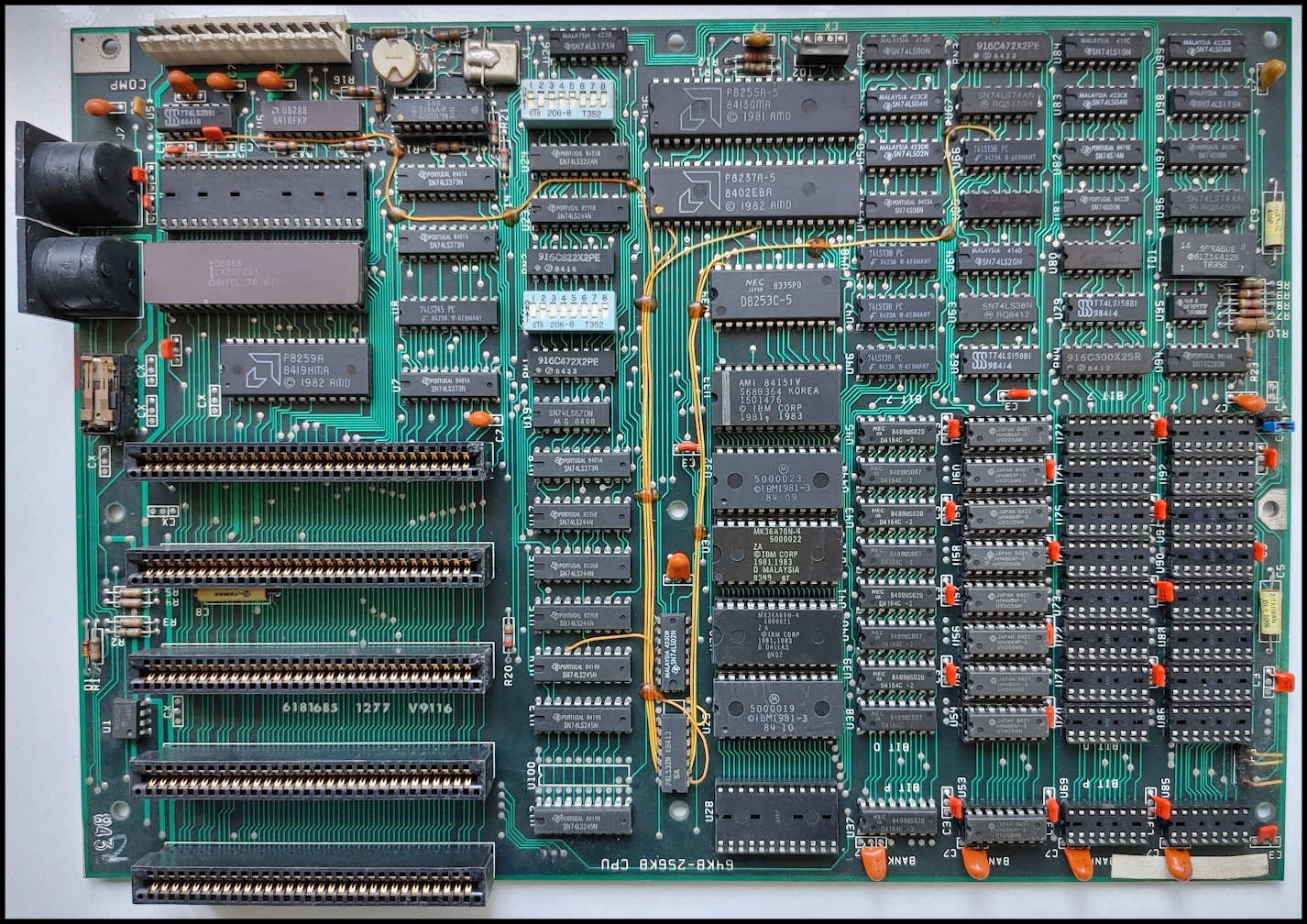

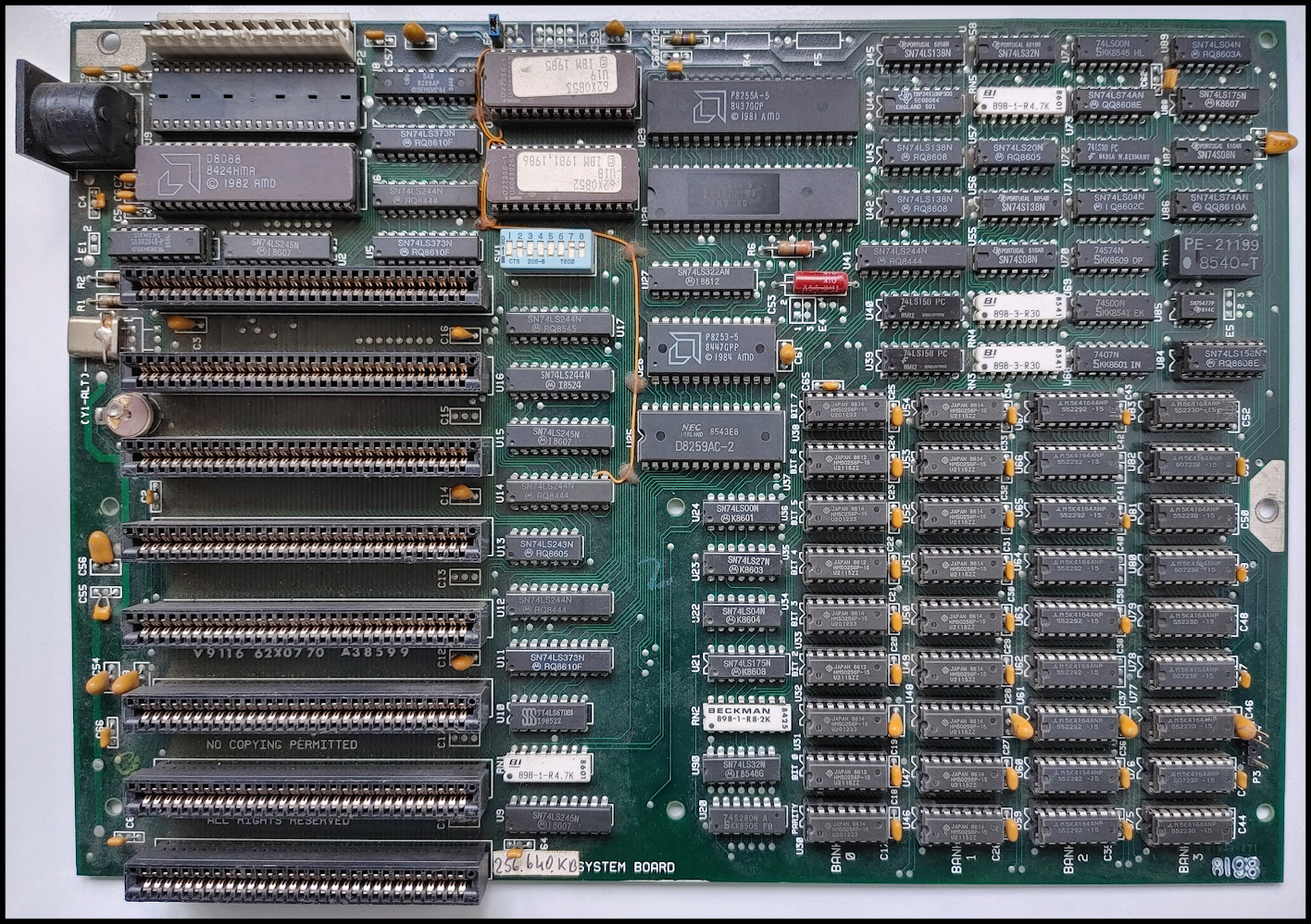

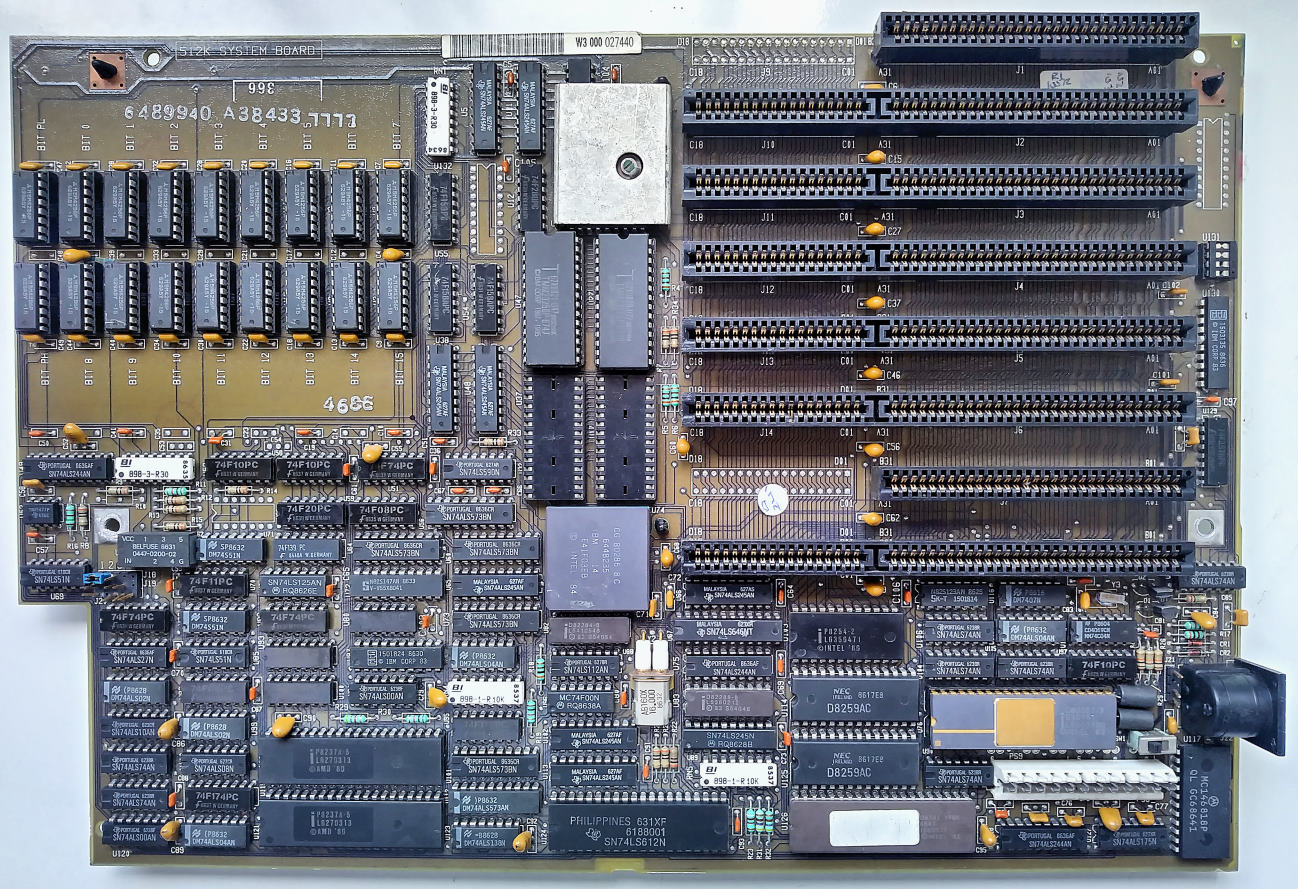

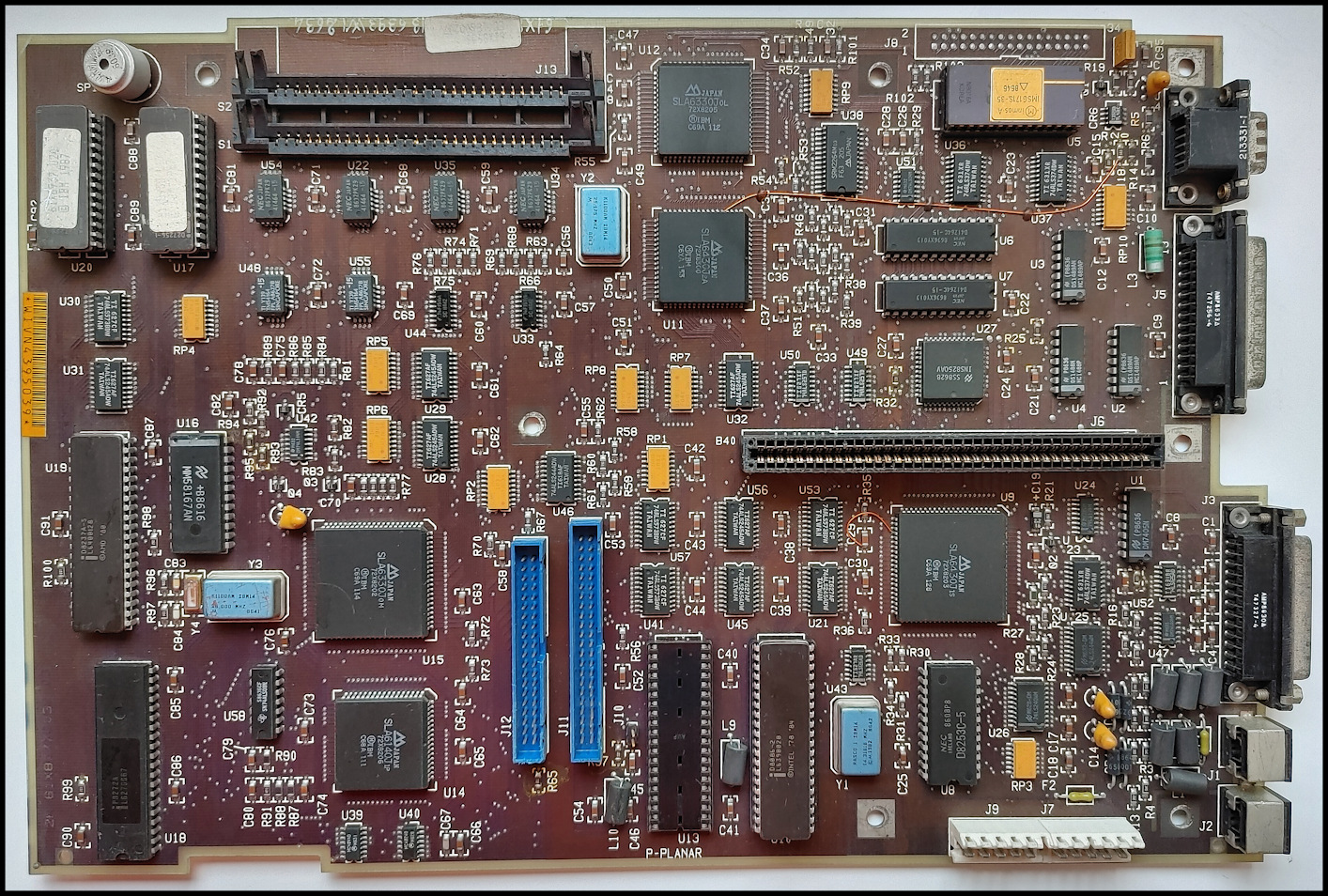

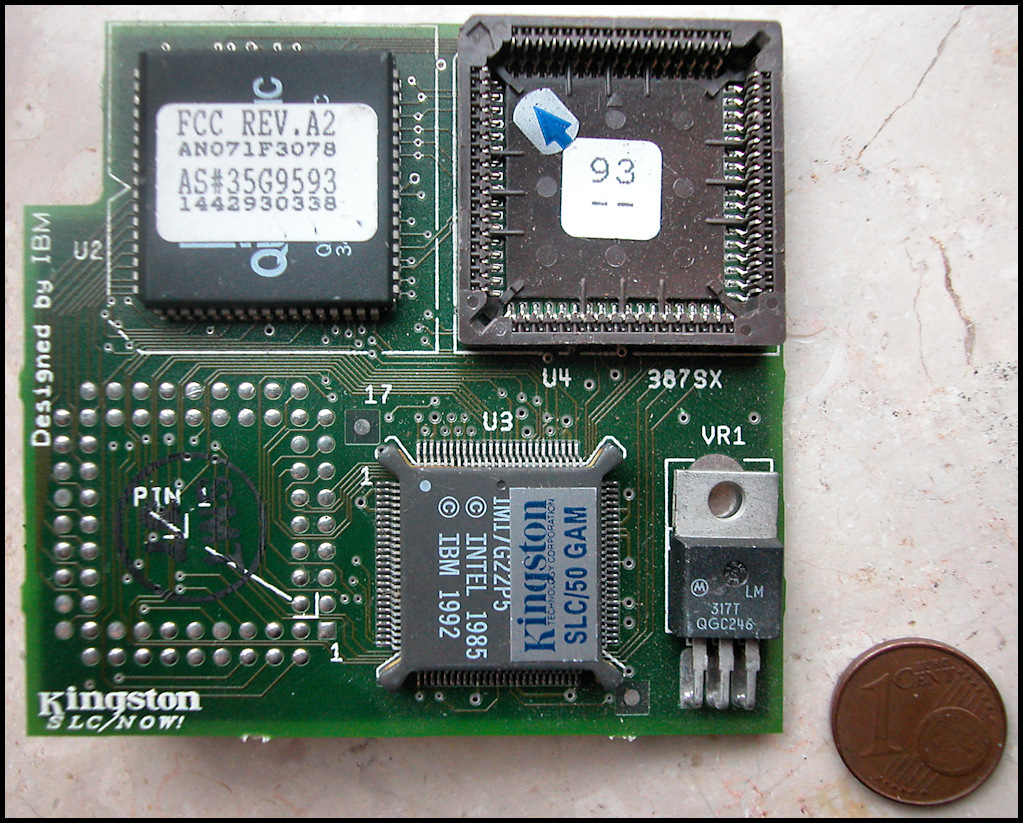

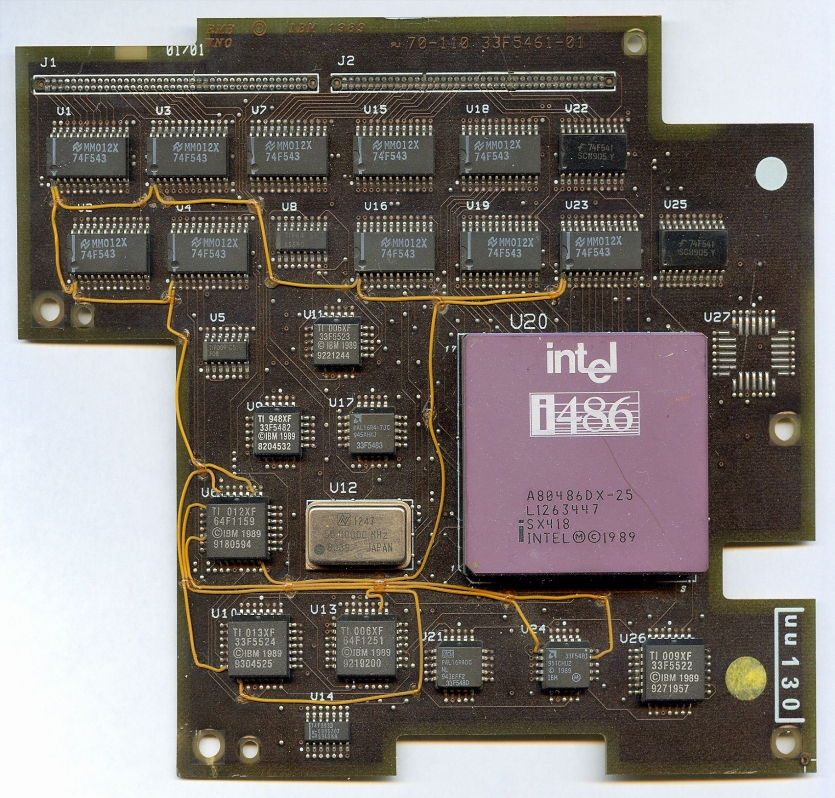

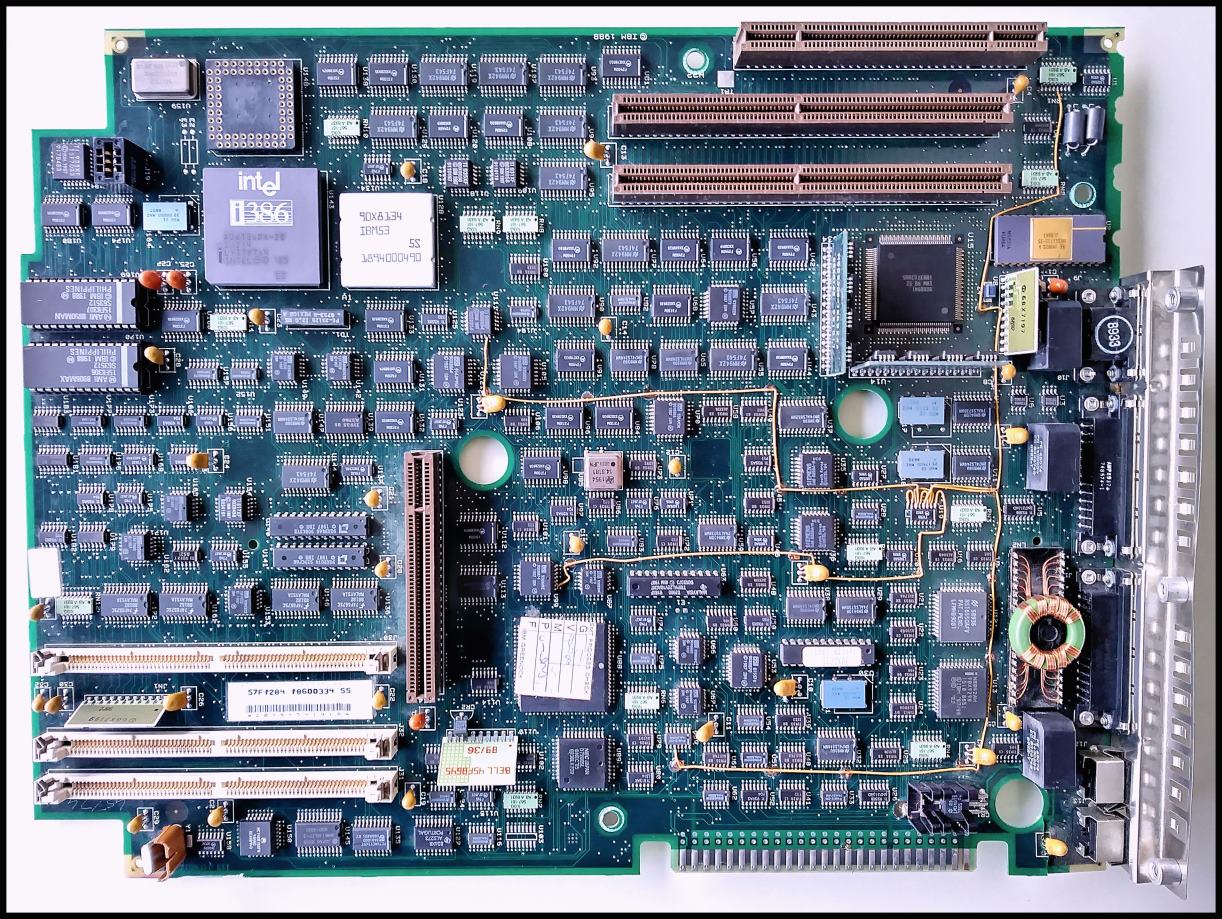

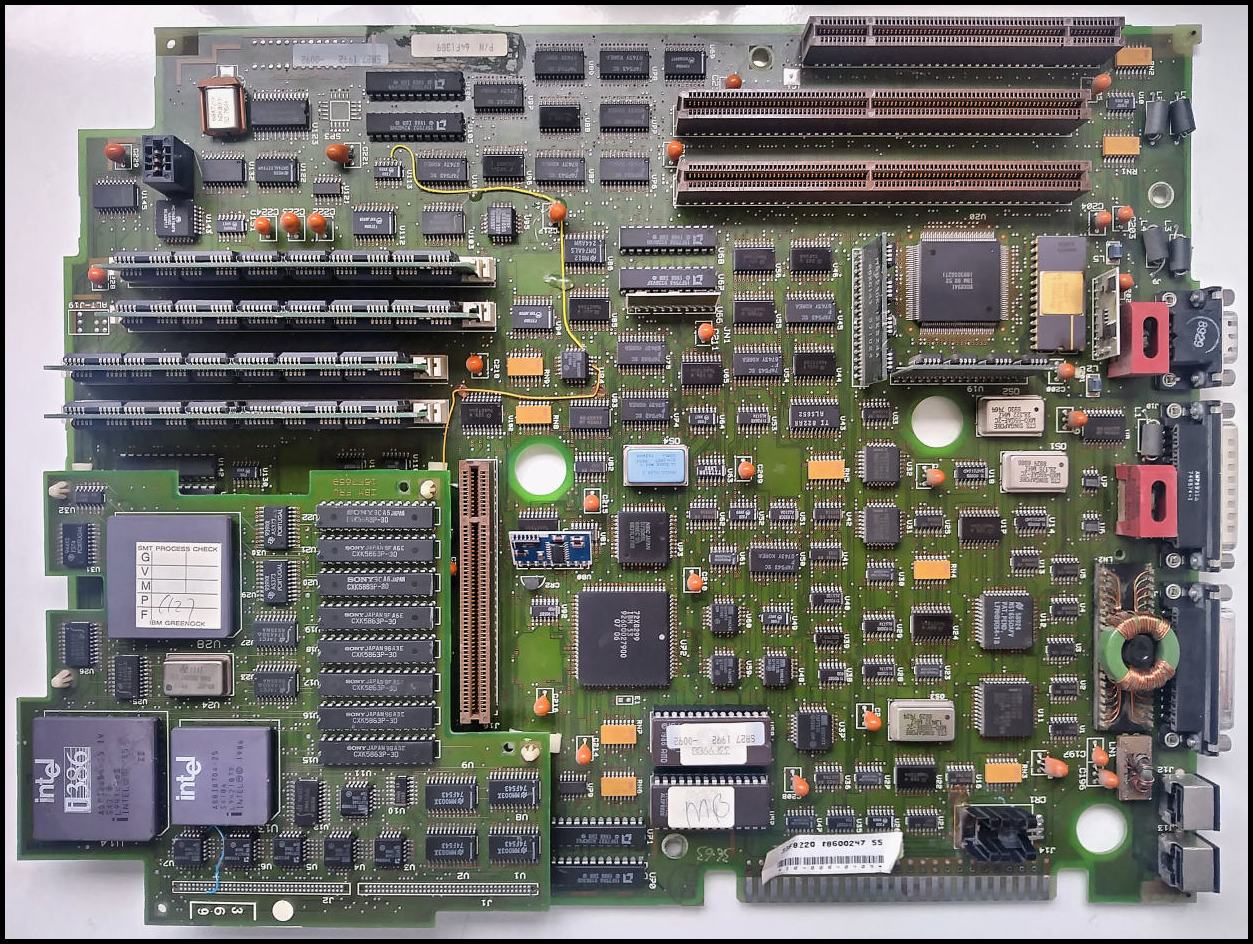

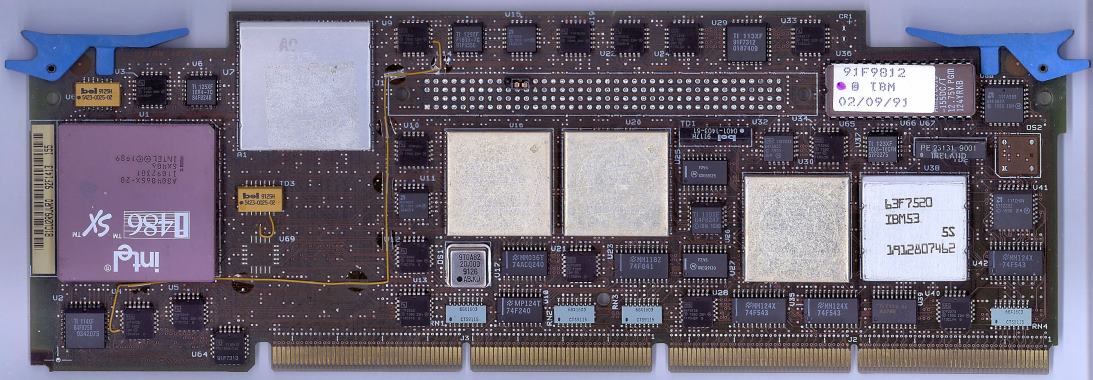

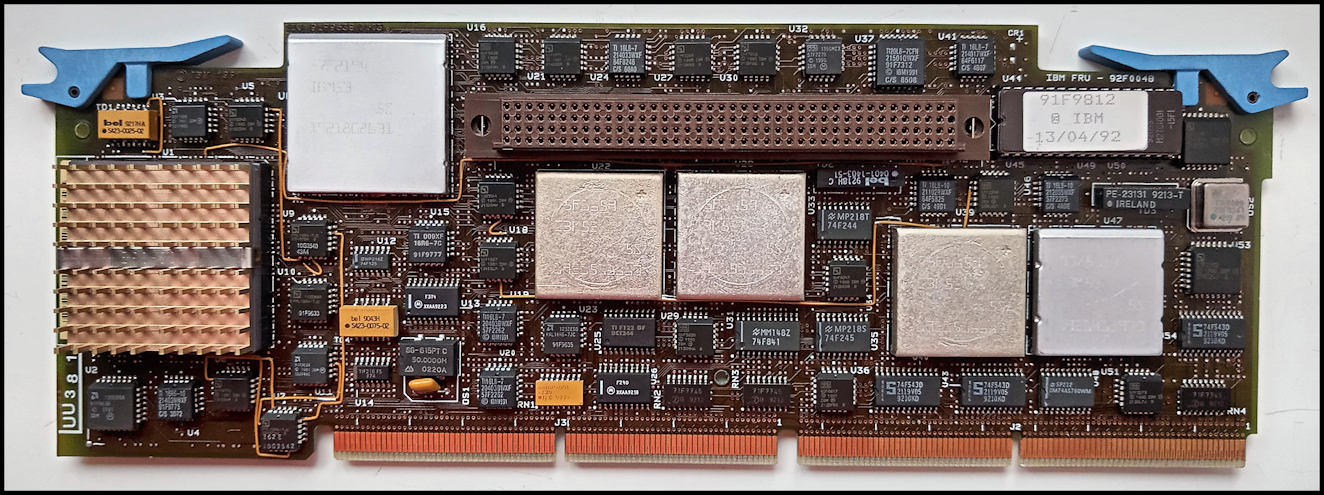

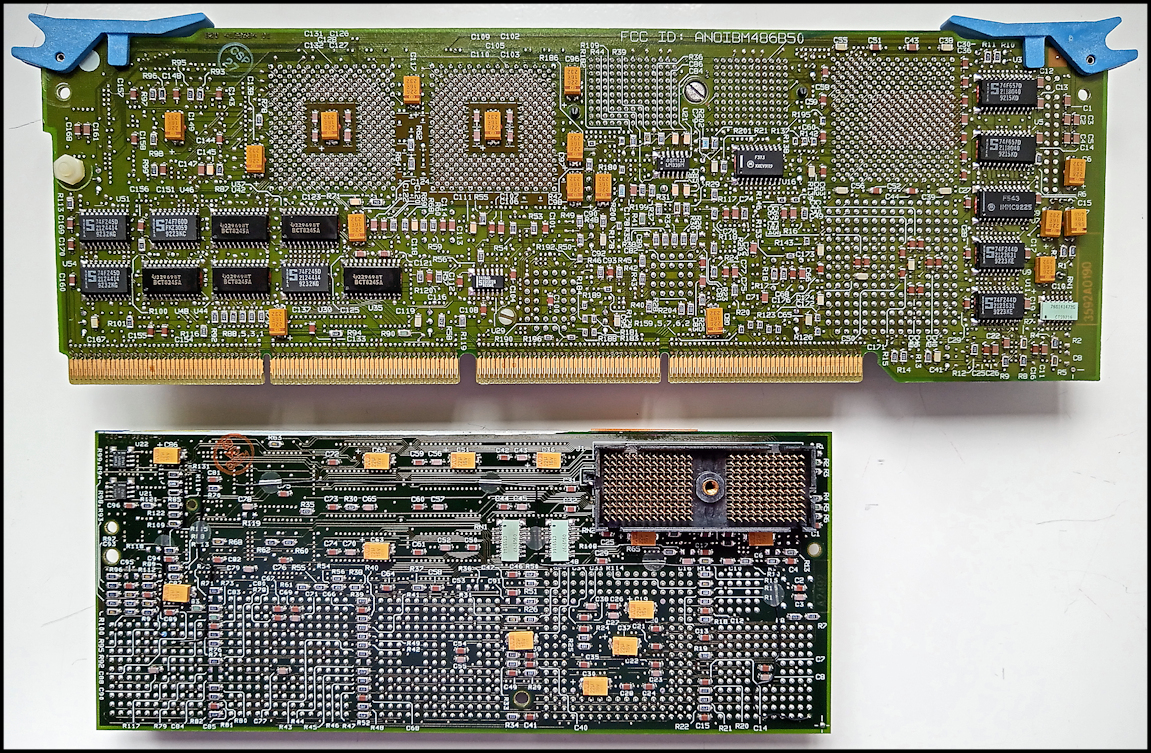

Principali novità e modifiche (dal 1.1.2020): 16 MBit DRAM chip, experimental thin-film Cryotron, Bromont plant paperweight, 360/195 card with TI chips, 370/145 MST card, Burlington Memory Systems Division paperweight with DRAM 4-chips module, System/38 keychain with logic chip, 4300 family keychain with logic chip, Silver Bullet chipset made by IBM for Cisco Systems, prototypes of IBM FET gate arrays, Displaywriter memory card, Displaywriter CPU Card, Personal/370 MCA card, PC/AT 5170 motherboard, PS/2 Model 70 E61 motherboard, PS/2 70 Model A21 motherboard, Livermore model B acoustic coupler with IBM part number, IBM GPD paperweight with 32- and 64-kbit DRAM chips, IBM GTD paperweight with MOS memories, IBM 8 Mbit DRAM pin, IBM PC RT 6150 AFPA option card, PS/2 9595 CPU Complex Type 3 M, PS/2 CPU complex Type 1 Upgraded to 486DX-50, POWER5 8-way MCM, RS64 A10 Cobra prototype, IBM paperweight with SLT modules in different steps of production, VTL-style card with AMS 6001 1 kbit DRAMs

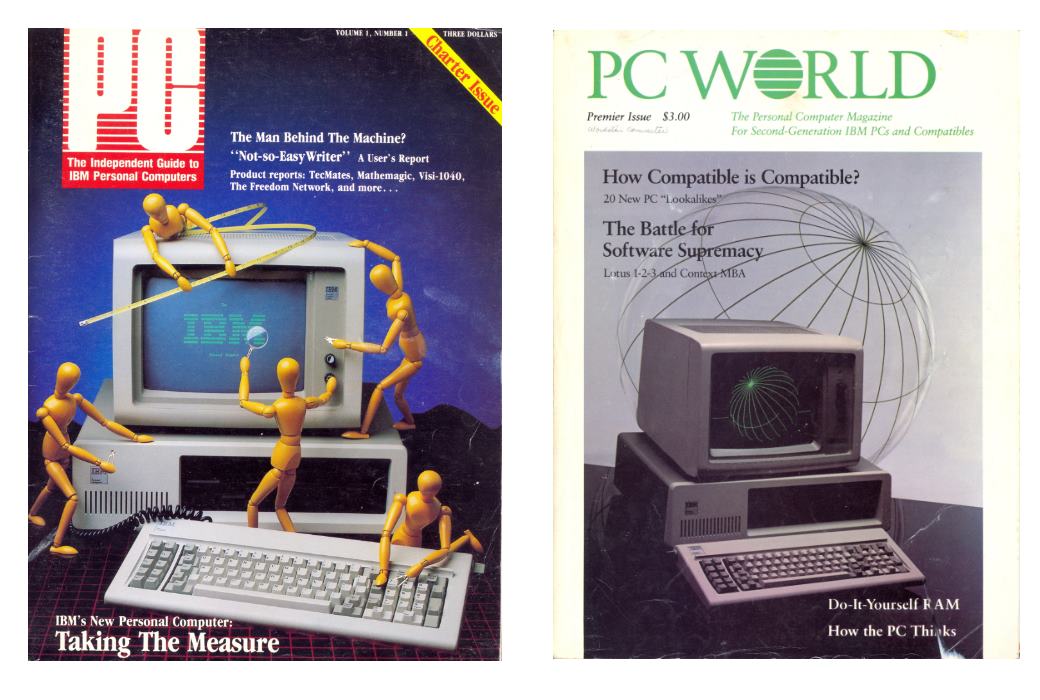

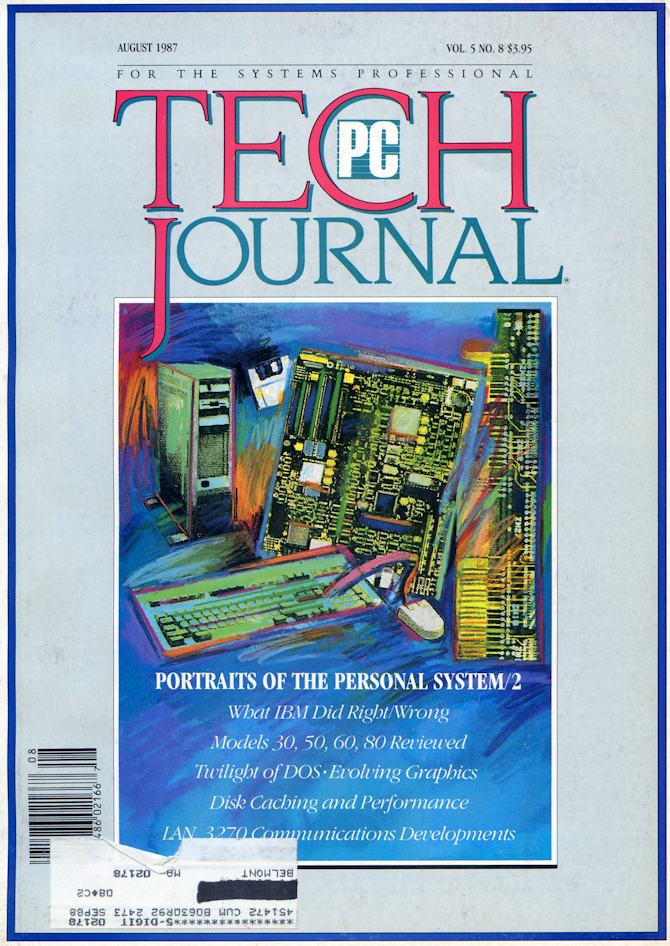

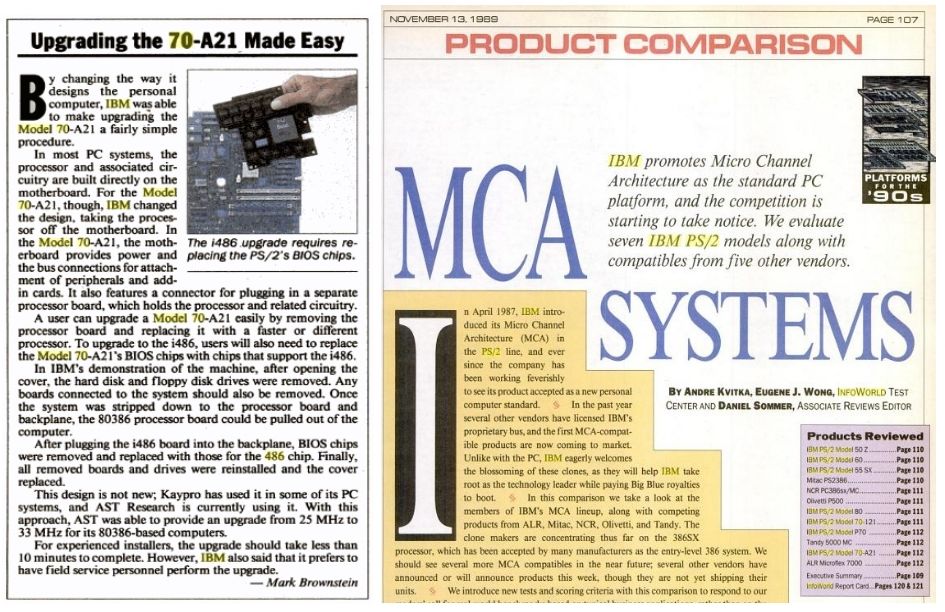

I primi numeri di due famose riviste di informatica personale dedicate a quello che forse è stato il prodotto IBM che più ha influenzato l'informatica moderna, il PC. A sinistra il numero iniziate di PC Magazine (Gennaio 1982), a destra il numero di lancio di PC World (Febbraio/Marzo 1983).

Numero della rivista PC Tech Journal, Dicembre 1984, dedicato alla presentazione del PC AT di IBM.

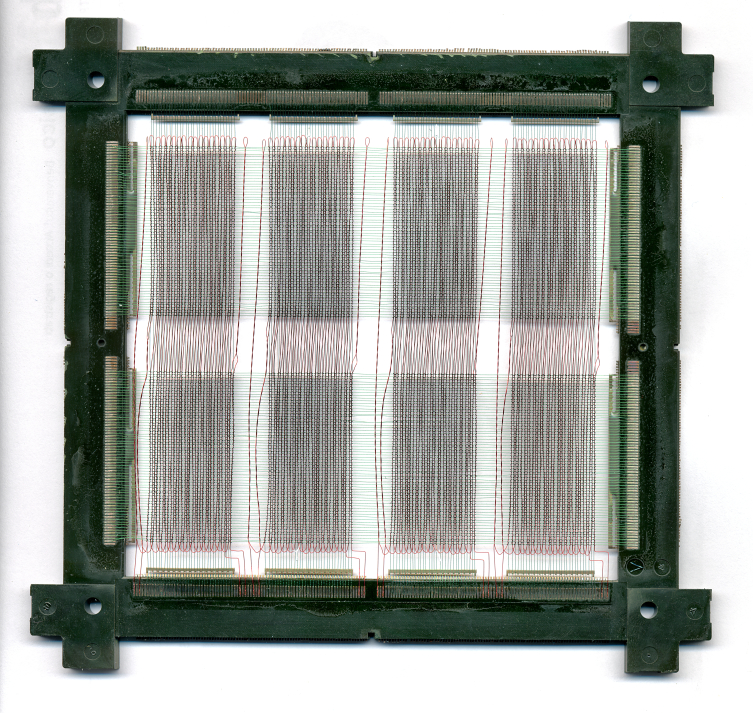

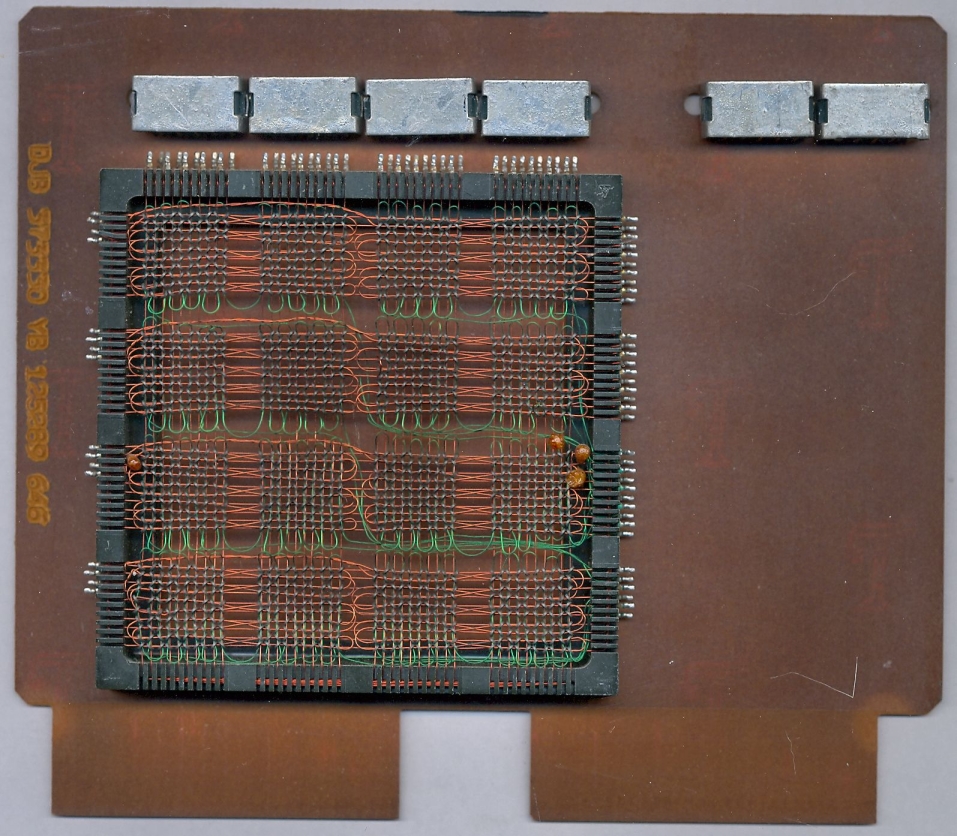

Parte della memoria a nuclei magnetici di un IBM System/360 Mod. 30 (1964), uno dei membri più piccoli della famiglia 360. Questa macchina (vedi: http://www-03.ibm.com/ibm/history/exhibits/mainframe/mainframe_PP2030.html) aveva una frequenza di clock di 1,33 MHz ed una capacità massima di memoria di 64 KB (http://ed-thelen.org/comp-hist/ibm-360-30.html). Venne prodotta fino al 1970. La maggior parte delle installazioni era dotata di 32 KB di memoria; all'inizio degli anni Settanta la FabriTek incominciò ad offrire un sottosistema di memoria a nuclei fabbricato in proprio che consentiva di espandere la RAM fino a 128 KB. Il 360/30, offerto come conveniente upgrade ai clienti IBM che già possedevano una macchina della serie 1401, era il più piccolo (cioè meno potente ed espandibile) membro della famiglia 360 a supportare completamente l'API 360; il 360/25 ed il 360/20, inferiori come prestazioni e caratteristiche hardware, avevano anche un diverso set di istruzioni.

Vedi: http://www.ljw.me.uk/ibm360/; http://en.wikipedia.org/wiki/IBM_System/360_Model_30.

Una memoria simile a questa è visibile qui: http://www.thegalleryofoldiron.com/MISC.HTM.

More cores here!

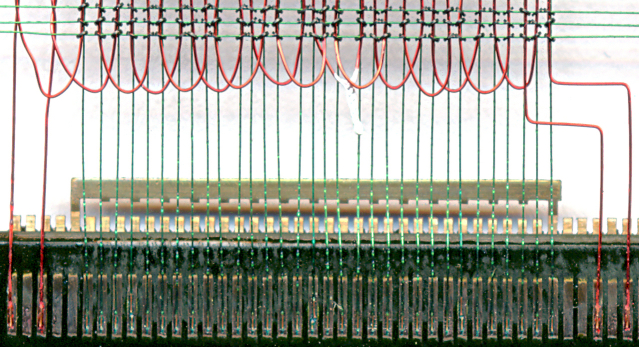

Dettaglio della memoria a nuclei magnetici dell'IBM 360/30 riprodotta sopra. L'organizzazione è del tipo a tre fili (three-wire): due per la scrittura (verdi) ed uno per la lettura (arancione). La capacità del singolo piano di memoria dovrebbe essere di 2.048 bit (2 Kbit: http://www.flickr.com/photos/pchow98/4012289798/). Queste memorie erano fabbricate direttamente da IBM. Sulla memoria a nuclei magnetici: http://en.wikipedia.org/wiki/Magnetic_core_memory.

Vedi: http://ibm-1401.info/IBMCoreArraysIEEEMagnetics1969.pdf (Ferrite Core Planes and Arrays: IBM's Manufacturing Evolution)

Piccola memoria a nuclei magnetici su scheda IBM in formato SMS (Standard Modular System) a doppia altezza, 1966. La capacità totale è di 1.600 bit. Questa memoria, assieme ad altri moduli dello stesso tipo, era impiegata come buffer della capacità complessiva di 4 kword nell'Integrated Control Unit IBM 2821 per 1-3 stampanti IBM 1403, un fortunatissimo e longevo modello di chain printer originariamente associato al calcolatore IBM 1401 e poi utilizzato anche con la famiglia System/360, ed uno o più lettori/perforatori di schede IBM 2540. Com'è noto, lo standard SMS venne introdotto dalla IBM nella seconda metà degli anni Cinquanta, inizialmente per il mainframe 7030 (Stretch), poi per i calcolatori 1401 e 1620. Sorpassato nel 1964 dalla tecnologia SLT (Solid Logic Technology), esso è rimasto in uso per molto tempo, fino alla metà circa degli anni Settanta, in un gran numero di periferiche (ad esempio le unità nastro IBM 240x coi relativi controller, la stampante IBM 1403, l'ICU IBM 2821, il lettore/perforatore di schede IBM 2540 e altri). In alcuni modelli della famiglia System/360 erano a loro volta presenti schede SMS con moduli SLT (un esempio è visibile in questa pagina del sito). I moduli SMS si basano su un circuito stampato a singola faccia, con le tracce che si trovano dal lato opposto rispetto ai componenti. Le dimensioni sono 2,5 per 4,5 pollici (singola altezza) e 5,375 per 4,5 (136,5 x 110 mm, doppia altezza); il connettore è a 16 contatti, identificati dalle lettere comprese tra A ed R, saltando la I e la O, sul primo o sull'unico connettore e dalle lettere da S a Z e dai numeri 1-8 sull'eventuale secondo connettore (in un modulo a doppia altezza). Il tipo di modulo è identificato da un codice letterale a 2, 3 o 4 lettere. Nel corso degli anni IBM ha prodotto un gran numero di tipi di schede SMS, qualche centinaio, in relazione al proliferare delle famiglie logiche utilizzate (RTL, DTL, ECL). Ad esempio l'IBM 1401 era basato su una "mescolanza" di circuiti logici DTL, chiamati CTDL nel gergo di Big Blue, RTL (CTRL nello stesso gergo) e "alloy", ovvero circuiti analogici realizzati con transistor in lega (alloy, appunto). Vennero successivamente introdotti moduli basati su una versione migliorata dell'originaria logica DTL, noti come SDTDL, basati su transistor di tipo "drift". Ciascun modulo logico SMS ha una complessità paragonabile a quella di un singolo integrato TTL SSI della famiglia 74. L'ICU IBM 2821 è rimasto in uso fino agli anni Ottanta, associato spesso a macchine della famiglia 370.

Vedi: http://media.guap.ru/960/del_popolo.pdf (articolo molto interessante)

Vedi: http://bitsavers.trailing-edge.com/pdf/ibm/28xx/2821/GA24-3312-9_2821_Unit_Description_Oct82.pdf.

Una memoria identica: http://www.computermuseum.li/Testpage/Core-Memory-1960s.htm.

Foto della parte elettronica dell'IBM 2821: http://www.baltimoresun.com/business/bal-bs-bs-bz-baltech-cum20100802081034,0,2859273.photo.

Anche: http://www.foxdata.com/blog/?tag=ibm-360 (è visibile una scheda identica a queste).

Anche: http://www.newbegin.com/html/misc__item_detail_23.html (presenta la scheda come parte dell'IBM 1401).

Anche: http://www.radiomuseum.org/museum/d/haus-zur-geschichte-der-ibm-datenverarbeitung-sindelfingen/.

Anche: http://ibmcollectables.com/gallery/album26.

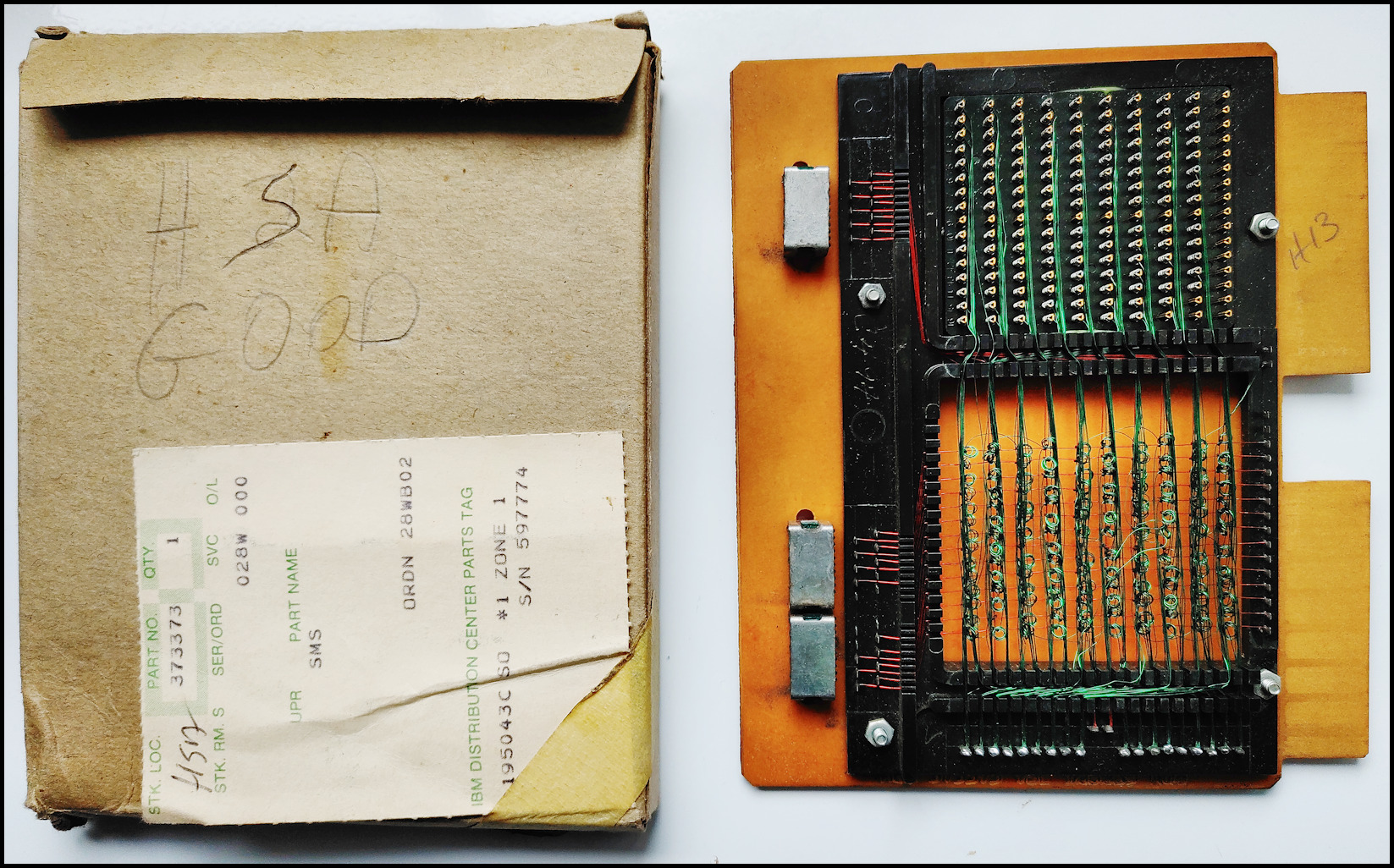

Memoria ROM a nuclei magnetici su scheda in formato SMS (circa 1970), con il suo contenitore originale, molto probabilmente si tratta di un ricambio per un controller di periferiche IBM 2821. Le memorie ROM a nuclei erano utilizzate come memorie di caratteri o memorie di controllo in una varietà di applicazioni, in luogo di altri tipi di ROM (es. a matrice di diodi), prima dell'avvento delle moderne ROM a circuito integrato.

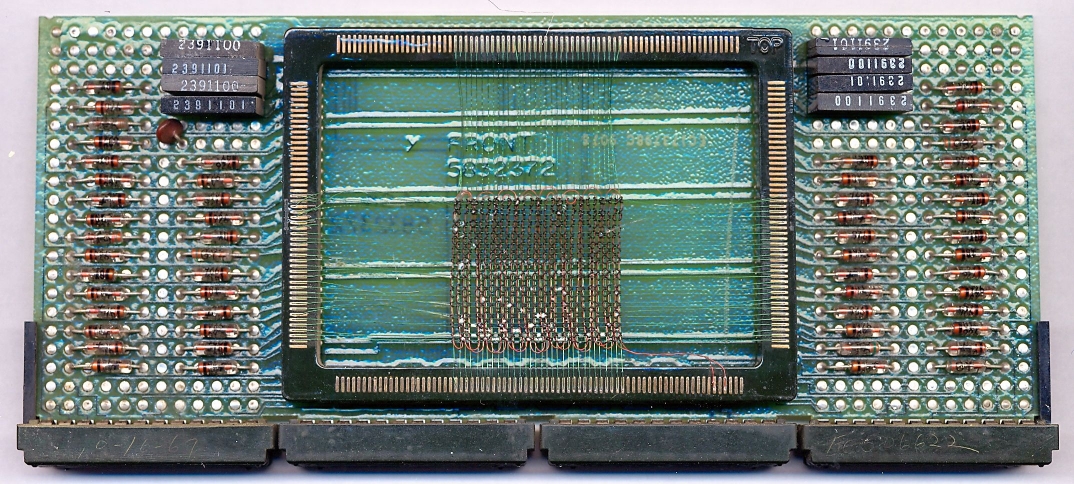

Piccola memoria a nuclei magnetici su scheda IBM in formato SLT-quad, 1967 (vedi data in basso a sinistra, 6-11-67). Non sono riuscito ad identificare la macchina dalla quale proviene, né lo sapeva chi me l'ha venduta su Ebay. Potrebbe essere la memoria di un printer controller.

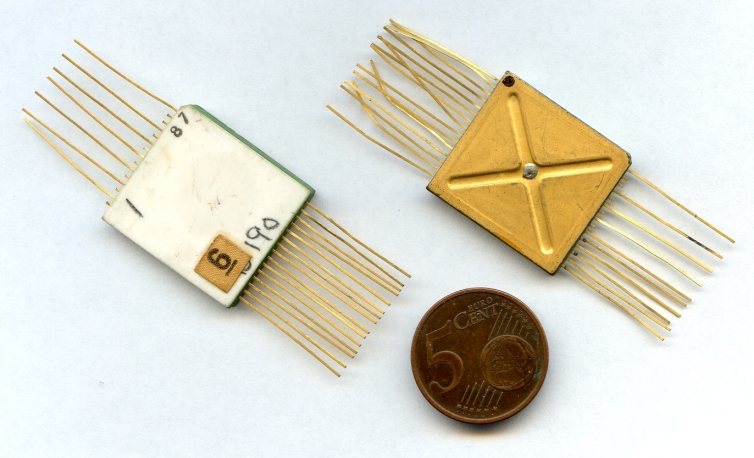

3.3.2015 - Questi due componenti, in apparenza circuiti ibridi (non è visibile alcuna indicazione del fabbricante) provengono da un lotto di materiali messi in vendita da un ex ingegnere IBM, secondo il quale erano impiegati nella memoria di un calcolatore militare fabbricato proprio da IBM. L'epoca di produzione dovrebbe corrispondere alla fine degli anni Sessanta.

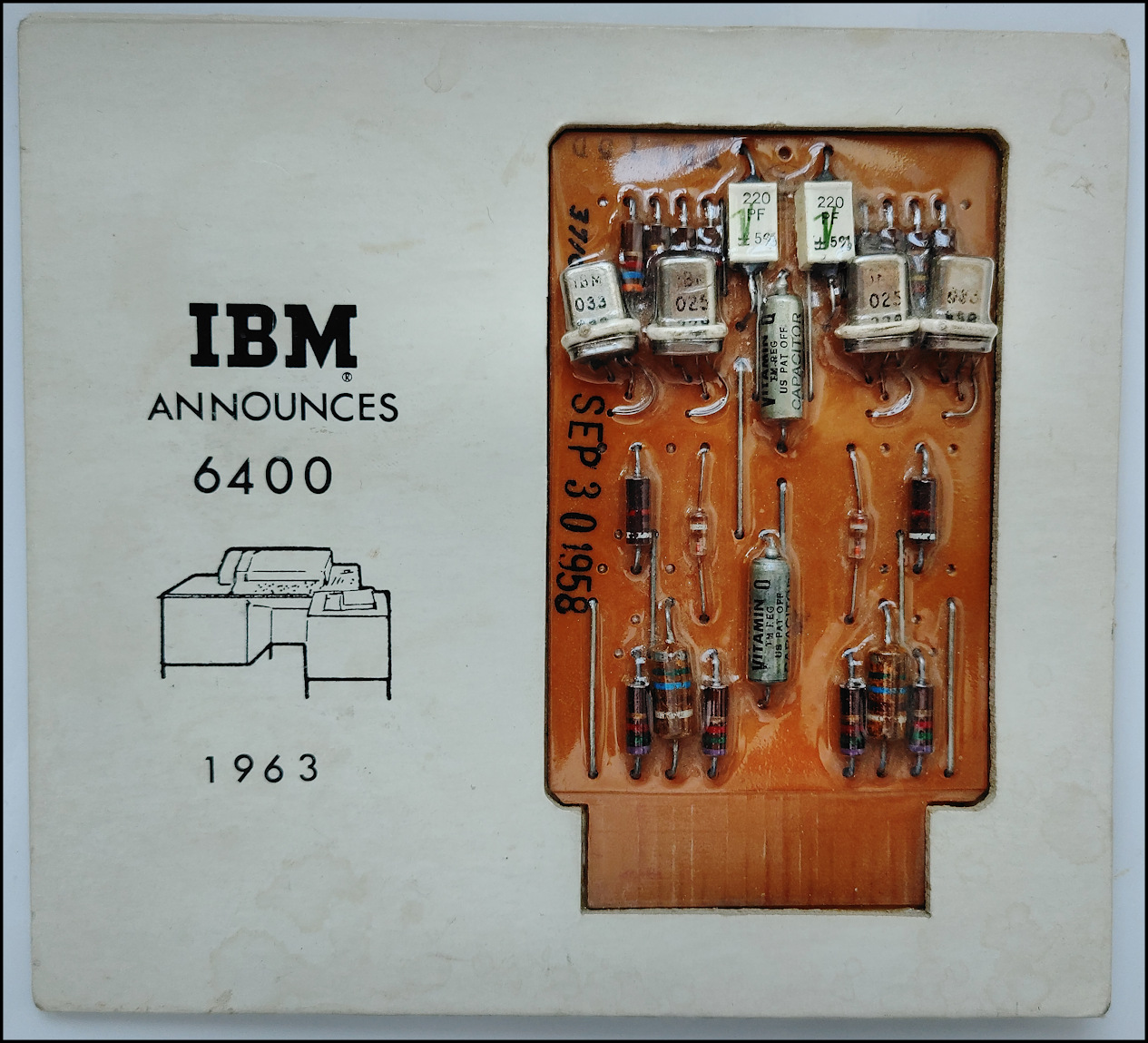

Cartolina pubblicitaria IBM del 1963 che annuncia l'introduzione della macchina contabile elettronica modello 6400 (vedi). Contiene una scheda SMS molto vecchia, del Settembre 1958 (questa tecnologia venne in effetti introdotta alla fine degli anni Cinquanta) con transistor siglati IBM.

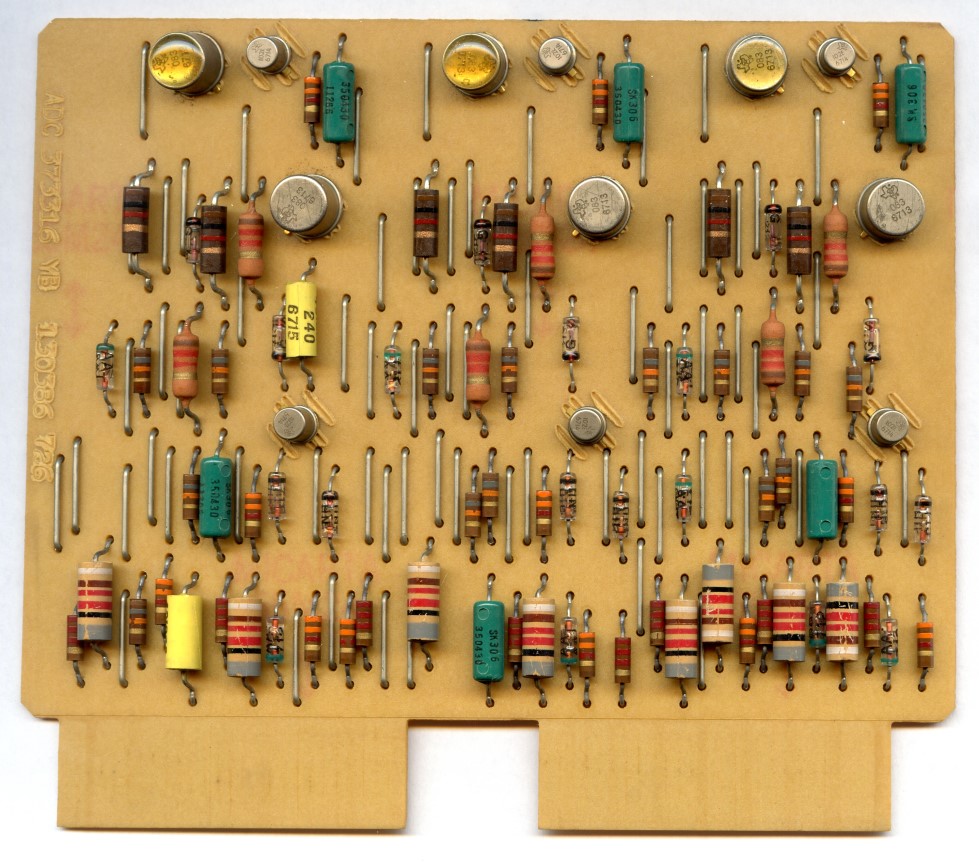

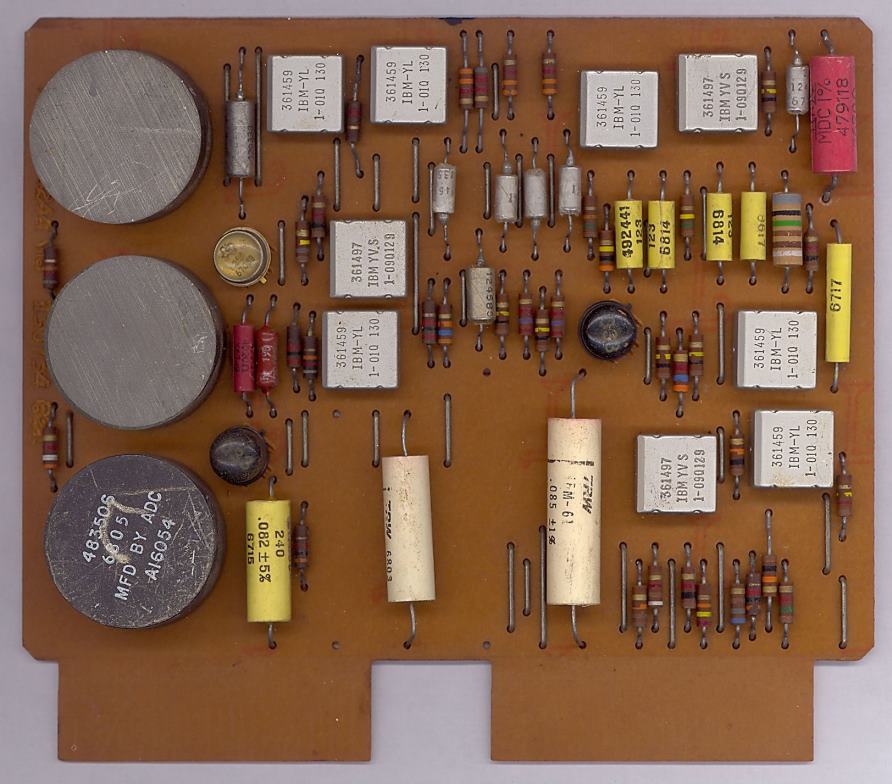

Modulo IBM SMS (Standard Modular System) a doppia altezza, 1967, con 12 transistor Texas Instruments ed altri componenti discreti. I moduli SMS impiegavano un tipo di circuito stampato ad una sola faccia; ulteriori connessioni erano rese possibili da collegamenti punto-a-punto fatti con filo di Rame. I segni che si vedono in corrispondenza dei piedini dei transistor servivano durante il montaggio (automatizzato) dei componenti per l'allineamento degli stessi. La tecnologia SMS, introdotta con la seconda generazione di calcolatori IBM -in particolare con il 7030 "Stretch"-, è sopravvissuta molto a lungo, fino all'inizio degli anni Settanta. Questo perché molte periferiche originariamente sviluppate per i computer quali quelli della Serie 1400 hanno avuto un ottimo successo commerciale rimanendo in uso, con poche modifiche, anche con i calcolatori delle successive generazioni (System/360 e /370). Buoni esempi sono la stampante 1403 ed il lettore/perforatore di schede 2540. In questi casi non si è avuta una transizione alle più recenti tecnologie SLT ed MST. Come si vede in questa pagina del sito esistono anche schede SMS con moduli SLT. Le dimensioni delle schede SMS a doppia altezza sono 5,375 per 4,50 pollici, con un doppio connettore di backplane a 32 linee totali (16+16), contrassegnate con le lettere A-R nel primo blocco (non vengono impiegate la I e la O) ed S-Z, più i numeri 1-8, nel secondo. Il backplane non impiega circuito stampato bensì connessioni punto a punto con filo (wire wrap). Si stimano in oltre 2500 i tipi di schede SMS complessivamente prodotti da IBM: secondo i piani iniziali avrebbero dovuto essere molti di meno, non più di 200, ma il loro numero è cresciuto con l'incorporazione di più famiglie logiche (RTL, DTL, ECL) e circuiti analogici di varia natura.

Vedi: http://static.righto.com/sms/index.html (SMS Card Database), http://ibm-1401.info/IBM-SMS-Cards-Coslet.html.

Scheda SMS a doppia altezza (1968) contenente transistor discreti e moduli SLT.

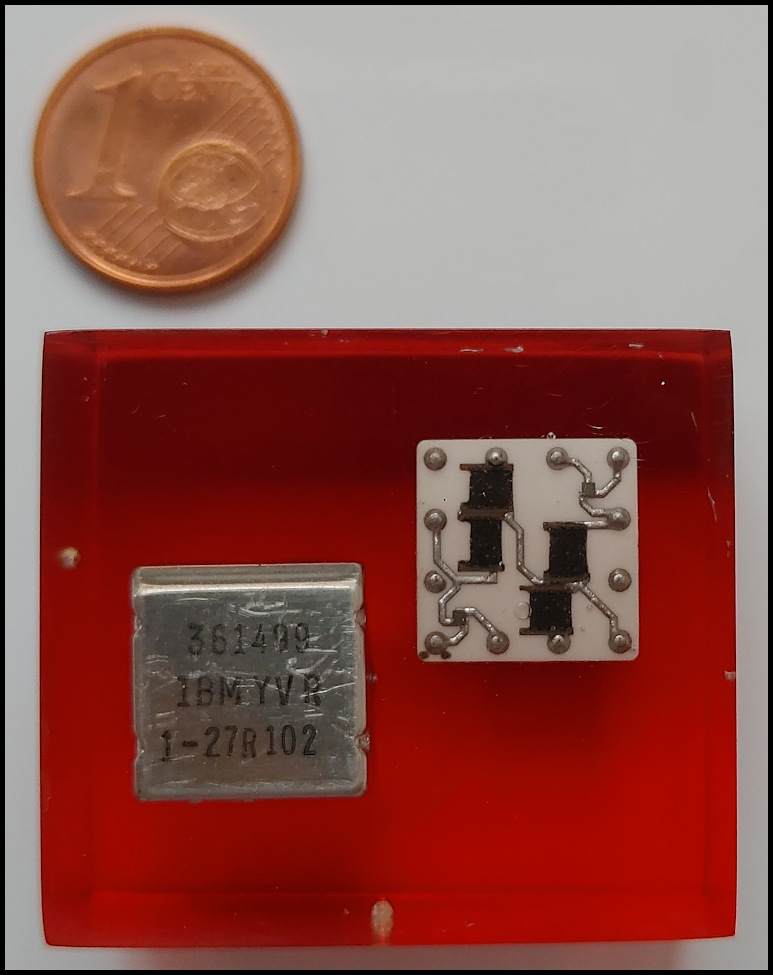

Piccolo gadget promozionale IBM contenente un modulo SLT aperto (primi anni Settanta).

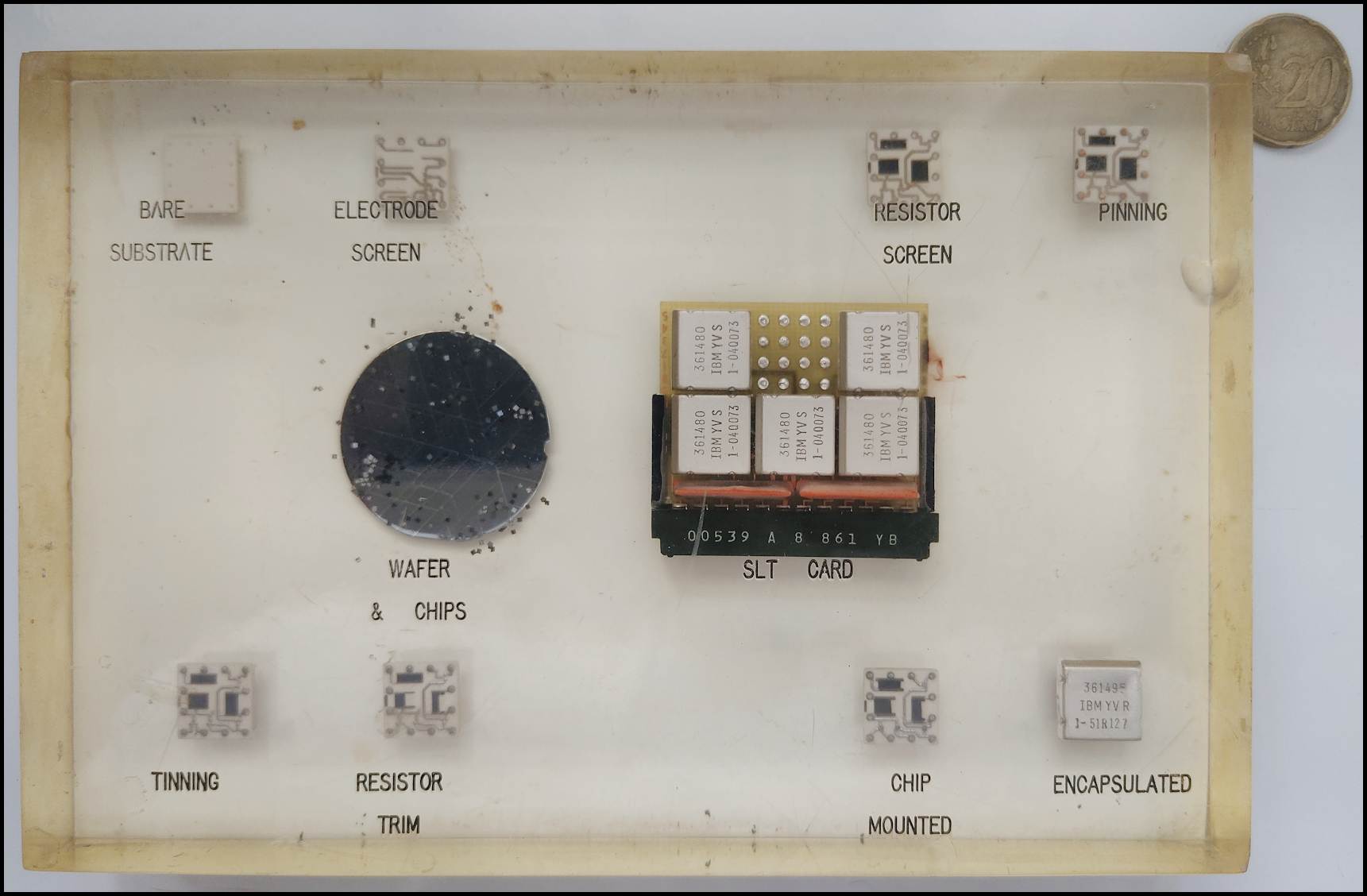

Questo fermacarte in plexiglass (circa 1965) illustra i vari passaggi del processo produttivo dei moduli SLT: dal wafer di 2'' di diametro che viene tagliato in singoli transistor della dimensione di pochi decimi di millimetro (al centro a sinistra), alle diverse fasi realizzative dei resistori e delle interconnessioni, ottenuti con tecnica fotolitografica (in alto e poi in basso, da sinistra verso destra), fino al modulo completo ed alla scheda pronta per essere montata sul backplane (al centro a destra). All'epoca la tecnica SLT, pur basandosi su circuiti logici ibridi anziché integrati monolitici, consentiva di ottenere una densità circuitale superiore a quella di tutte le macchine di seconda generazione a transistor discreti.

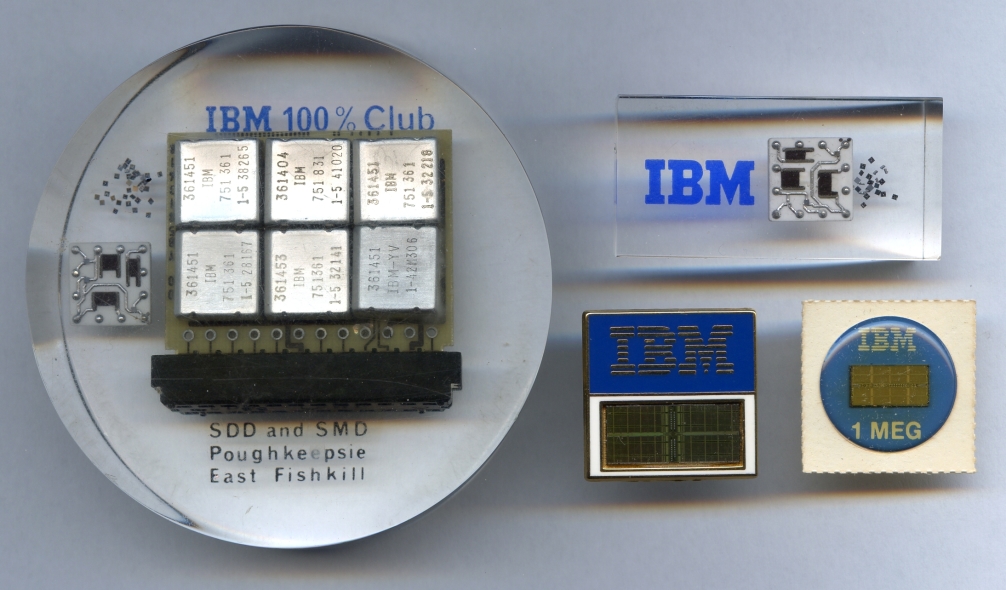

1.10.2014 - Alcuni esempi di materiale pubblicitario IBM. A sinistra, un fermacarte in plexiglass contenente una scheda SLT, un modulo SLT ed alcuni transistor impiegati in questo tipo di circuiti: fa riferimento alla System Development Division (SDD), presso gli impianti IBM di Poughkeepsie, ed alla System Manufacturing Division (SMD) di East Fishkill (entrambe nella Contea di Dutchess, Stato di New York, USA). Un esemplare identico è visibile in dettaglio in questa pagina. Entravano a far parte del "100% Club" erano tutti quei rivenditori di hardware che riuscivano a raggiungere o a superare la quota programmata di vendite annuali: questo fermacarte è uno dei vari esempi di oggetti promozionali che venivano loro regalati da IBM. Gli stabilimenti di Poughkeepsie, cittadina situata nella media Valle dell'Hudson, vennero avviati nel 1941 quando l'IBM era fornitrice dell'Esercito degli Stati Uniti e, tramite una sua diretta controllata (la Munitions Manufacturing Co.) fabbricava munizioni e cannoni contraerei. Terminata la Seconda Guerra Mondiale la Munitions Manufacturing venne assorbita dalla controllante e la fabbrica di Poughkeepsie divenne l'impianto "numero 4" dell'IBM, nel quale si producevano soprattutto macchine per scrivere. Nel 1962 l'IBM acquistò terreni agricoli nella zona di East Fishkill e vi realizzò un importante impianto per la produzione e l'assemblaggio di componenti microelettronici. Durante gli anni della guerra nelle due fabbriche di Poughkeepsie e di Ulster erano impiegati circa 31.000 dipendenti (vedi). In alto a destra si vede un modulo SLT del tipo di quelli impiegati nel System/360 racchiuso in plexiglass assieme ad alcuni transistor. Questo oggetto promozionale esiste in diverse forme e dimensioni (vedi ad esempio qui). In basso al centro c'è una spilla contenente un chip di DRAM da 16 Mbit fabbricato negli stabilimenti IBM di Bromont (Québec, Canada). In basso a destra un adesivo contenente un chip DRAM da 1 Mbit, prodotto probabilmente negli impianti di Essonnes (Francia). I chip DRAM da 1 Mbit vennero introdotti dall'IBM nel 1984 ed erano fabbricati con tecnologia SAMOS (Silicon and Aluminium MOS). IBM fu la prima a produrre in grandi quantità e ad utilizzare su scala industriale chip di questa capacità; di lì a poco periodo altri fabbricanti annunciarono la disponibilità di RAM dinamiche con caratteristiche simili (NEC, Fujitsu, Toshiba, Hitachi, Mitsubishi). I chip IBM da 1 Mbit vennero impiegati nel System/36, nel System/38, nei calcolatori 43xx, nel mainframe 3090 e nel Disk Cache Controller 3880.

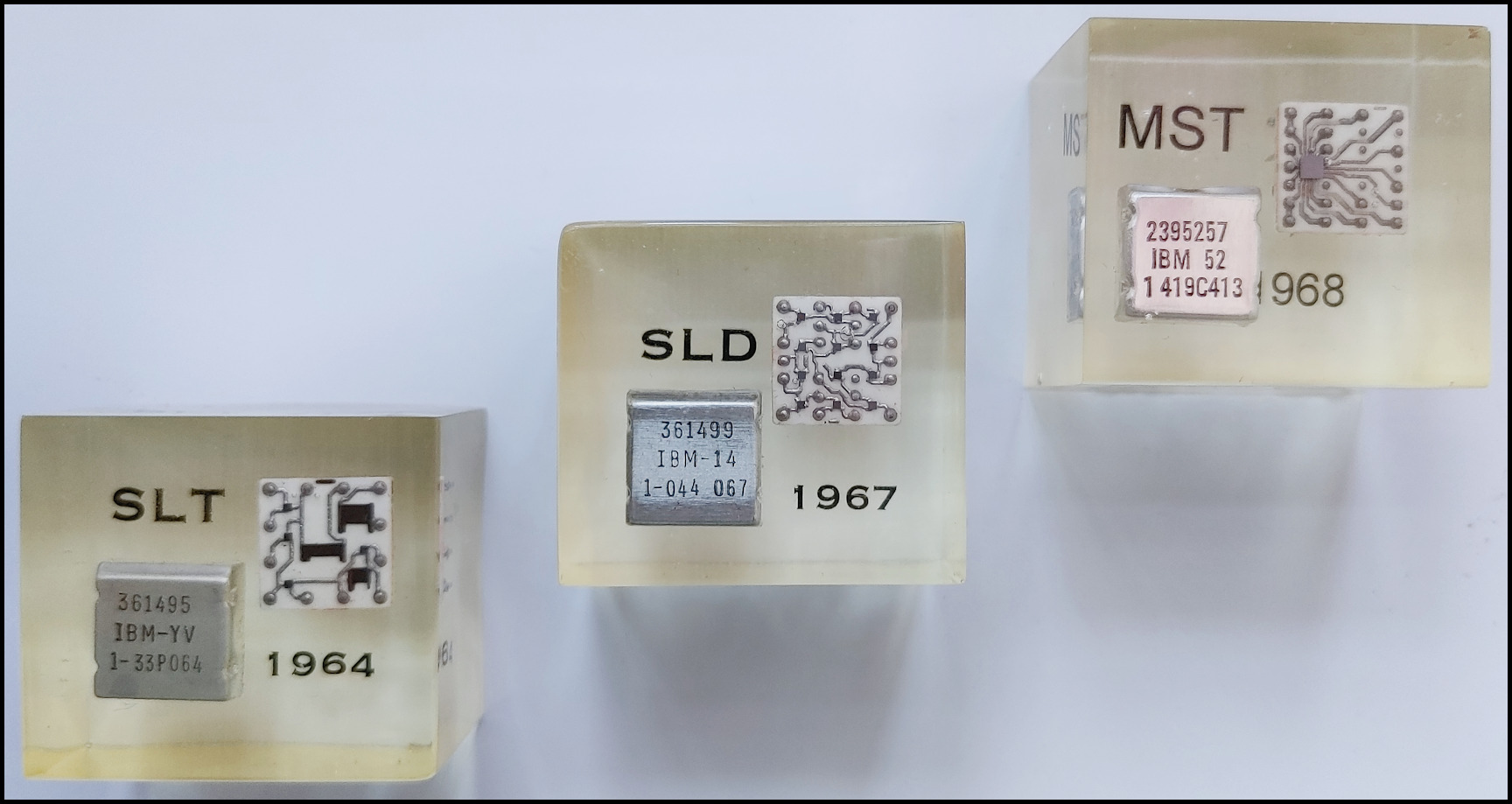

L'evoluzione della tecnologia IBM in 3 piccoli cubi fermacarte in plexiglass, contenenti (da sinistra a destra) un modulo SLT - Solid Logic Technology, introdotta nel 1964 con il System/360, al centro un modulo Solid Logic Dense (SLD) a 12 transistor e a destra un modulo MST - Monolythic System Technology, introdotta con il System/370 e basata su veri e propri circuiti integrati (tanto SLT quanto SLD erano invece tecniche a circuito ibrido). Il vantaggio in termini di densità circuitale conseguito dai moduli SLD rispetto agli SLT, di cui sono l'evoluzione diretta, è dovuto alla diversa organizzazione dei moduli, che raccolgono tutti i transistor ed i diodi su un lato riservando l'altro ai componenti passivi, perlopiù resistori.

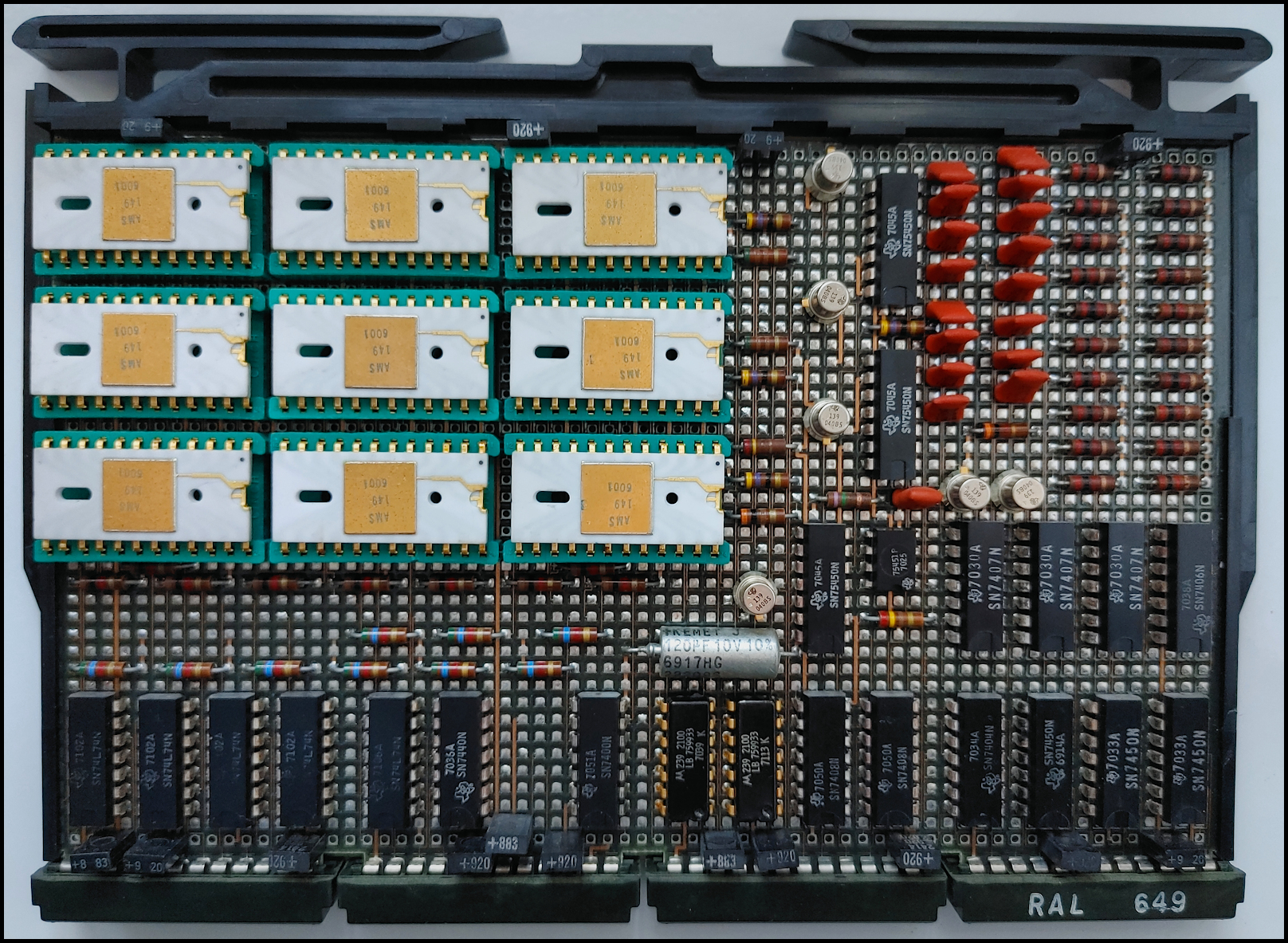

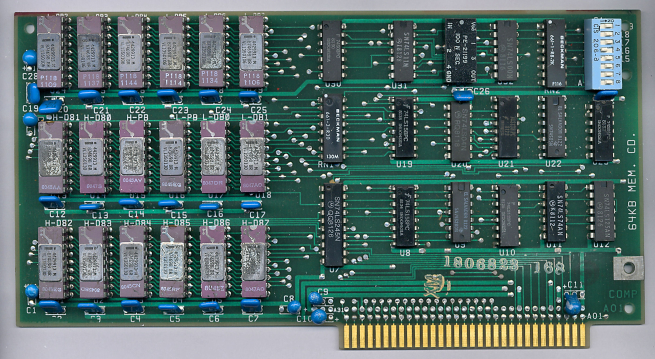

Scheda IBM "VTL" (Vendor Transistor Logic = integrati TTL di terze parti) con memorie RAM AMS 6001 da 1.024 bit (1 kbit), 1971, per un totale di 1 kbyte. Questa insolita scheda -è l'unica VTL che conosco con memorie AMS 6001- è probabilmente un prototipo, in quanto mancante del FRU. Non è noto da quale macchina provenga. L'AMS 6001 si presentava come concorrente a più basso costo della Intel 1103. Il vantaggio in termini di prezzo le derivava dal processo produttivo, P-MOS, mentre la controparte Intel utilizzava la tecnologia Silicon-gate. Anche il consumo, sia operativo che in standby, risultava inferiore a quello della 1103. La AMS 6001, introdotta all'inizio del 1970, è stata tra le prime DRAM commerciali da 1 kbit, e secondo alcuni la prima, essendo la Intel 1103 entrata in produzione a metà 1970 benché progettata ancora nel '69.

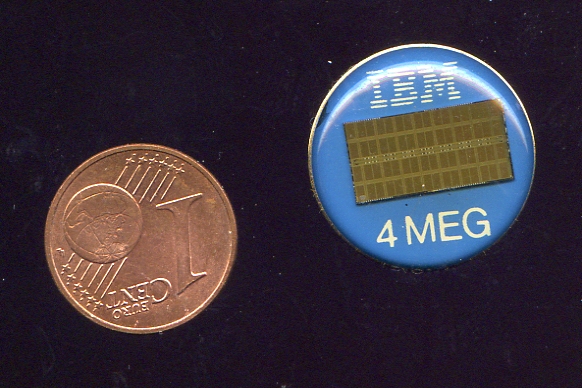

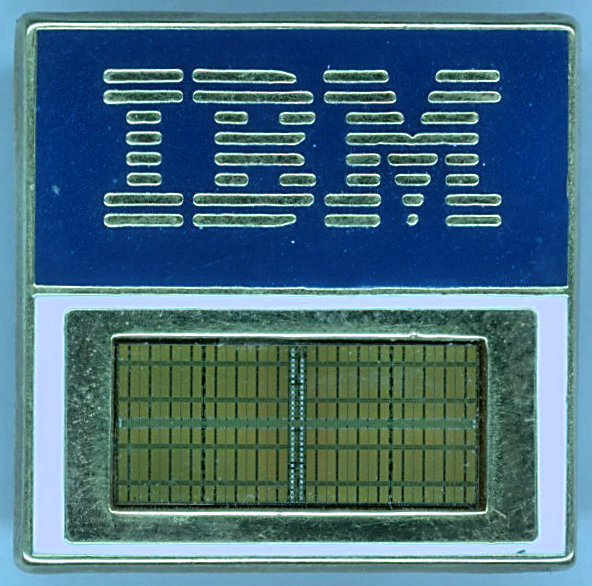

17.6.2015 - Adesivo IBM contenente un chip DRAM da 4 Mbit (circa 1991). Questo tipo di chip è stato impiegato, ad esempio, nelle SIMM da 8 MB utilizzate nei PS/2 modello 90 e 95. IBM è stata tra i primi produttori a rendere commercialmente disponibili DRAM CMOS di tale capacità. In questa pagina è visibile un chip simile benché catalogato come memoria da 1 Mbit.

Spilletta con chip DRAM da 16 Mbit (circa 1994).

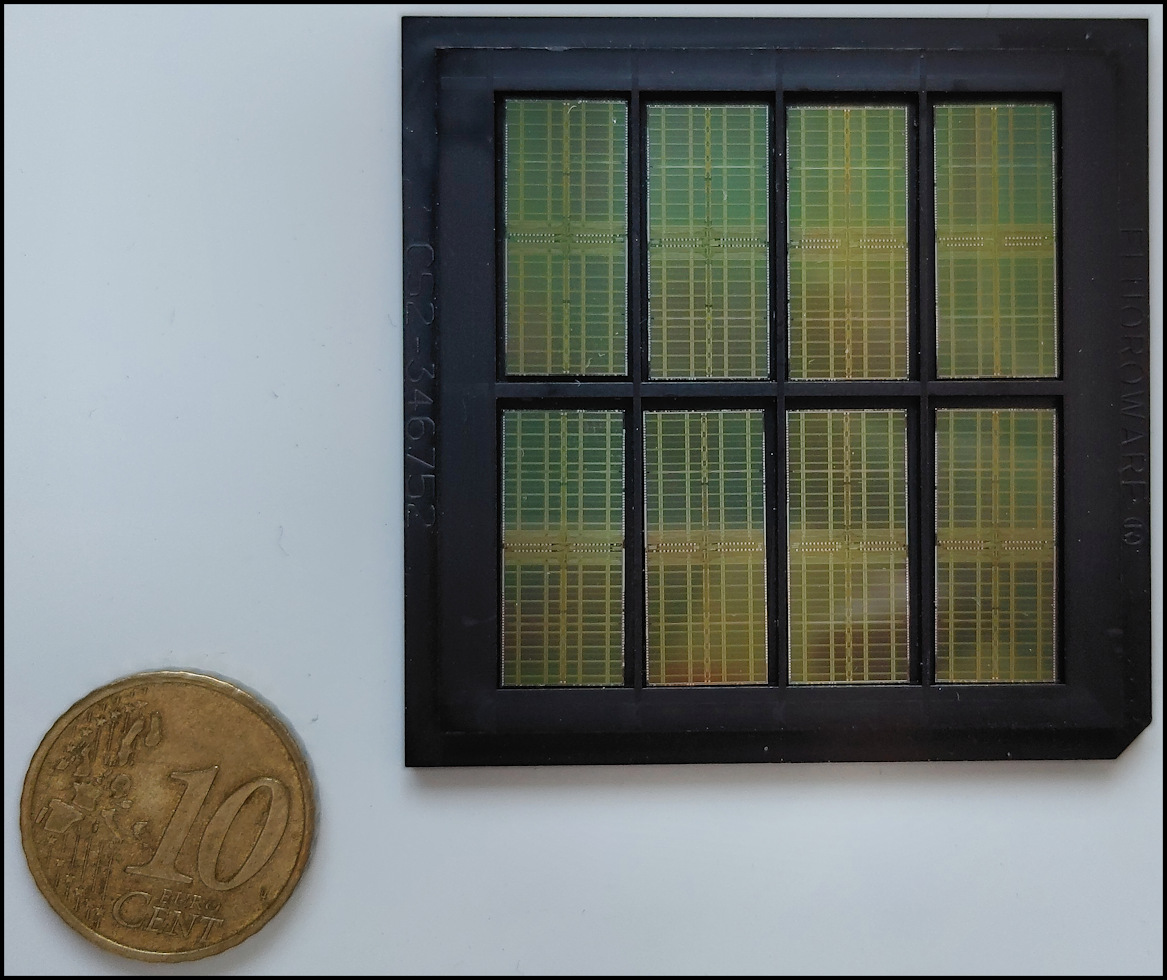

Engineering sample di DRAM IBM da 16 Mbit simili a quella dell'immagine precedente.

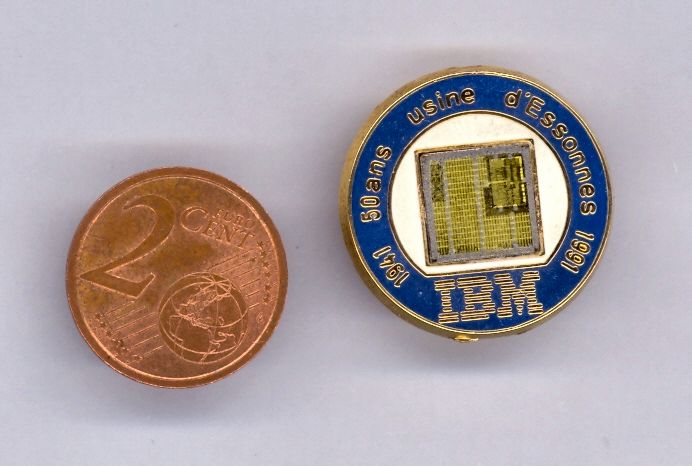

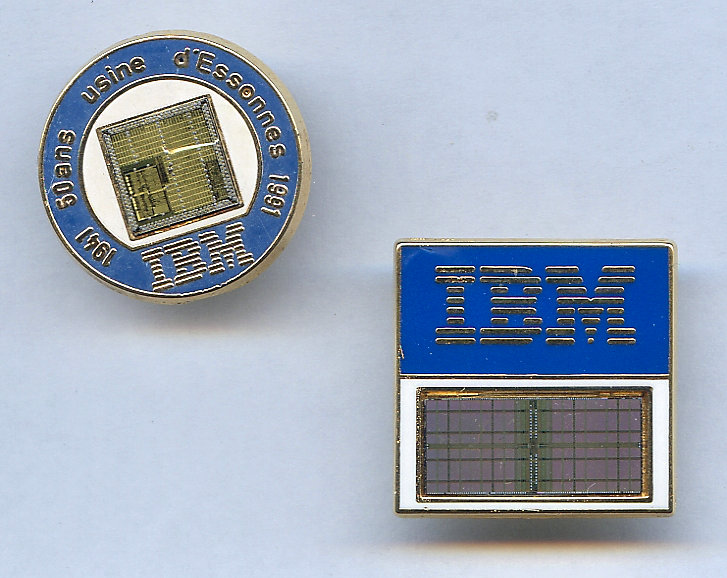

Spilletta commemorativa del cinquantesimo anniversario di fondazione degli stabilimenti IBM di Essonnes in Francia (1991).

Altro esempio di spilletta commemorativa per i 50 anni di attività dello stabilimento IBM di Essonness (Francia) e spilla con memoria DRAM da 8 Mbit (1992).

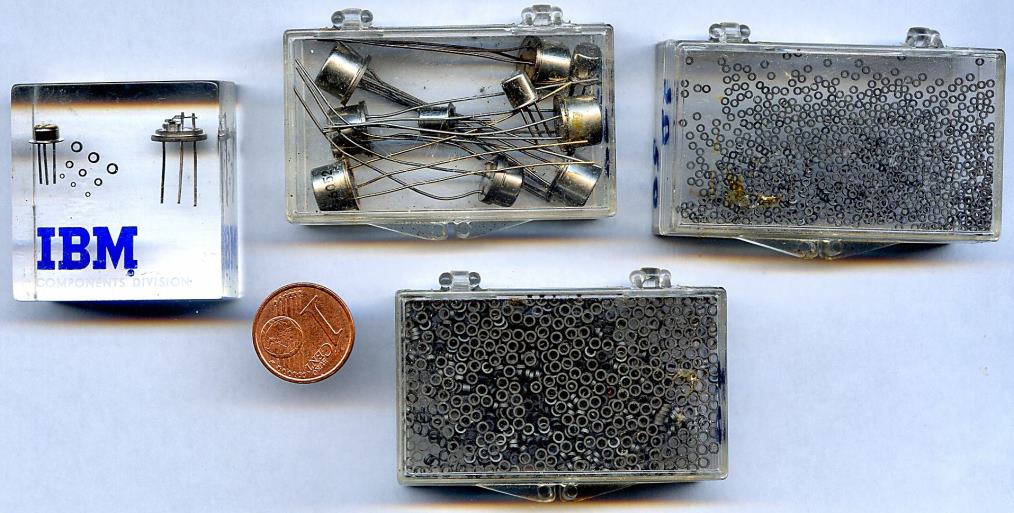

Vari materiali IBM utilizzati durante un servizio del fotografo Cornell Capa (fratello di Robert Capa) sull'attività di ricerca del Thomas J. Watson Research Center (vedi sotto). A sinistra un fermacarte promozionale contenente 2 transistor al Silicio utilizzati nei moduli SMS e nuclei magnetici di tre differenti misure; al centro, alcuni transistor datati 1963/1964 presumibilmente impiegati in moduli SMS ed SLT. A destra infine due scatolette con nuclei magnetici.

Entrambi provenienti da un centro di ricerca IBM, probabilmente il T. J. Watson visto che appartengono al medesimo lotto di materiali dal quale provengono gli oggetti visibili nelle immagini sopra e sotto, un piccolo wafer di transistor al Silicio con sulla scatola i dati relativi ai parametri dell'impiantazione ionica e, a destra, una maschera utilizzata nella fabbricazione di transistor (sulla scatola è riportata la dicitura "SS circuit chips" che fa pensare a qualcosa connesso alla produzione dei circuiti SLT, che negli anni Sessanta erano appunto denominati da IBM "circuiti logici a stato solido" sebbene non si tratti di integrati monolitici).

Questi interessanti oggetti provengono dal medesimo lotto al quale appartengono quelli raffigurati nell'immagine precedente e nella successiva. Si tratta in particolare di materiali appartenuti al Thomas J. Watson Research Center dell'IBM, risalenti alla metà degli anni Sessanta (circa 1967/8). A destra si vede una memoria sperimentale a film sottile (thin film) da 64 bit assieme alla scatola nella quale era stata messa a disposizione del fotografo (Cornell Capa). A sinistra in basso un altro esempio di circuito sperimentale (non identificato), forse un cryotron thin-film (vedi sotto). In alto a sinistra, una memoria thin film magnetica dalla capacità di 2.304 bit. Le dimensioni di quest'ultima sono di circa 56x56 millimetri. La scansione non riesce a rendere correttamente l'aspetto superficiale che è molto meno scuro di quanto sembri qui. Dalle ricerche che ho svolto dovrebbe trattarsi di una memoria RAM sperimentale prodotta dai laboratori IBM di Zurigo. La capacità totale dovrebbe essere stata di 18.432 bit suddivisi in 8 "placchette" metalliche massicce come questa, che pesa circa 130 grammi. Una memoria del tutto identica è raffigurata nel volume III.1 dell'opera di G. Mannino-Patanè, La Tecnica Elettronica e le sue applicazioni, Hoepli 1967, da cui ho tratto queste informazioni. Non mi è stato possibile reperire ulteriori dettagli al riguardo. Le memorie thin film sono state introdotte nel mondo dei calcolatori elettronici nel 1962 (Univac 1107). L'IBM le ha impiegate nel 1968 nel modello di punta della gamma System/360 (360/95). Sono state poi rapidamente accantonate a seguito dei progressi raggiunti dalla tecnica delle memorie a circuito integrato. Altri esempi di memorie thin film sono visibili in questa pagina ed in questa pagina del sito.

Aggiornamento Giugno 2016: l'oggetto in alto a destra potrebbe -il condizionale è obbligatorio!- essere un prototipo sperimentale di memoria criogenica a film sottile. Non ho trovato in Rete alcuna immagine di componenti simili; in quegli anni (questi oggetti risalgono al 1963/inizio 1964) la IBM stava in effetti svolgendo un'intensa attività di ricerca sull'impiego della superconduttività nei calcolatori elettronici.

YES! IT'S A CRYOTRON!

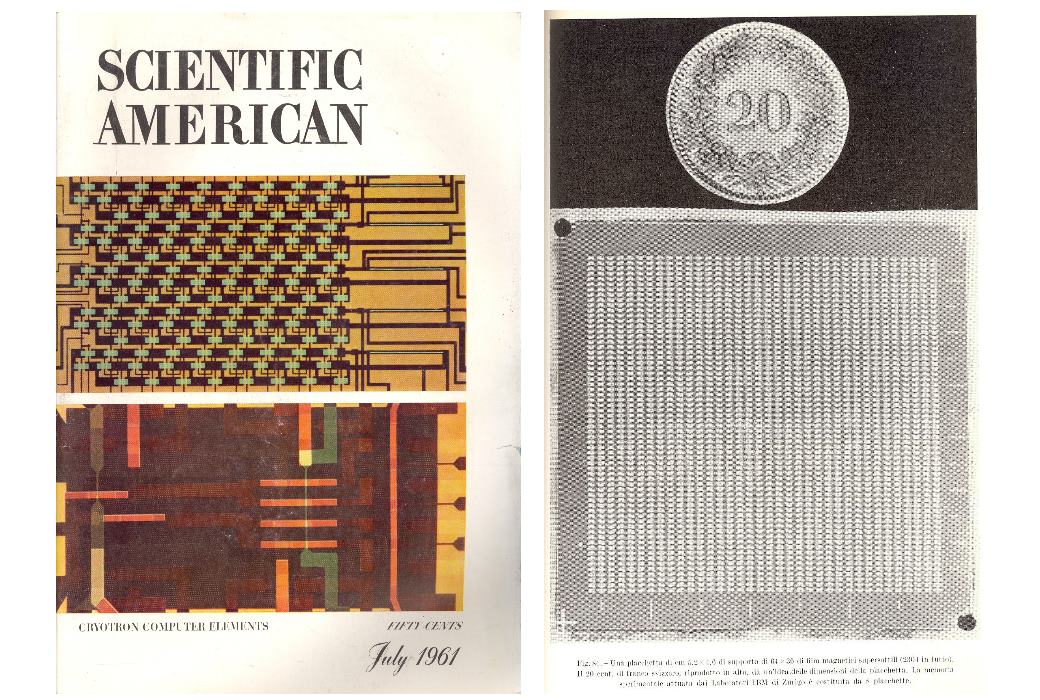

A sinistra: sulla copertina del numero di Luglio 1961 della rivista Scientific American (in Italia pubblicata dal 1968 e chiamata "Le Scienze"), due cryotron a film sottile su substrato di vetro, tra cui uno con funzioni di registro/memoria. Il cryotron in basso è davvero molto simile all'oggetto visibile in basso a sinistra nella foto precedente, anche se in quest'ultima la scansione non riesce a rendere i colori dovuti alla diffrazione della luce sulla sottile pellicola di materiale superconduttore depositata tramite evaporazione sotto vuoto. Ritengo quindi che quello in mio possesso sia effettivamente un cryotron thin film risalente all'inizio degli anni Sessanta. L'articolo di Scientific American in cui se ne parla (Superconducting Computers) è stato scritto da W. R. Ittner e C. J. Kraus, all'epoca ricercatori nei laboratori IBM. In particolare il cryotron visibile qui dovrebbe essere un flip-flop con tempo di commutazione di 0,3 microsecondi. Ricordo che il cryotron è un tipo di interruttore elettronico che sfrutta, per ottenere elevate velocità di commutazione, le proprietà dei materiali superconduttori. Venne ideato nel 1953 da Dudley Buck del MIT che lo brevettò nel 1955. I primi cryotron a film sottile (o "planari") vennero realizzati nel 1957 da John Bremer della General Electric. Tali dispositivi possono essere annoverati tra i primissimi circuiti integrati, per quanto non basati sui comuni semiconduttori. Tra la fine degli anni Cinquanta e l'inizio degli anni Sessanta vennero dimostrate svariate applicazioni dei cryotron nel campo dei calcolatori elettronici, ma essi non trovarono mai nessuna applicazione commerciale, rimanendo allo stadio di prototipi di laboratorio. Il nome "cryotron" deriva dal fatto che i materiali impiegati per realizzarlo operano a temperature criogeniche, ovvero al di sotto dei -200 °C. Non ho notizia di altri cryotron posseduti da collezionisti Italiani o europei: se ne avete uno, scrivetemi. A destra c'è invece la scansione di una pagina del libro Tecnica Elettronica e sue applicazioni di G. M. Patanè (Hoepli 1966, vol. 3 tomo I) in cui è raffigurata una memoria sperimentale IBM a film magnetico sottile identica a quella visibile nella foto soprastante. L'autore informa che tale memoria è stata sviluppata nel 1963/4 dai laboratori IBM di Zurigo e contiene una matrice di 64 x 36 film sottili di dimensioni 0,35 x 0,6 millimetri con spessore di circa 0,05 millesimi di millimetro, ognuno dei quali corrisponde a 1 bit di informazione. La "placchetta" sulla quale sono deposti i film sottili forma, assieme ad altre 7, un'unità di memoria magnetica dalla capacità di 18.432 bit. Il tempo di lettura è di 60 nanosecondi.

Cryotrons are very rare nowadays because they are essentially prototypal (experimental) devices never put into mass production. The total number of cryotrons fabricated over the years is unknown. If You have a cryotron like this (or a different one, or any other kind of experimental computer devices) in Your collection, please contact me!

Definizione di "cryotron": http://www.sapere.it/enciclopedia/cryotron.html.

Vedi: https://spectrum.ieee.org/tech-history/heroic-failures/dudley-bucks-forgotten-cryotron-computer; https://www.technologyreview.com/s/601543/the-tiny-switch-that-almost-made-it-big/.

Articolo di Dudley Buck (The Cryotron): https://dome.mit.edu/bitstream/handle/1721.3/40618/MC665_r15_M-3843.pdf?sequence=1.

Articolo di Bremer sul cryotron planare a film incrociati: https://www.computer.org/csdl/proceedings/afips/1959/5055/00/50550255.pdf.

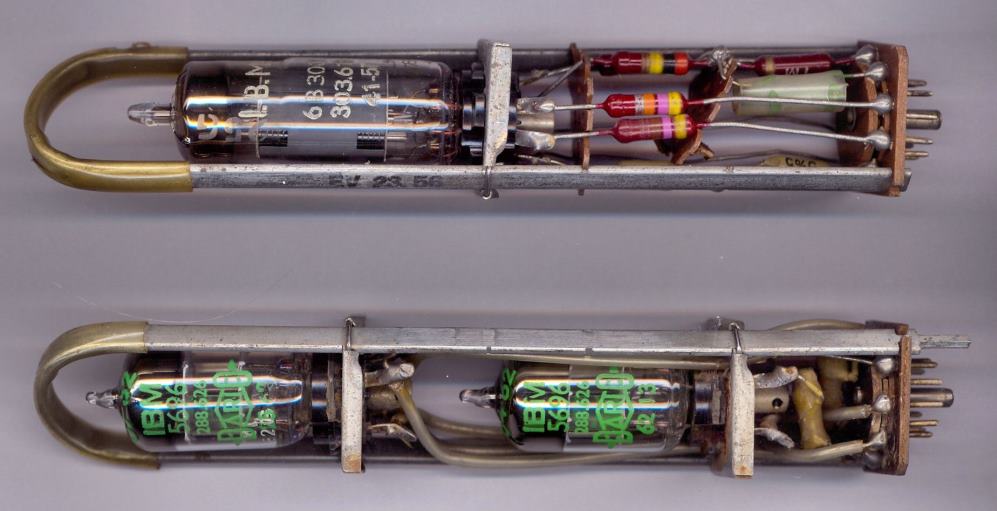

Coppia di moduli a tubi elettronici IBM, colloquialmente denominati "fingers". L'esemplare in alto è di tipo PS-20 ed aveva la funzione di amplificatore (buffer) di segnali logici. Era probabilmente installato in un IBM 604. Presenta un particolare "reworking" non completamente visibile nell'immagine: uno dei resistori nella parte destra è stato sostituito ed è stata rifatta la saldatura, ma in questo modo non è stato più possibile mantenere l'allineamento della piastra separatrice in bakelite. Il modulo sembra essere del 1956, la valvola è invece del 1963. L'esemplare in basso è di tipo DS-501 del 1958 (forse DD-501, la stampigliatura è in parte abrasa), proveniente da un IBM 650: si tratta di un elemento di commutazione logica e contiene due thyratron/tetrodi a gas Xenon IBM/Dario 5696 fabbricati nel 1962. Il tubo 5696 in virtù dell'elevata velocità di commutazione era utilizzato in molte macchine IBM di prima generazione. E' stato introdotto da RCA all'inizio degli anni Cinquanta.

Caratteristiche del tubo RCA 5696: https://frank.pocnet.net/sheets/079/5/5696.pdf

Vedi: http://www.decadecounter.com/vta/articleview.php?item=293 (modulo costruttivamente simile al DS-501)

Anche: http://ed-thelen.org/comp-hist/IBM-604.html; http://www.nzeldes.com/HOC/PluggableUnits.htm; http://www-03.ibm.com/ibm/history/ibm100/us/en/icons/ibm603/breakthroughs/.

Vedi: https://pdfs.semanticscholar.org/58e7/9f00e2e012ac64de130982fc3b991284a50a.pdf (The Architecture of IBM's Early Computers).

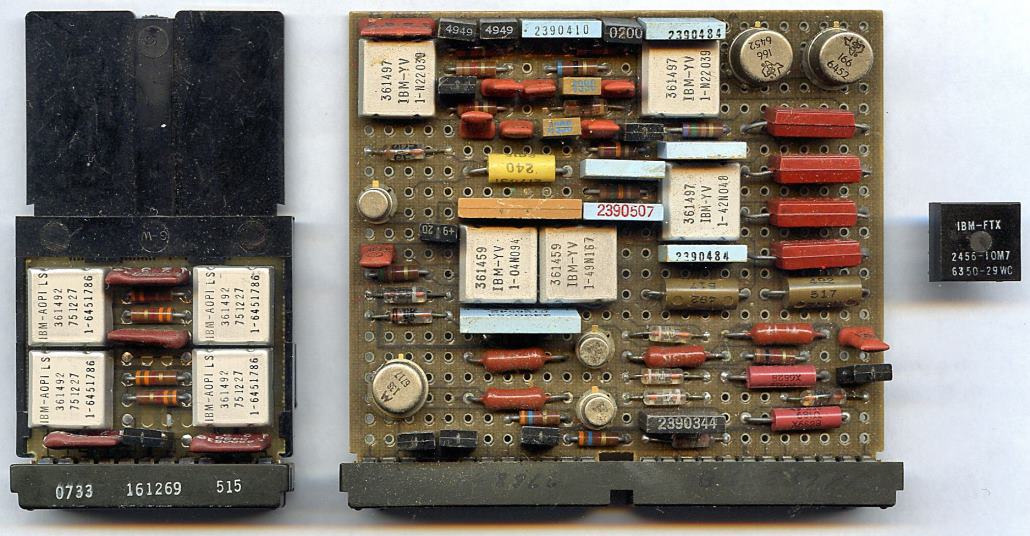

19.12.2016 - Due moduli IBM SLT (Solid Logic Technology) databili tra l'inizio del 1965 ed il 1967 (montano componenti con codici di data compresi tra il 1964 ed il 1967), più un circuito ibrido IBM SLT sperimentale in package plastico di datazione incerta. Questi moduli SLT sono i più vecchi che abbia incontrato e provengono, come il circuito a destra, da un lotto di materiali IBM del Thomas J. Watson Research Center che furono utilizzati alla fine degli anni Sessanta, probabilmente nel 1969, per un servizio fotografico sull'attività di ricerca dell'IBM svolto da Cornell Capa, fratello del famoso Robert Capa. La tecnologia SLT venne ufficialmente introdotta da IBM nel 1964 con i calcolatori della famiglia System/360 (vedi: https://en.wikipedia.org/wiki/IBM_Solid_Logic_Technology).

Vedi: http://poincare.matf.bg.ac.rs/~zstanic/uor/Slajdovi/S360.pdf (The 360 Revolution).

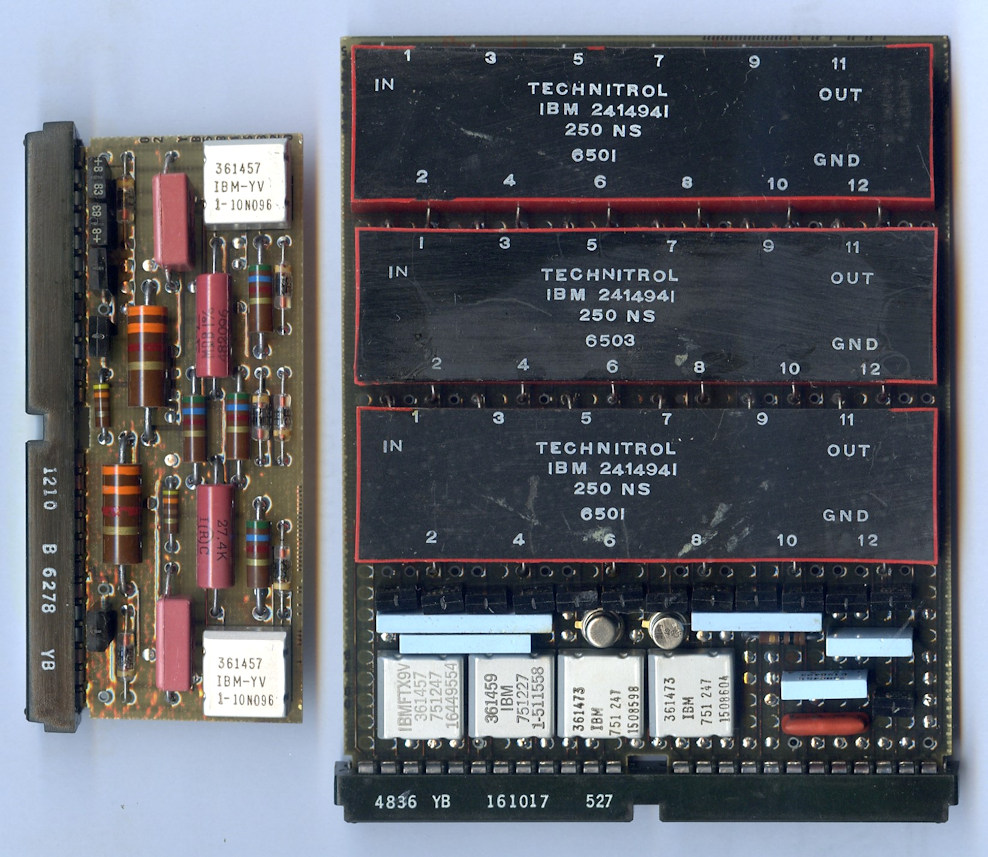

Moduli IBM SLT del 1965, di cui quello a destra contiene 3 linee di ritardo Technitrol da 250 ns.

Piccolo fermacarte in plexiglass dedicato all'inaugurazione della fabbrica IBM di Bromont (Québec, Canada) nel Giugno 1972. A destra il substrato ceramico di un modulo MST (Monolythic System Technology).

Portachiavi con modulo MST fabbricato nello stabilimento IBM di Essonnes in Francia (circa 1980).

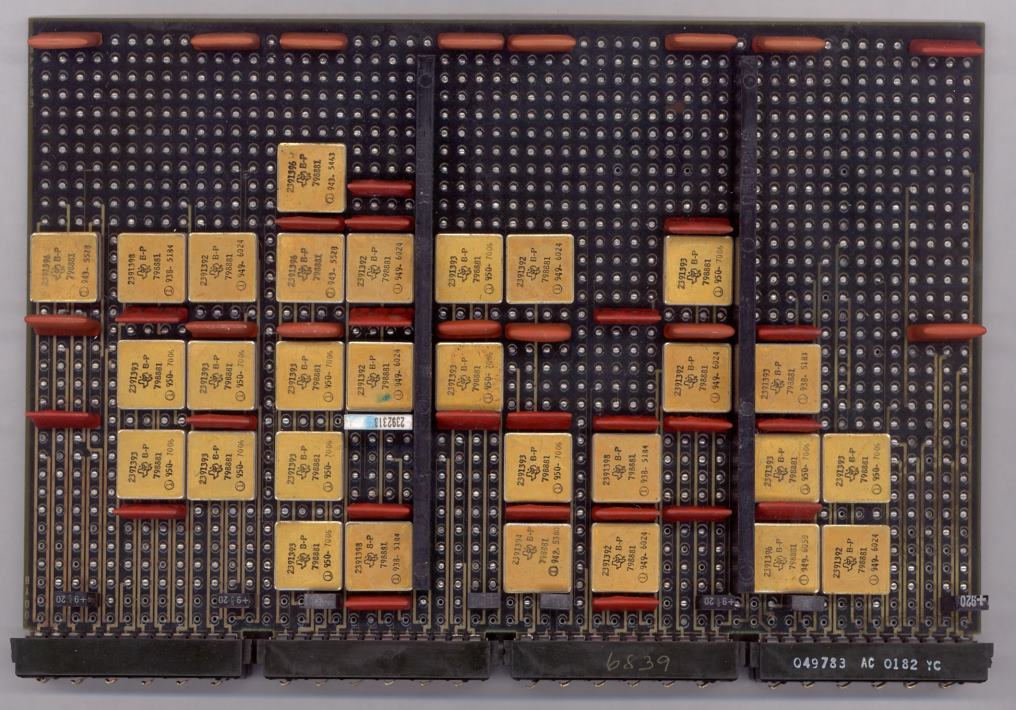

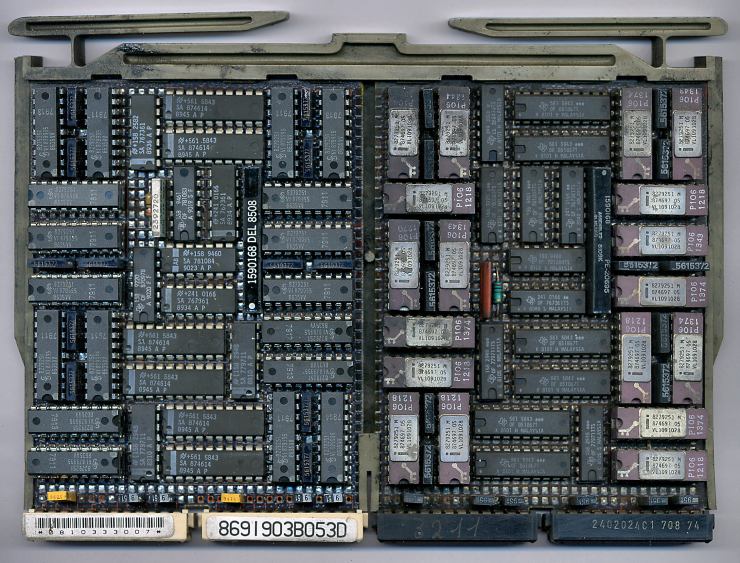

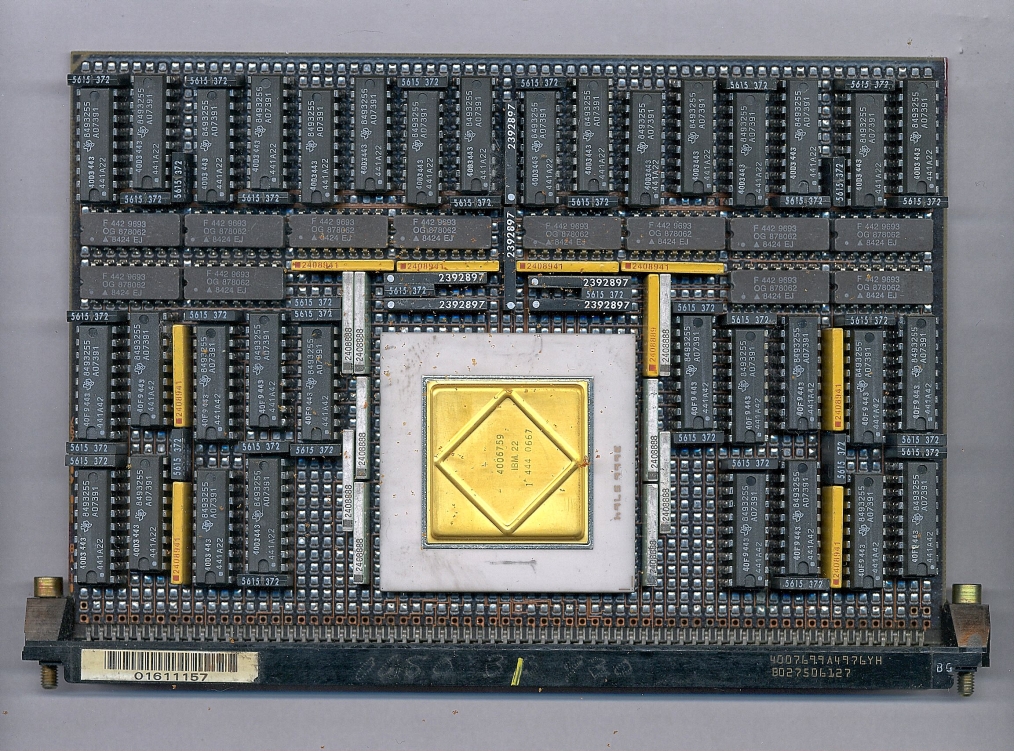

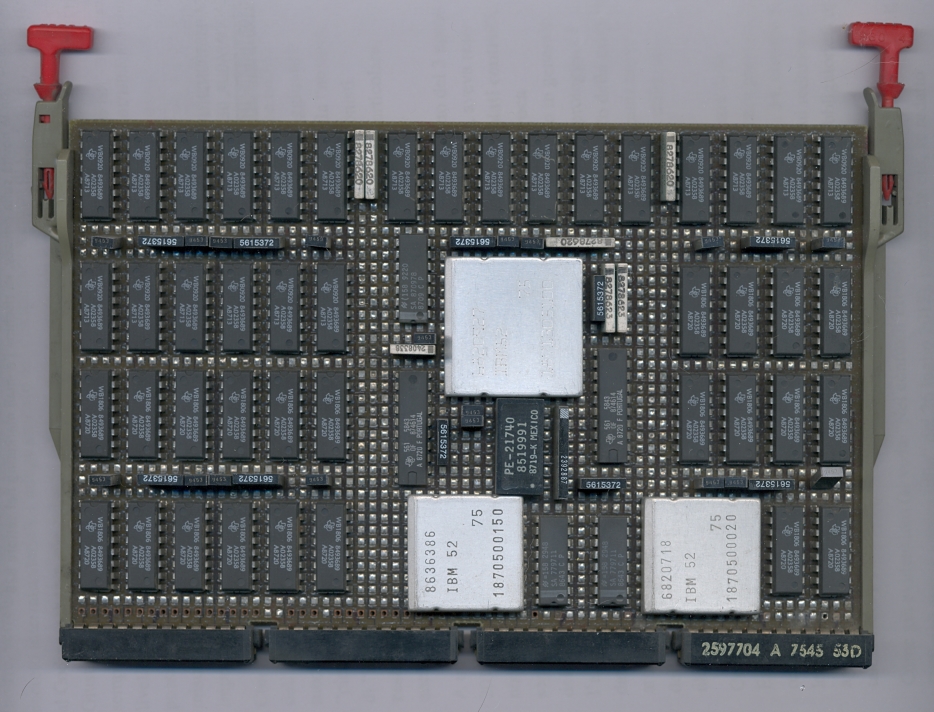

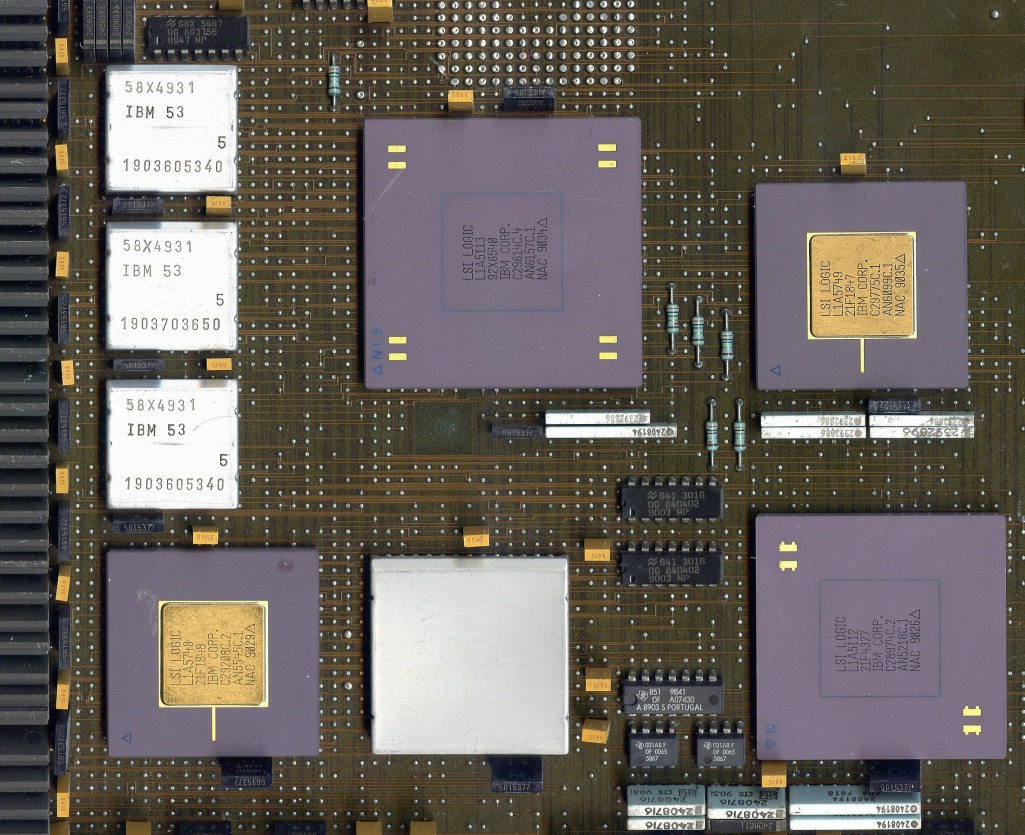

Scheda con integrati ECL Texas Instruments a bassa scala di integrazione (SSI) in package ceramico-metallico proveniente dalla CPU di un mainframe IBM System/360 modello 195 (1969/1970). Ciascun integrato contiene da 2 a 4 porte logiche elementari, in genere NAND a due ingressi. Il passo (spaziatura) dei piedini è compatibile con quello dei moduli IBM MST. Notare anche, in basso, la presenza di alcuni contatti di backplane aggiuntivi non presenti nelle "normali" schede con tecnologia SLT/MST. Un singolo circuito TI dello stesso tipo è visibile in questa pagina del Museo. Il modello 195 era la versione più potente della famiglia IBM 360. Fu prodotto in un ridotto numero di esemplari (circa 20), venduti per la maggior parte ad istituti di ricerca ed agenzie governative (ad es. la NASA). A differenza degli altri modelli meno potenti, faceva uso -nella CPU- di integrati monolitici ECL anziché di moduli logici ibridi (SLT). I tempi di commutazione delle porte logiche ECL del 360/195 erano di circa 3 nanosecondi, dunque molto più brevi rispetto a quelli degli altri membri della serie 360. L'IBM 360/195 venne annunciato nell'estate del 1969 e commercializzato a partire dal 1971 fino al 1977. All'epoca era la più potente macchina IBM e poteva competere con i più veloci supercomputer del mondo, ad esempio il CDC 7600, così come il suo predecessore 360/91 era stato la "risposta" IBM all'avvento del CDC 6600.

In questa pagina sono visibili alcune schede provenienti da un IBM 360/195: http://www.chilton-computing.org.uk/ca/technology/s360_195/p002.htm.

Caratteristiche del 360/195: http://www.bitsavers.org/pdf/ibm/360/funcChar/GA22-6943-1_360-195_funcChar_Aug70.pdf.

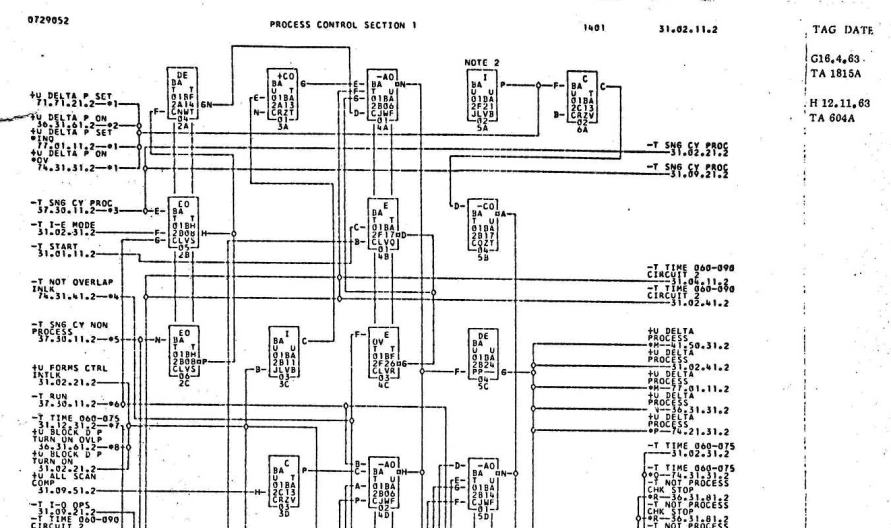

1.10.2014 - Microfiche IBM (Aprile 1971) con la descrizione di schemi logici generati automaticamente (ALD: Automated Logic Diagrams) applicati a circuiti SLT, SLD (Solid Logic Dense), ASLT (Advanced SLT) e MST (Monolithic System Tecnnology, utilizzata a partire dal System/370), parte della serie Field Engineer Maintenance Library. La tecnologia SLD permetteva di aumentare la densità di integrazione montando su un lato del substrato ceramico i componenti attivi (transistor) e sull'altro quelli passivi (resistori). L'ASLT impiegava invece due substrati ceramici in uno stesso package. Il contenuto del è consultabile come documento PDF a questo indirizzo.

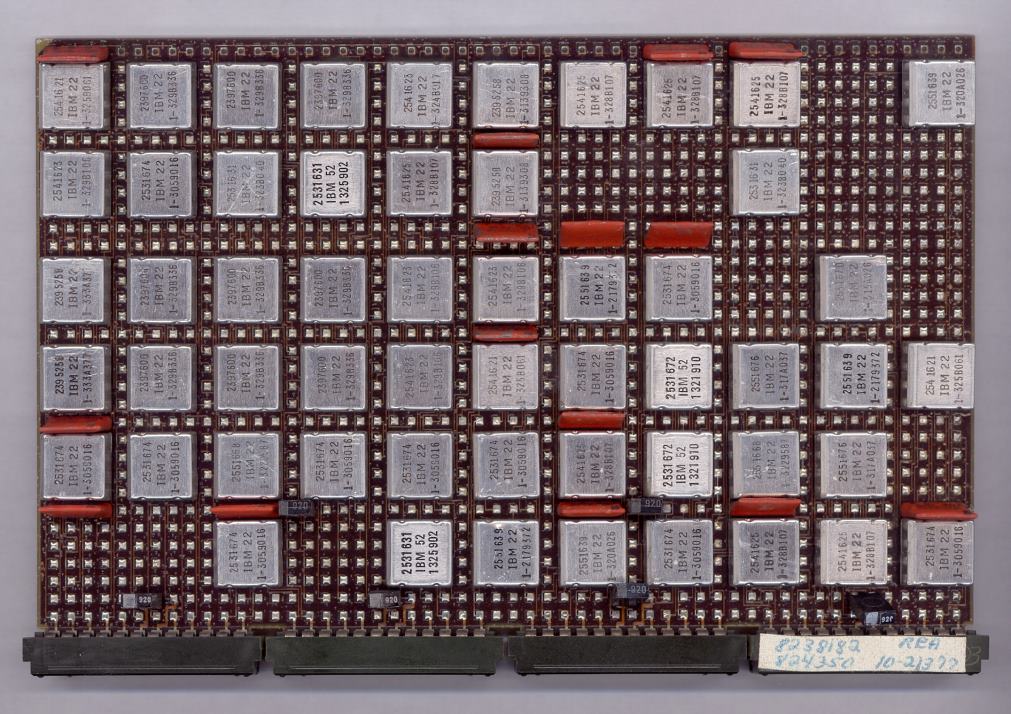

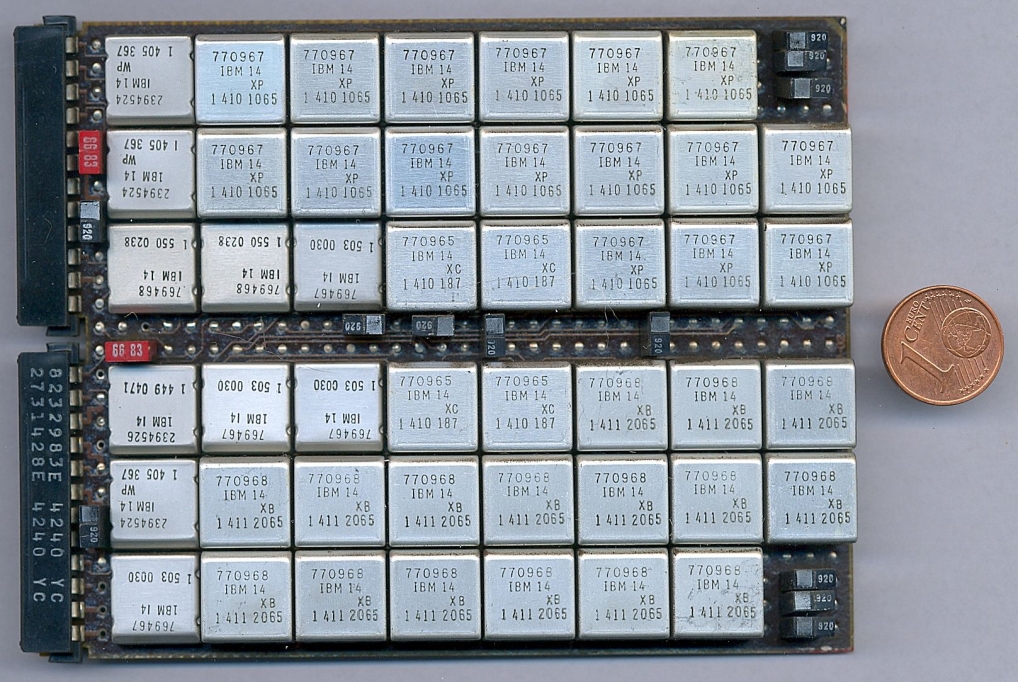

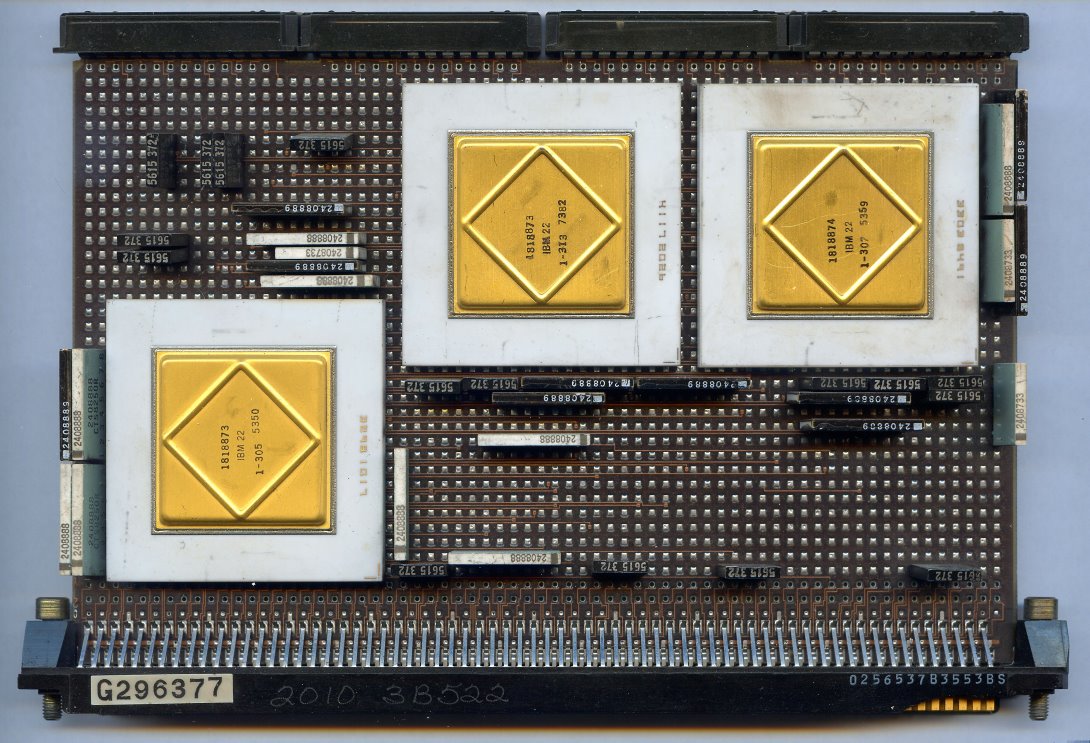

Modulo con 4 schede MST proveniente da un mainframe IBM System/370 modello 145.

Scheda SLT proveniente da un mainframe IBM System/370.

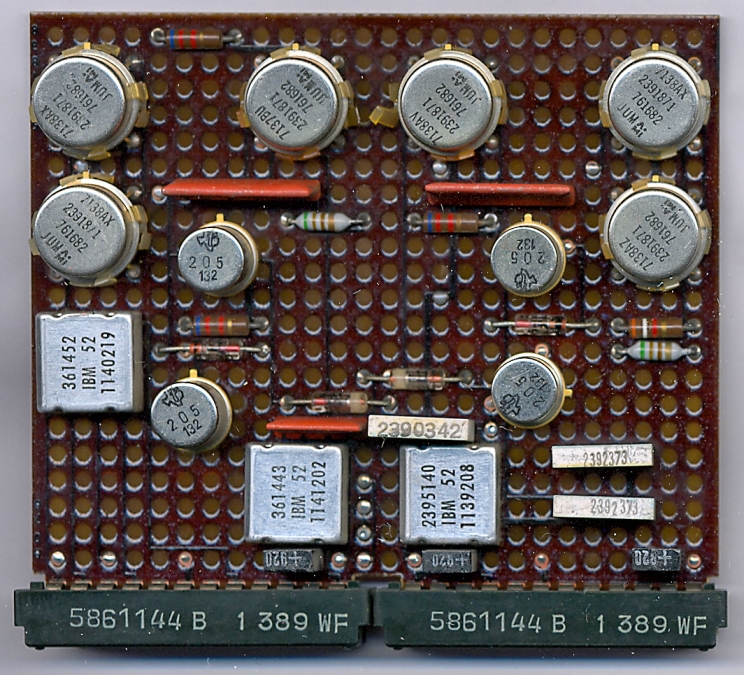

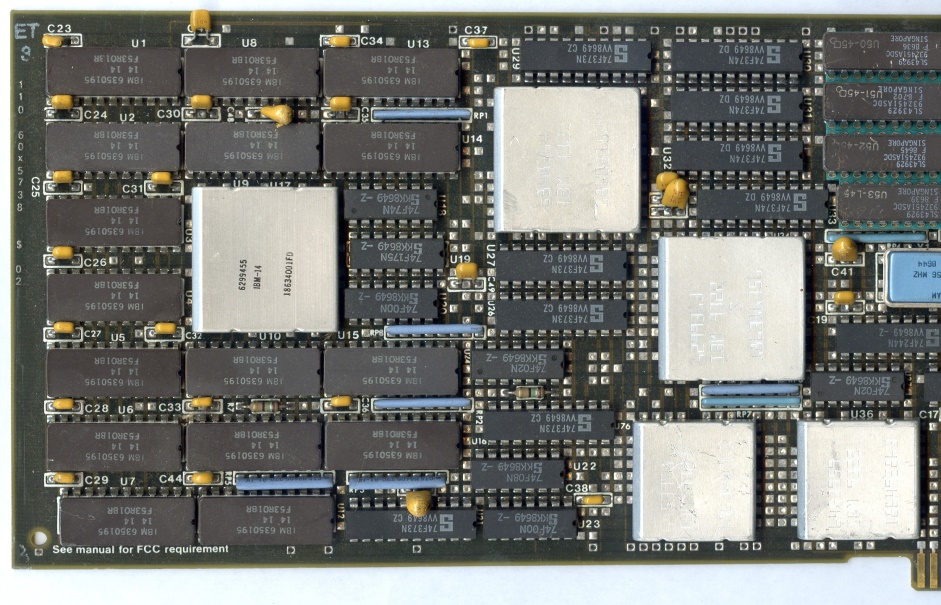

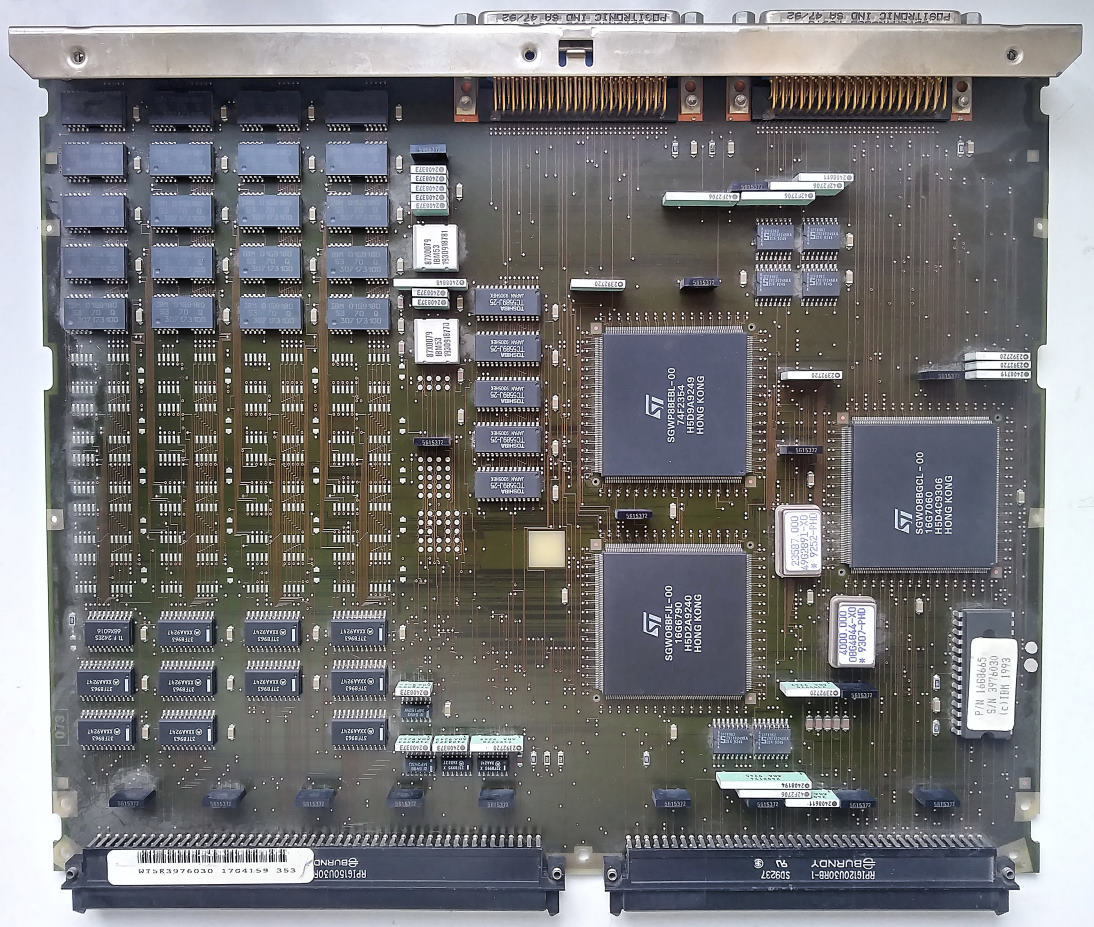

Elettronica di controllo di un'unità a disco IBM 3370, 1981, con moduli e backplane di tipo MST (Monolithic System Technology). Presentato nel 1979, l'IBM 3370 (denominato New File Project) è stato il primo hard disk commerciale di grandi dimensioni (14 pollici, in questo caso) con testine thin-film, una tecnologia sviluppata dalla stessa IBM alla fine degli anni Sessanta presso il T.J. Watson Research Center. La capacità del 3370 è di 541 MB per unità; il tempo d'accesso medio è pari a circa 20 ms, con una velocità media di trasferimento dei dati di circa 1,86 MB/s. I dischi 3370 erano in genere accoppiati ai mainframe 4331/4341 ed al System/38, che poteva controllarne direttamente (senza cioè l'ausilio di un controller esterno) fino a 4, per una capacità totale di circa 2,16 GB (vedi http://www-03.ibm.com/ibm/history/exhibits/storage/storage_3370b.html). Nella foto è visibile in basso a destra una tipica scheda MST in cui si mescolano componenti IBM e di altri produttori; ciò era reso possibile dall'adozione di un passo standard per la spaziatura dei punti di saldatura. Il dettaglio in alto a destra mostra l'interconnessione tra i moduli MST ed il backplane: come già nel caso della tecnologia SLT, il "maschio" è si trova sul backplane e la "femmina" sulla scheda, contrariamente a quanto accade di solito; il meccanismo di ritenzione e supporto dei moduli è in gran parte derivato dalle specifiche SLT introdotte con l'IBM System/360 nel 1964. La forma del backplane MST (vedi) è però diversa dall'SLT (vedi). Si noti, nel dettaglio in basso a sinistra, la particolare organizzazione del backplane, in cui si trovano sia interconnessioni su circuito stampato che altre di tipo "wire-wrapped", ottenute cioè con fili che collegano coppie di piedini. Nei dettagli si intravedono le lettere che distinguono i vari connettori di backplane. I moduli MST fanno uso di circuiti stampati multistrato, con livelli separati per l'alimentazione ed i segnali; il numero di livelli varia a seconda delle diverse successive revisioni di questa tecnologia particolarmente longeva (ancora in uso, soprattutto in alcune periferiche, attorno alla metà degli anni Novanta, più di vent'anni dopo la sua introduzione con il System/370). Come già ricordato altrove in questo sito, nella realizzazione dei circuiti MST IBM fece largo uso di schemi logici standardizzati e, a partire dalla metà degli anni Settanta, di gate array MSI/LSI prima bipolari e poi MOS. I circuiti logici MST sono caratterizzati da un minimo numero di resistenze e capacità integrate: la maggior parte di esse si trova infatti esternamente, sulla scheda (sono i piccoli componenti rettangolari neri e bianchi visibili nell'immagine sopra). Molte schede MST hanno connettori sia dal lato del backplane che da quello opposto, il che permette ulteriori connessioni grazie a particolari "ponti" realizzati con circuito stampato ad 1 o 2 livelli, incrementando così il numero di connessioni utili per unità di superficie.

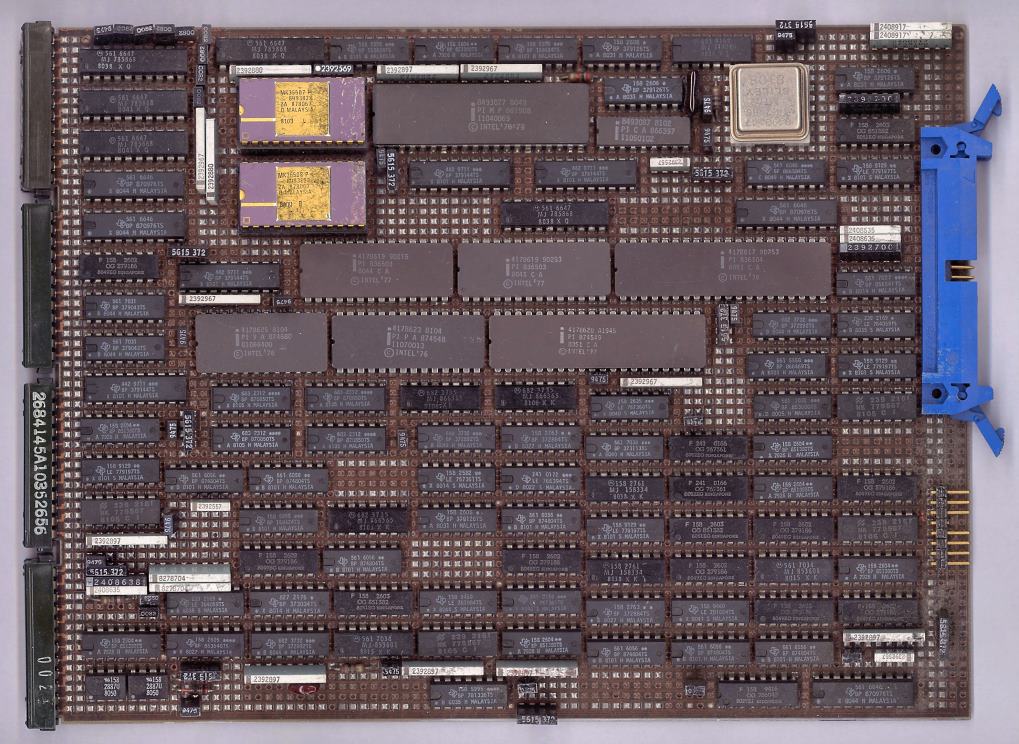

Da https://www.eevblog.com/forum/blog/eevblog-960-mystery-merry-mailbag-teardown/25/:

"[...] All the DIP chips will be IBM part numbered 74 or 74LS series 'Jelly Bean' chips. It was very rare to see a standard part numbered chip back in the day. Even the likes of 741 Op-Amps would be IBM part numbered. Engineers also had IBM part numbered Fluke multimeters, Tektronics scopes, Snap On tools etc etc. There was a very specialised inventory control system, that Don will remember, called CEPICOS (Customer Engineering Parts Inventory Control On-line System.) that managed stock of millions of parts for IBM locations worldwide. And as noted, all the grid holes in the boards are filled with solder. I imagine that the components were installed in the correct places and the board wave soldered, thus filling up all the unused holes. They would have had another machine to solder on the spring contacts for the end connectors. Having had to replace munted contacts manually, it is a pretty precise job and hard to do well by hand. I don't know of a chip list of IBM part numbers to standard chip numbers, but someone on the net should have one. BTW. At one point IBM was the largest manufacturer of silicon chips in the world. Move over Texas Instruments, but alas no longer. But as IBM used its own silicon and never sold it, it was never widely reported."

"It's likely the IBM chips you see in this would have been made in East Fishkill, NY, which handled the bipolar chips used by the IBM Server group, whereas Burlington handled CMOS chips, more commonly used in IBM's consumer and low-end products like the PC division, at least until the mid 90's when Fishkill eventually switched over to CMOS. Unfortunately I have no information on the PCB layout style, but my best guess is that it did enable very early design automation. IBM has an extremely proud EDA (Electronic Design Automation) heritage going well back before I joined (hey, when you have giant mainframes at your disposal to use, you might as well use them!) Well before commercial EDA tools were available, IBM had an in-house EDA group [...] that wrote their own schematic entry and synthesis systems, logic simulators, transistor-level simulators, test pattern generation tools, static timing analysis, chip place and route, you name it. And this was LONG before any of the 3rd party tool vendors existed. [...] at least prior to the late 80's, these all ran on mainframes accessible via terminals with very limited graphics capability. Everything was driven by esoteric text files with a zillion three letter acronyms in addition to ALD. This was all for chip design, but I suspect the board designers had similar technology. When you are limited to designing on a more or less text-based display using very primitive (by today's standards) layout and routing tools, it's no wonder you'd wind up with that grid-based board design technique. [...] one of the first truly graphical EDA environments (at least for chip design). It still ran on the mainframe and was originally written in Pascal, but it did use a 5080 graphics terminal. A few years later we ported it to the RS/6000 UNIX environment. This was a little after other EDA vendors were starting to have legitimate offerings on Sun, Apollo and HP machines, so we were somewhat behind the times, but most of the IBM design community was still running on mainframes. The IBM EDA group continues to this day and certainly has its niche areas of expertise. Cadence's Encounter Test tool is based on an IBM test tool and still has "hidden" IBM environment variables that are used for certain IBM proprietary uses (nothing outrageous, just turns on certain output formats used by custom IBM chip test equipment), and IBM's static timer is state of the art, albeit not really industry compatible (IBM's solution is the "Beta" to the industry's "VHS"). But once IBM sold its chip manufacturing business to GlobalFoundries in 2015, I wonder if the EDA group is sustainable."

"Regarding the routing, the right angles were fine. Make no mistake, IBM has well ahead of the pack with their PCB manufacturing technology. They had no issue with etching near the corners. Most raw cards were made near the corner of Braker Lane and Burnett Road in the Balconnes area of Austin Texas, which is now a park area (not residential) due to the toxic materials that have leached into the ground. [...] why 45 degree tracks are silly and that these days 90 degree tracks are fine. Sort of true. But I don't like them for the following reasons:

1. Sharp corners might invite arcing on higher voltage circuits or when an ESD spike hits.

2. They look crap. PCB layout should be impressive artwork. It looks like you've done a cheap job on a PCB. No science to it, just aesthetics. You won't get impress the chicks with 90 degree tracks. It looks like painting your fence in Mission Brown. Pride in PCB layout show the work of a craftsman rather than the average tradesman.

There is some argument about EMI. For differential high speed signals, I don't believe there is much difference between 2 x 45 degrees, or 1 x 90 degrees per track OVERALL; as long as the impedances are matched, the electrical lengths are the same etc. I don't like right angle buses in schematic layouts. This is for a practical reason. The right angle on a bus entry or buss bends for example, "points" to the direction of its connection at the other end. Right angles do not do this. Furthermore, a poorly printed schematic is easier to decipher with 45 degree connections rather than right angles. (I hate round dots for pin 1 marks too in PCBs. Triangles are a lot smarter, for practical reasons.) IBM's computer generated schematics were below par in my opinion - bloody hard to follow. They never used standard logic symbols for a start; just "logic blocks"."

"I don't know what IBM called the style of that grid arrangement but it was used in the majority of IBM equipment in the 70s and 80's. (Terminals, modems, mainframes, mid range systems, communication controllers, disk drives, tape drives, electronic typewriters, matrix and line printers. Pretty much everything.) It is multilayer, four layer at least, with plated through pads at 0.1" everywhere. I think that IBM must have had a process to make them that could easily have the traces added where needed. So you could place chips and passive components anywhere on the board and use all the other holes as vias. Most boards have spring contacts soldered along the edges and green plastic covers snapped over them. Some boards have these connectors on both ends of the board and once plugged into the main mother board, crossover connectors connected the rears of boards where necessary. The boards also typically had a plastic frame clipped around them that had guides and eject levers so engineers could easily insert and remove them from equipment. (Not so in space constrained test gear.) [...] Bypass capacitors, when used, where typically single caps (Not arrays). They where pretty much the same size as the resistor arrays but only 2 pins long. The big silver aluminium cans... We called these 'Duchess Modules' (Their code name. Everything in IBM had a code name.) They were always through hole [...] They came in different pin configurations depending on the number of wires that the chip needed. There were literally hundreds of different types. The IBM PS/2 (1987) even used them. The smaller cans had different configurations too. Sometimes they where as simple as just containing four transistors."

Stampa di parte di un ALD (Automated Logic Diagram, "Diagramma Logico Automatizzato") generato da un software IBM EDA (Electronic Design Automation) per la progettazione assistita da computer di circuiti logici. Riprodotto da: https://www.eevblog.com/forum/blog/eevblog-960-mystery-merry-mailbag-teardown/. Ulteriori informazioni si possono reperire qui: http://ibm-1401.info/ALDs-fromAustralia.html.

Scheda MST impiegata nella logica di controllo di un disk drive IBM 3370.

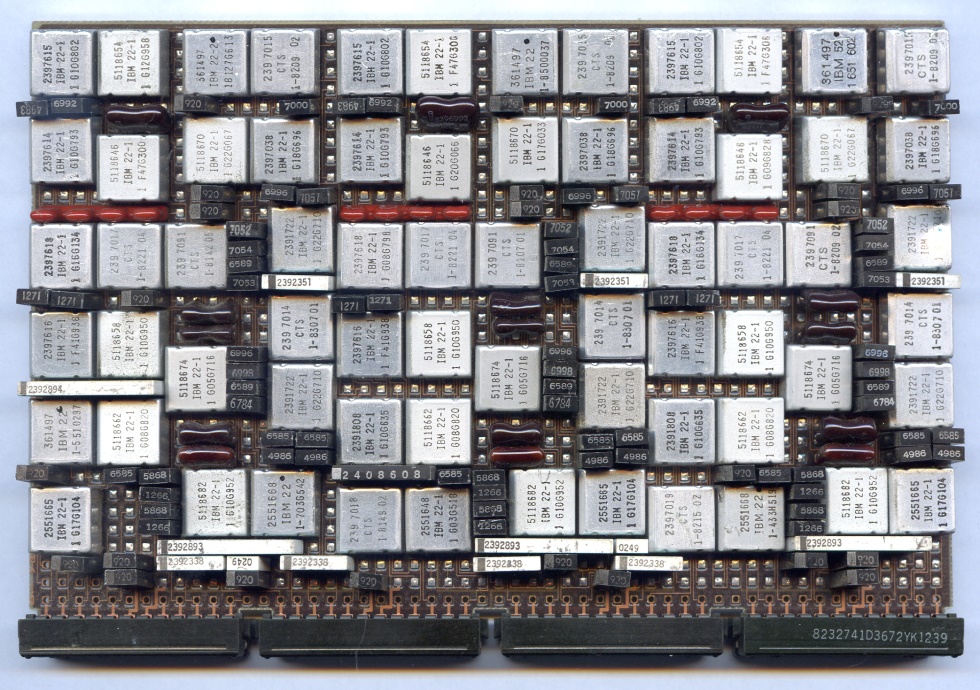

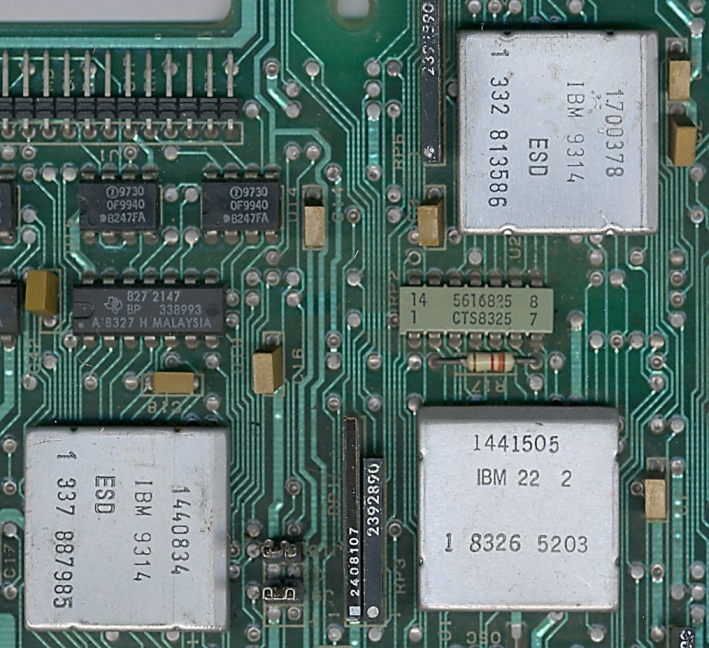

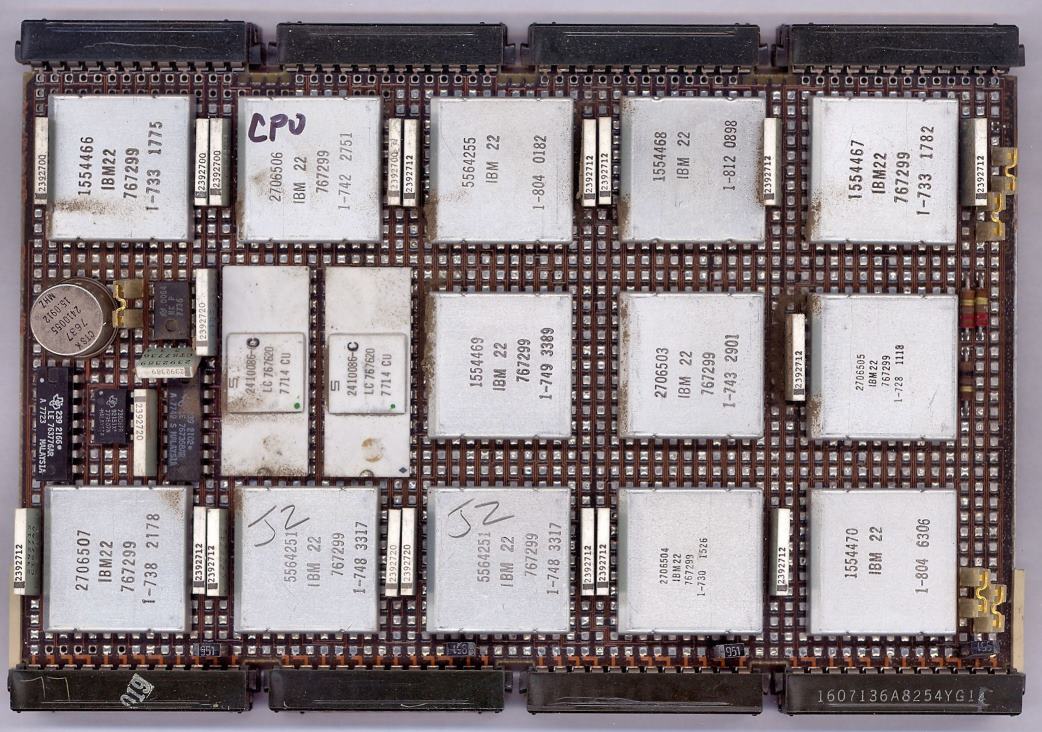

2.7.2015 - Scheda della CPU di un mainframe IBM System/370 modello 145, con circuiti MST (questo esemplare è del 1982). Si noti che alcuni moduli riportano la sigla "CTS".

Questa scheda SLT del 1971 proveniente da un lettore/perforatore di schede IBM 129 Card Data Recorder (vedi), successore del diffusissimo modello 029 commercializzato ai tempi del System/360. Contiene 6 shift-register dinamici da 480 bit, per un totale di 5.760 bit corrispondenti a 960 caratteri EBCDIC con codifica a 6 bit per carattere. 960 caratteri rappresentano la "capacità" di una singola scheda perforata IBM a 96 colonne (per 10 righe), formato alternativo rispetto alle tradizionali 80 colonne, introdotto nel 1969 assieme al minicomputer System/3 ed al Data Recorder 5496. Il medesimo tipo di shift register sono stati usati anche nel terminale 3277 (appartenente alla famiglia IBM 3270). Gli shift-register sono un esempio di memoria seriale. Durante i primi anni Settanta essi presero il posto, nel settore delle macchine da ufficio, delle memorie a linea di ritardo magnetostrittive impiegate ad esempio nei terminali IBM 2848 e 2260. Il terminale Datapoint 3300 impiegava 44 shift-register da 200 bit ciascuno per una capacità complessiva di 1.800 caratteri a 6 bit, ovvero 25 righe per 72 colonne di testo. In queste applicazioni essi erano anche chiamati "buffer circolare" o "memoria circolare" (imperfetta traduzione dell'inglese "circulating memory"). Gli shift-register visibili qui sono stati fabbricati nel 1971 dalla AMi con processo PMOS e sono equivalenti al tipo S1685. Contenuti in package metallico TO-8 a 12 pin, funzionano ad una frequenza massima di 1 MHz e sono compatibili coi livelli di segnale TTL a 5 V.

Pagina in cui si parla dell'AMI S1685: http://www.oldatheart.co.uk/computers.html.

Anche: http://www.trevormarshall.com/byte_articles/byte18.htm.

Schede SLT dell'IBM 129 tra cui una identica a questa: http://en.wikipedia.org/wiki/Keypunch#/media/File:IBM_129_SLT_modules.jpg.

Altro esempio di schede (MST) con shift-register AMi da 480 bit di capacità, provenienti probabilmente dalla logica di controllo di un terminale (1973).

Chip di DRAM CMOS da 1 Mbit fabbricato da IBM negli stabilimenti di Poughkeepsie incluso in una placchetta adesiva pubblicitaria (1987). IBM è stata il primo produttore di calcolatori elettronici ad introdurre nei propri sistemi commerciali chip di memoria di questa capacità. I primi calcolatori IBM che li hanno impiegati sono stati quelle della serie 43xx.

This 1 Mbit CMOS DRAM chip, made by IBM at Poughkeepsie around 1987, is encased in a transparent adhesive "bubble" of resin. A nice tech gift for IBM’s salesmans. Big Blue pioneered the use of such DRAMs in commercial systems (43xx).

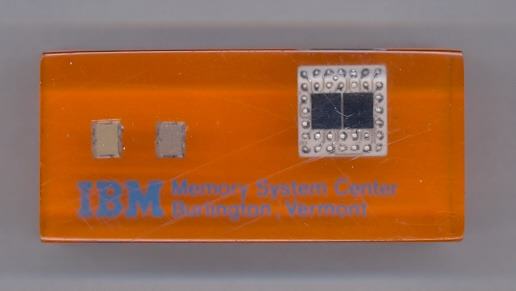

Piccolo fermacarte in plexiglass contenente due chip di DRAM da 32 e 64 kbit ed un modulo di memoria con 4 di questi chip, tutti fabbricati presso il Memory System Center dell'IBM a Burlington (Vermont, USA). Circa 1978.

Fermacarte dell'IBM General Systems Division con due chip di memoria DRAM, rispettivamente da 32 e da 64 kbit (circa 1978). Entrambi usati nel System/36 e nel System/38.

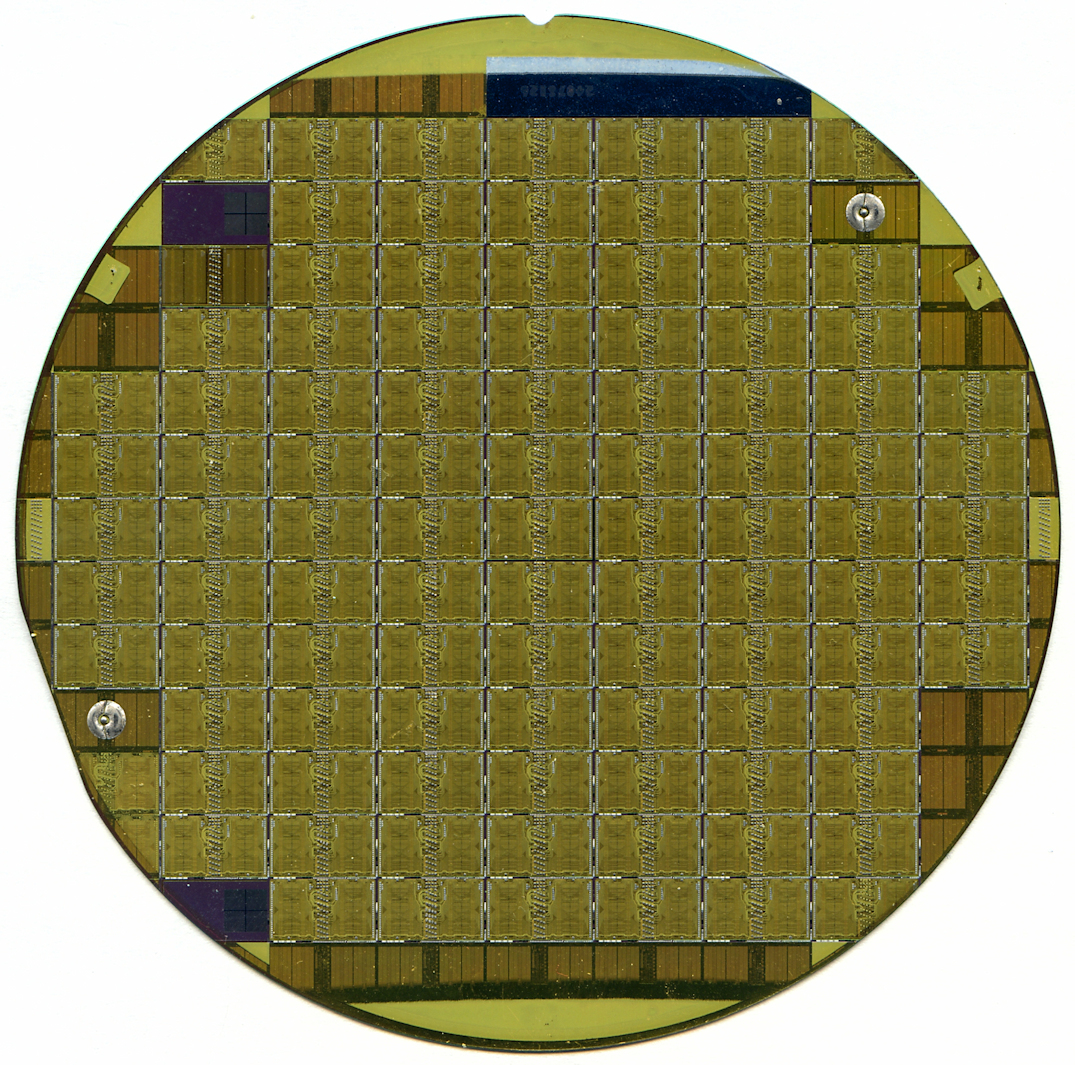

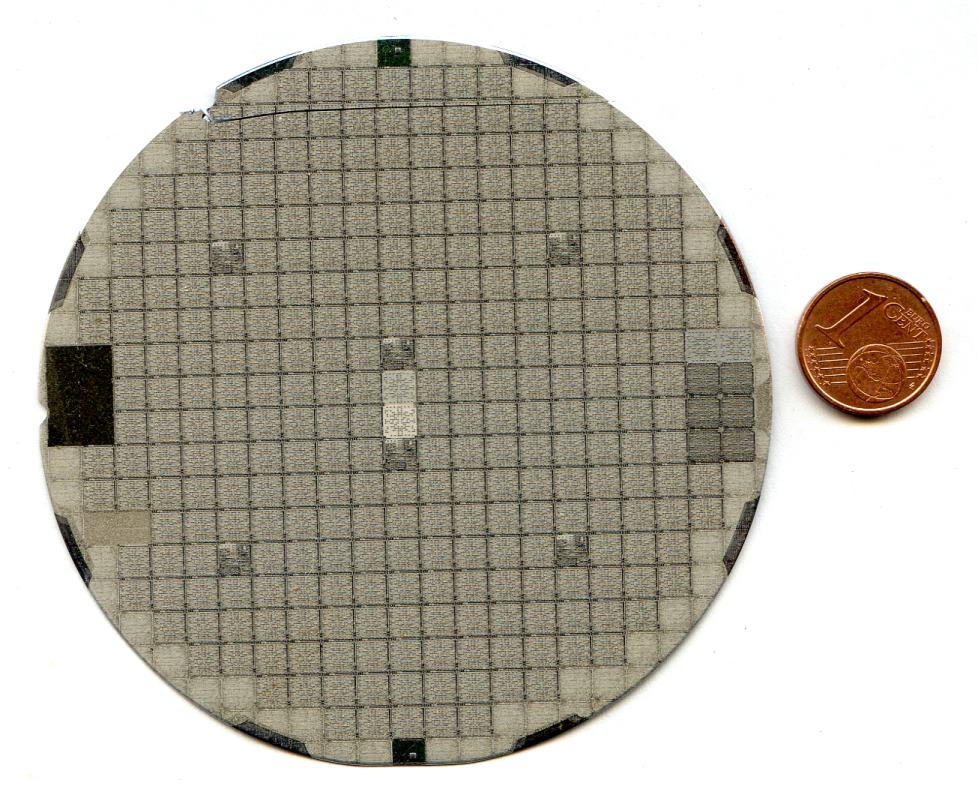

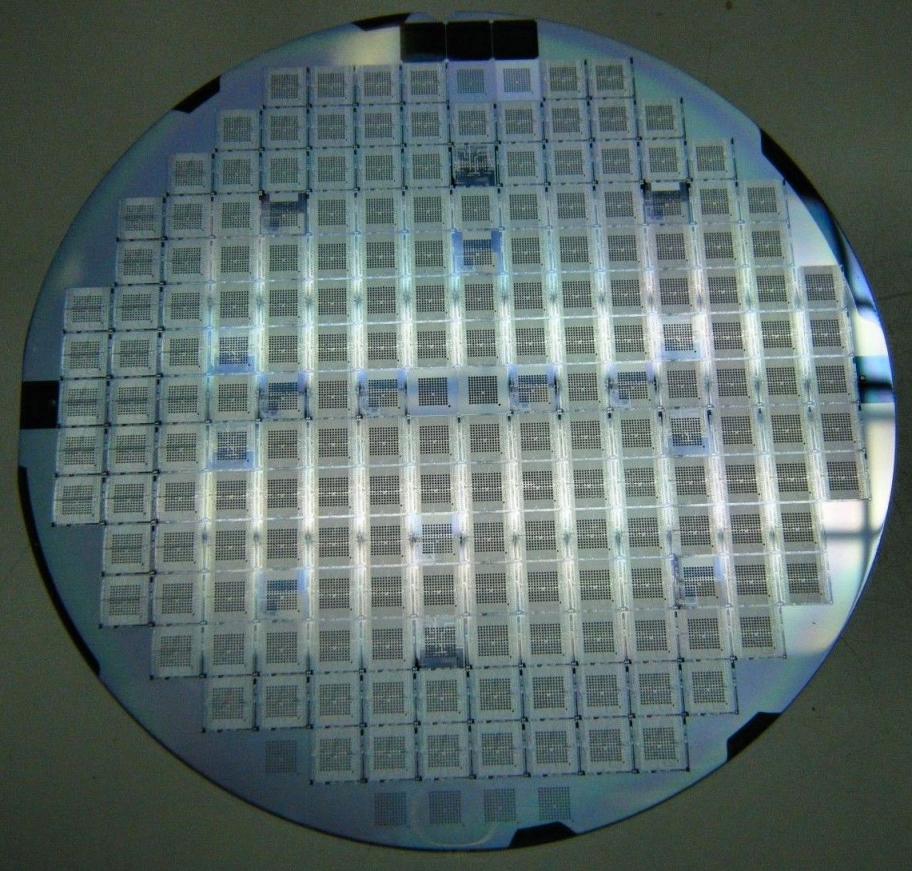

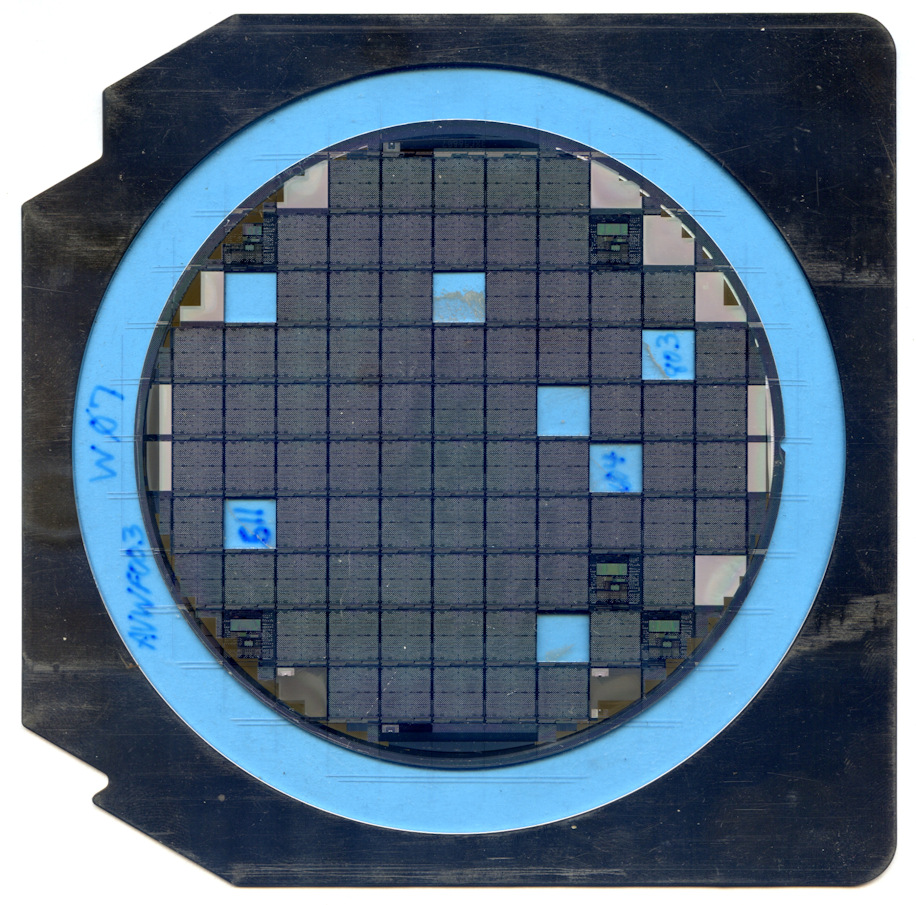

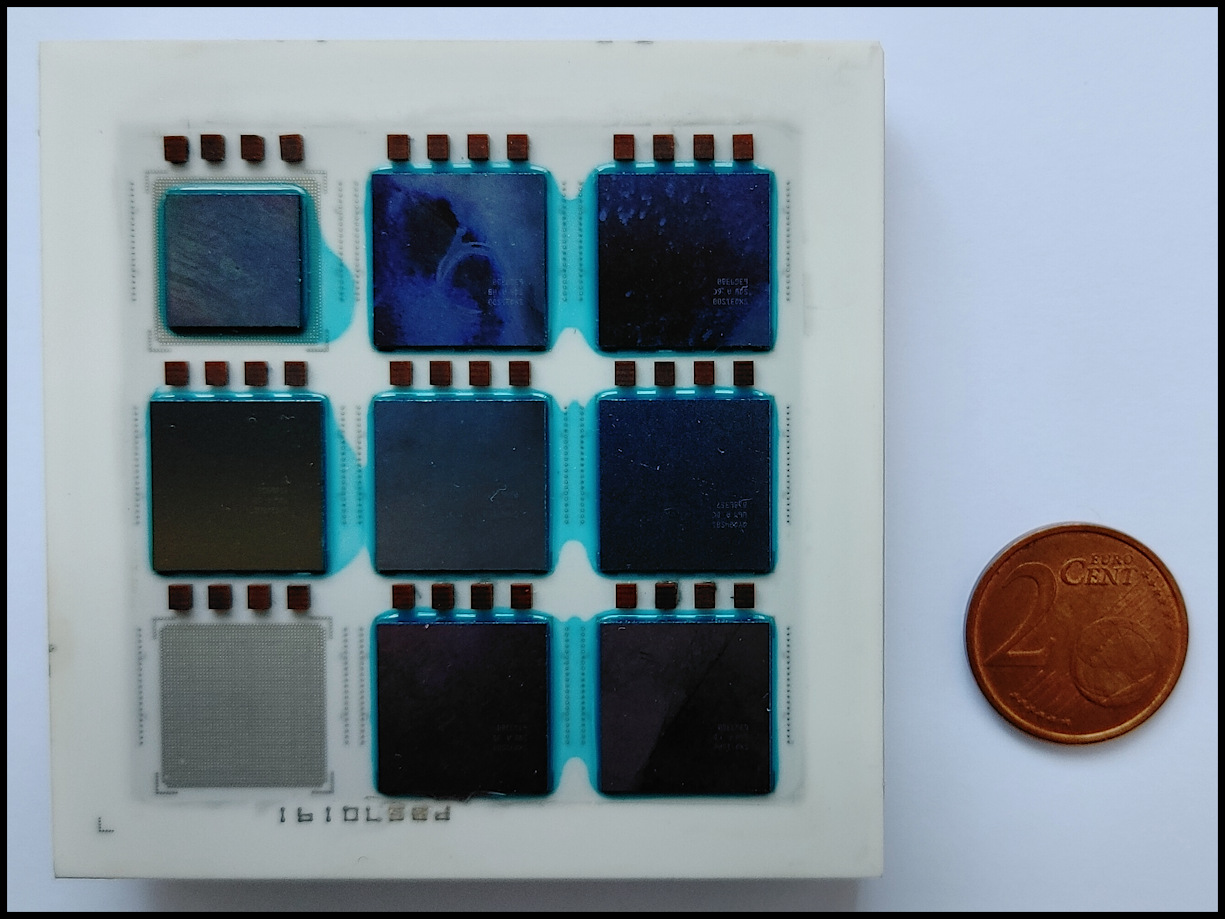

Wafer da 3 pollici (proveniente dallo stabilimento IBM di Bromont) con memorie DRAM MOS da 288 kbit, 1987/8, probabilmente prototipi o pre-produzione.

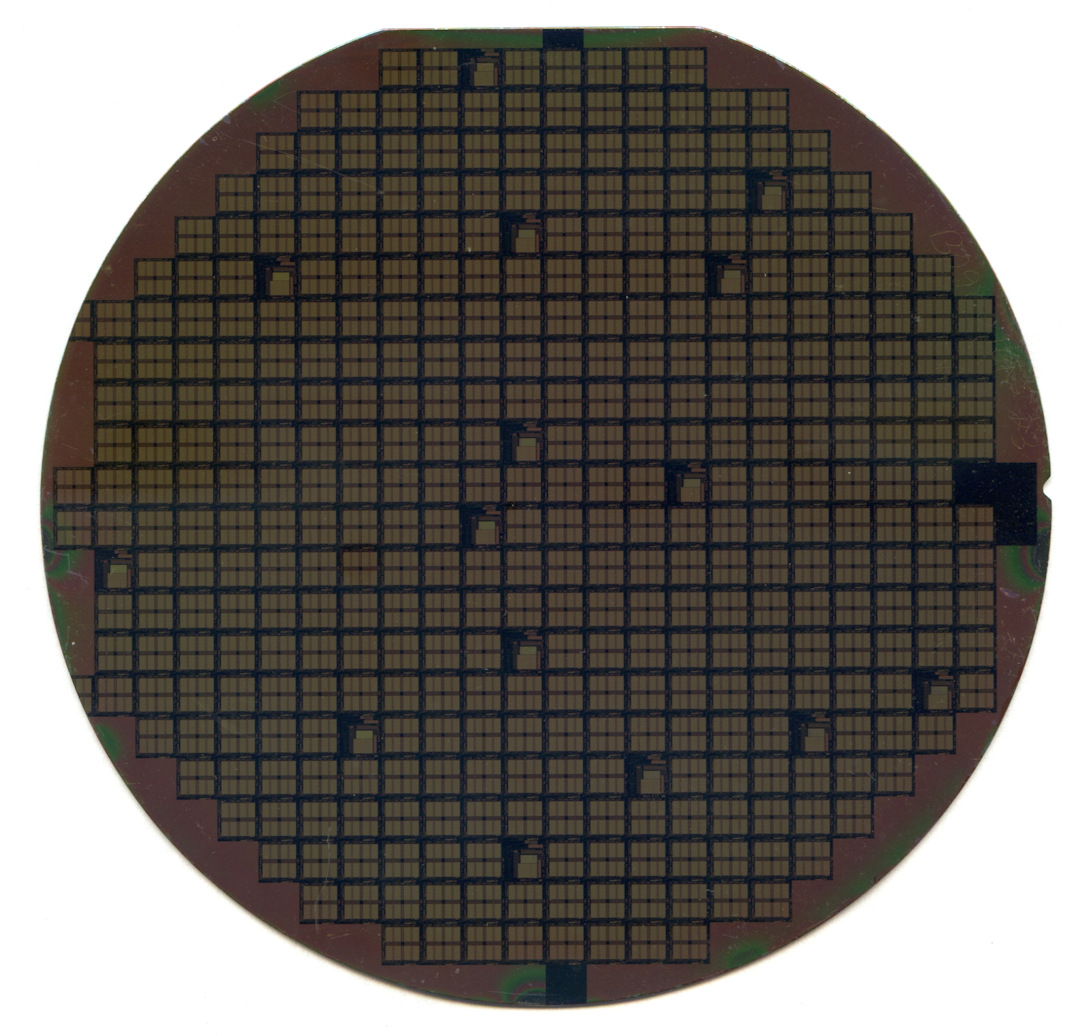

Wafer di DRAM IBM, probabilmente da 256 kbit, circa 1989.

Prototipi di memorie DRAM IBM da 16 Mbit, circa 1995, modello Luna-C. Si tratta della versione con ECC incorporato della più comune Luna-ES. E' fabbricata con processo CMOS DD3, 5 Volt (ne esiste anche una versione a 3,3 Volt) e l'organizzazione della memoria è 4M×4 (cioè 4.096K parole di memoria da 4 bit -o 1 nibble- ciascuna).

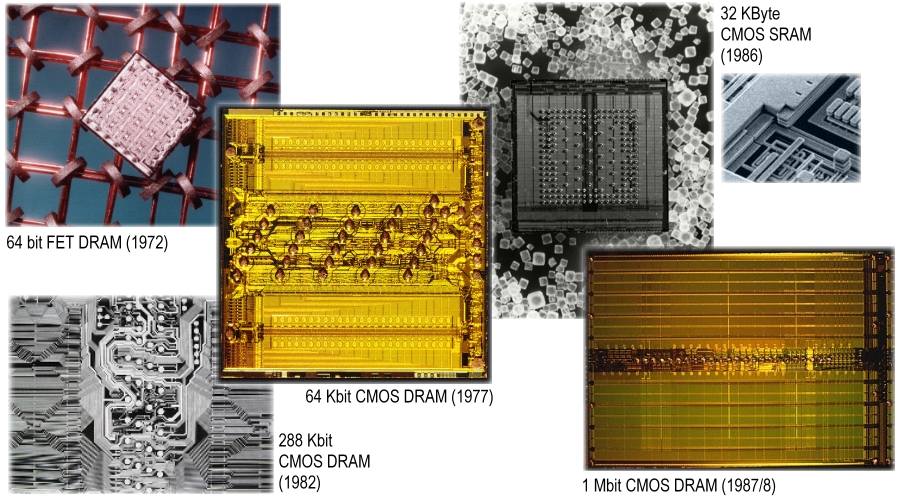

Sintesi delle principali tappe dell'evoluzione delle RAM fabbricate da IBM, dal 1972 al 1987 (introduzione della prima DRAM CMOS da 1 Mbit). Le DRAM da 1 Mbit sono state impiegate per la prima volta nel Disk Cache Subsystem IBM 3990 (il primo computer a farne uso è stato il 4341, vedi sopra).

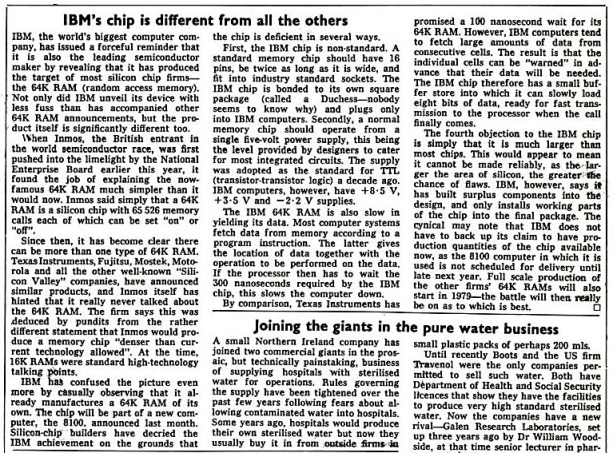

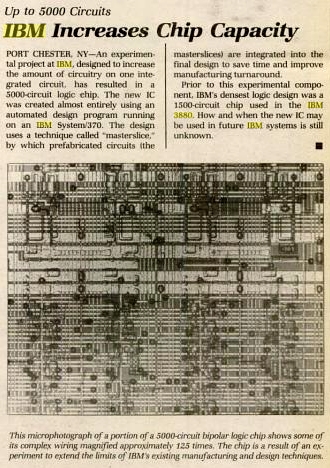

Articolo apparso nel 1978 sulla rivista New Scientist che annuncia l'avvio da parte di IBM della produzione di chip DRAM da 64 Kbit, 300 ns.

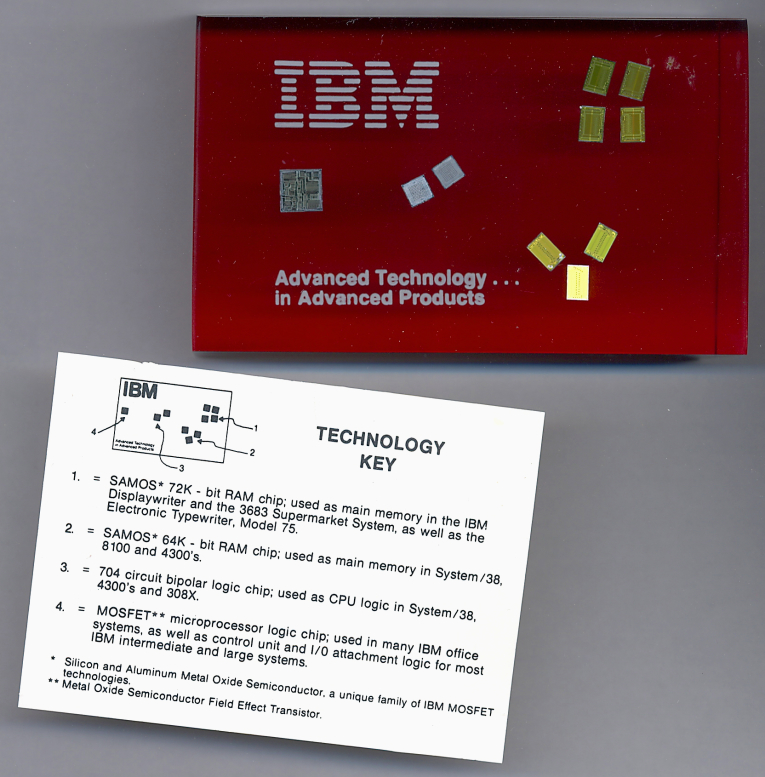

Fermacarte promozionale contenente alcuni chip sviluppati da IBM alla fine degli anni Settanta. A destra si vedono 4 chip DRAM CMOS da 64 kbit (vedi immagine più sopra). Al centro ci sono tre chip DRAM da 32 kbit. I due chip a sinistra sono microprocessori MOS impiegati in alcuni prodotti IBM. Esistono più versioni di questi fermacarte, realizzate a scopo pubblicitario in anni diversi, che contengono chip diversi (vedi ad esempio questa pagina) ed hanno diverso colore (rosso oppure blu). Lo stabilimento IBM menzionato in questo esemplare del 1978 è quello di Manassas, in Virginia, nel quale si producevano memorie ed altri integrati logici. I chip di memoria da 32 e 64 kbit sono stati impiegati, ad esempio, nei calcolatori IBM 4341 e 4361. Tutti questi componenti erano fabbricati col processo SAMOS sviluppato dalla stessa IBM nella seconda metà degli anni Settanta: "SAMOS" è l'acronimo di Silicon and Aluminium MOS.

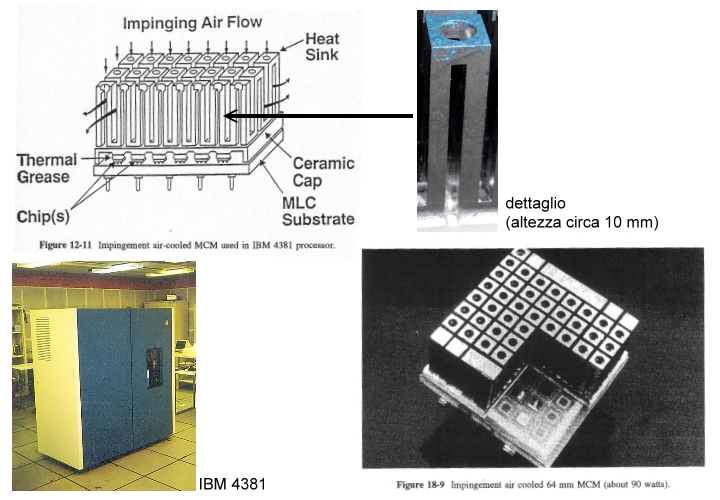

Fermacarte IBM (circa 1988) con diversi tipi di integrati: al centro, due memorie da 4 Mbit. A sinistra un circuito CMOS VLSI del tipo impiegato ad esempio nelle macchine PS/2. Sotto, due integrati utilizzati nella CPU 4381.

Altro esempio di fermacarte IBM con chip diversi dal precedente. Una delle memorie (in particolare quella a sinistra) sembra essere una DRAM da 8 Mbit.

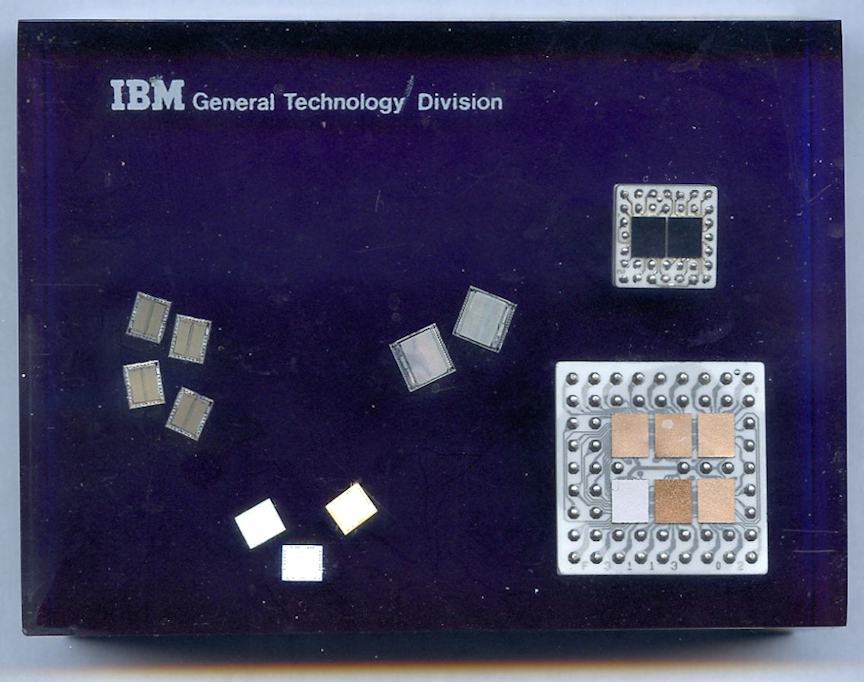

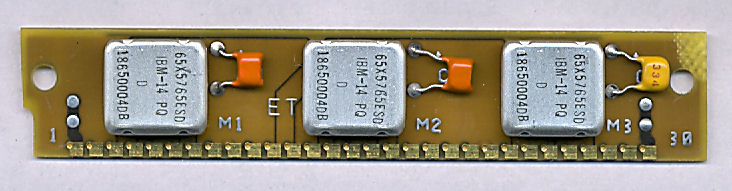

Fermacarte dell'IBM General Technology Division con esemplari di DRAM NMOS da 16, 32 e 64 kbit, circa 1986. A destra due moduli (MST) completi. Quello in alto può ospitare 2 o 4 chip di memoria (due per lato).

26.4.2015 - Portachiavi promozionale con modulo MST e 4 chip fabbricati con la medesima tecnologia.

Portachiavi con chip di DRAM da 64 Kbit utilizzato nell'IBM System/38.

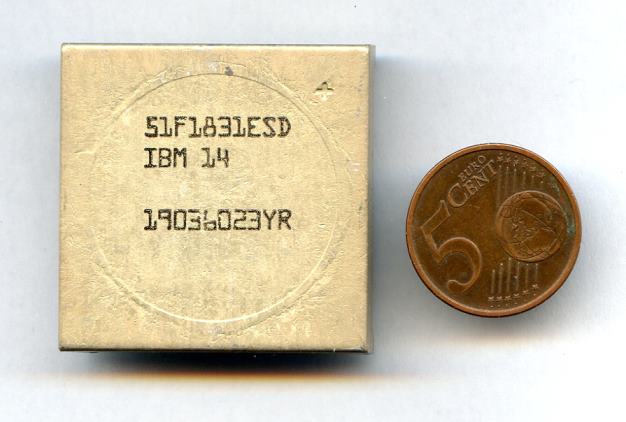

Portachiavi con chip logico TTL LSI impiegato nei "mini-mainframe" della famiglia IBM 4300.

Wafer IBM da 2,5 pollici con integrati logici MST. Questo esemplare è datato 1982 e proviene dagli stabilimenti di East Fishkill.

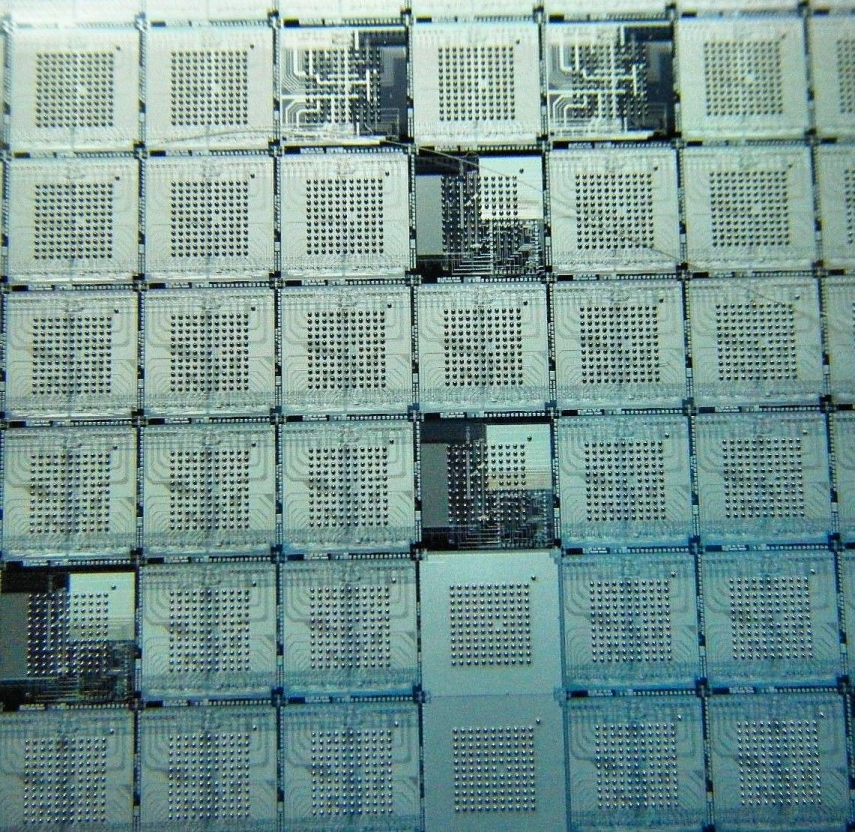

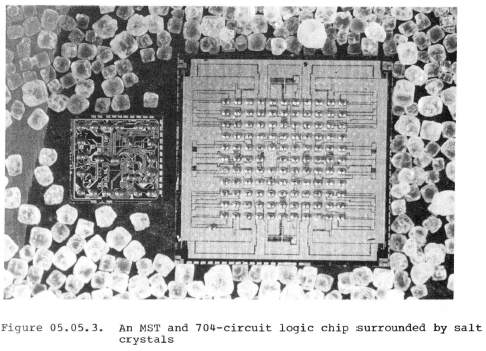

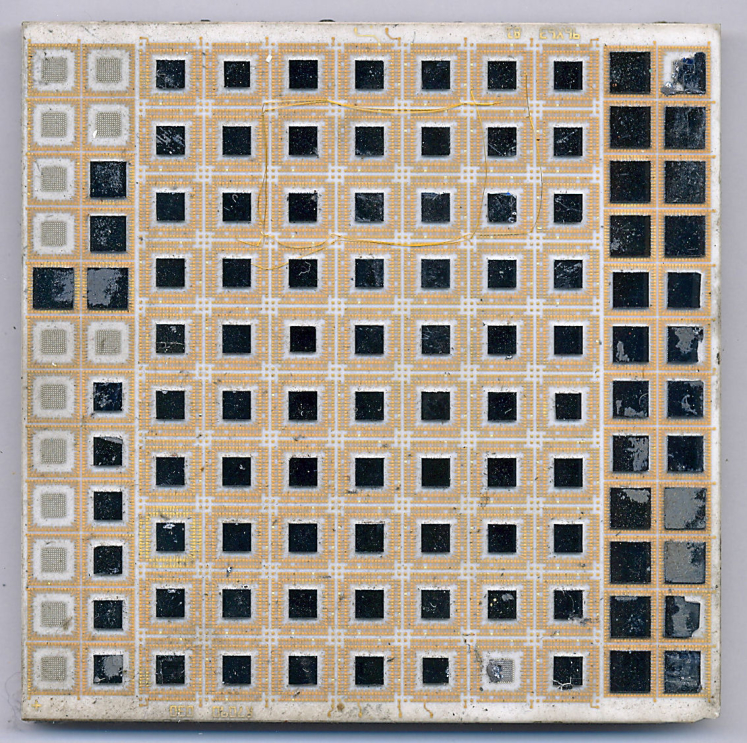

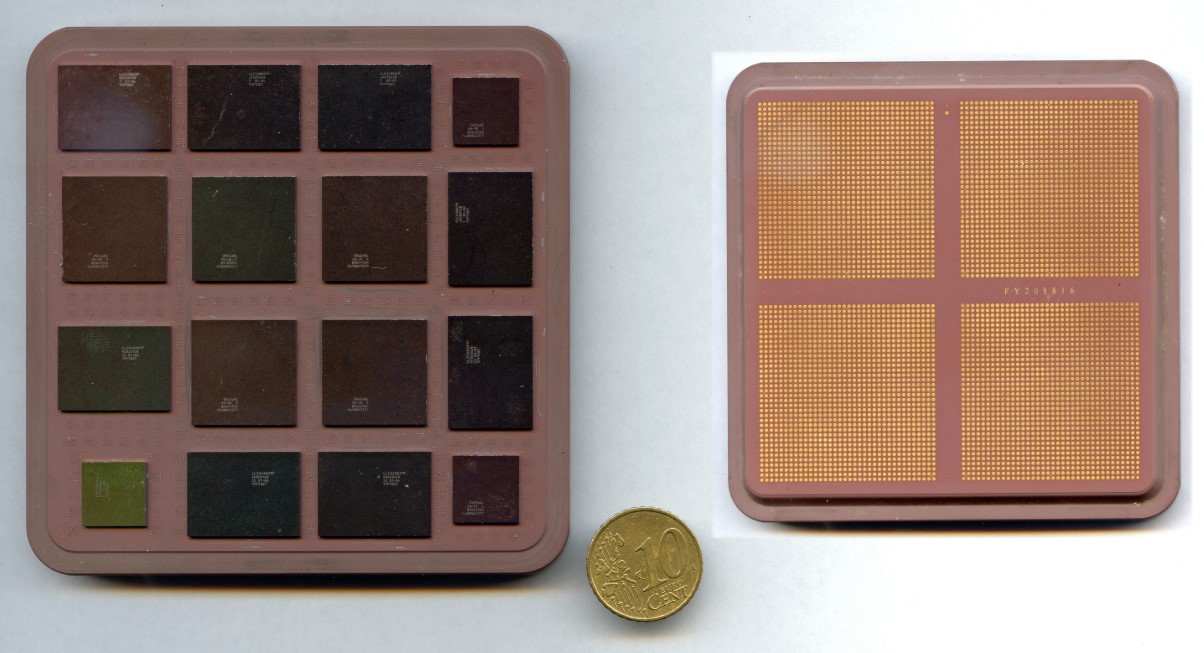

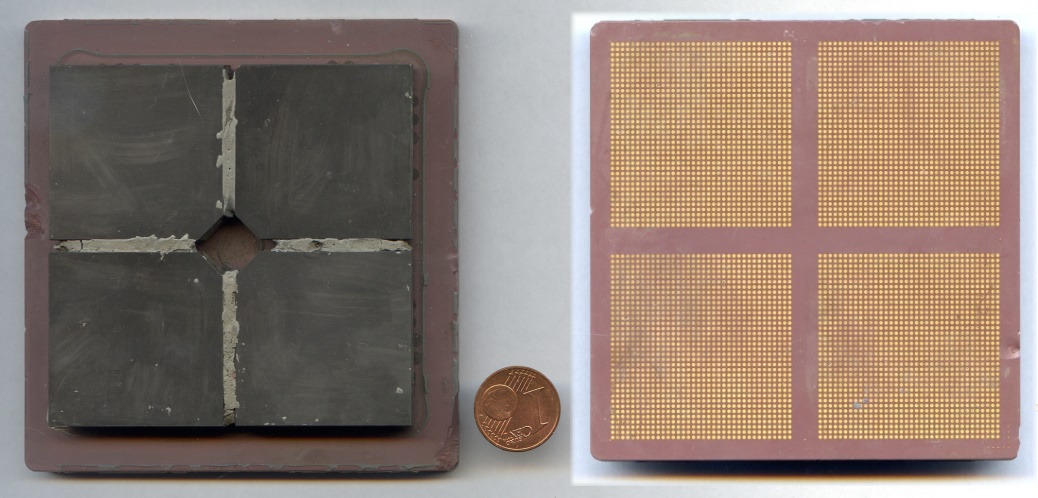

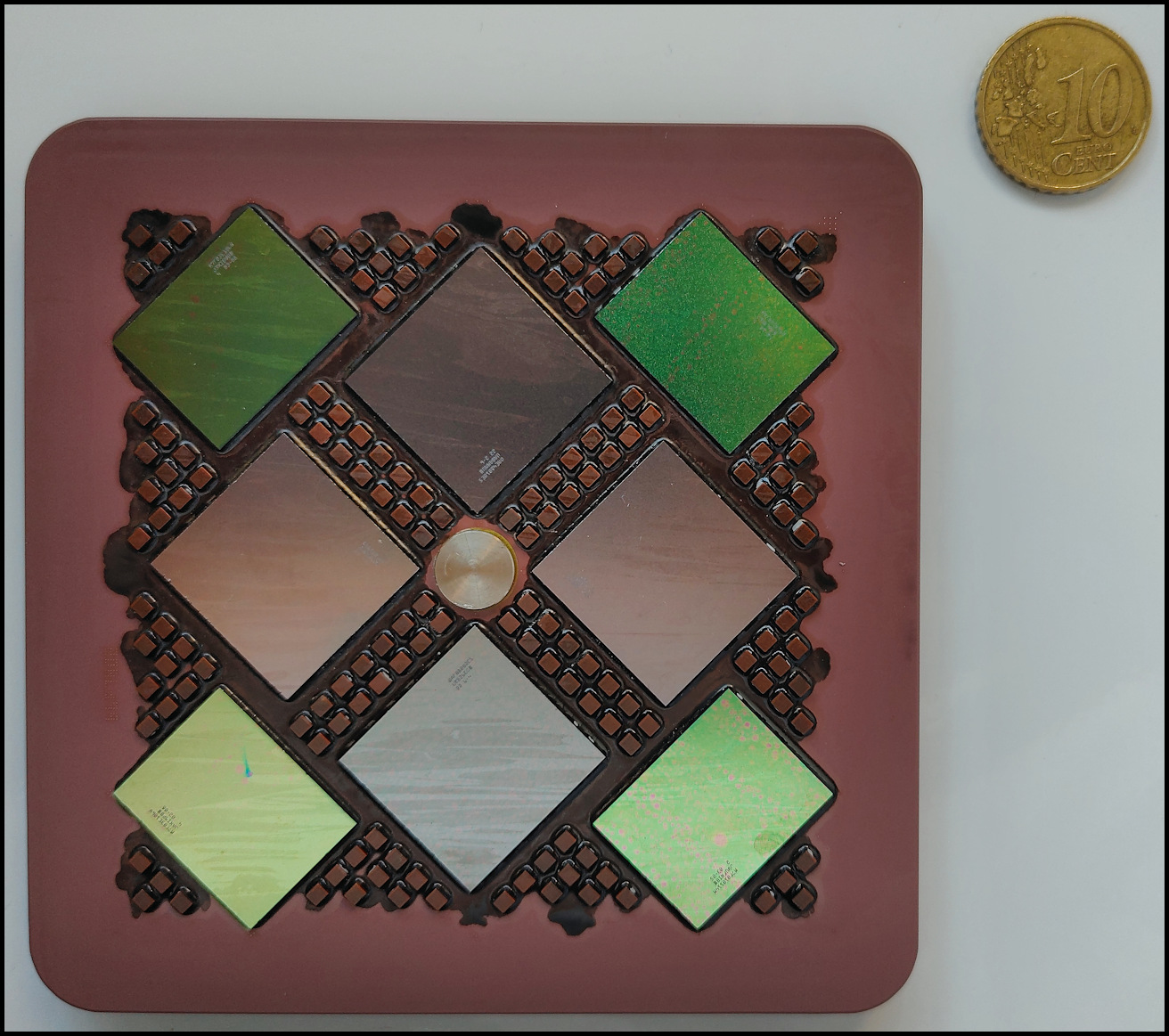

Wafer da 3 pollici di integrati logici TTL LSI fabbricato negli stabilimenti IBM di East Fishkill, circa 1983 (stando alle informazioni del venditore). Questi integrati vengono montati con la tecnica flip-chip denominata C4 (Controlled-Collapse Chip Connection: vedi http://en.wikipedia.org/wiki/Flip_chip). Il wafer proviene dalla collezione personale di un ex impiegato IBM.

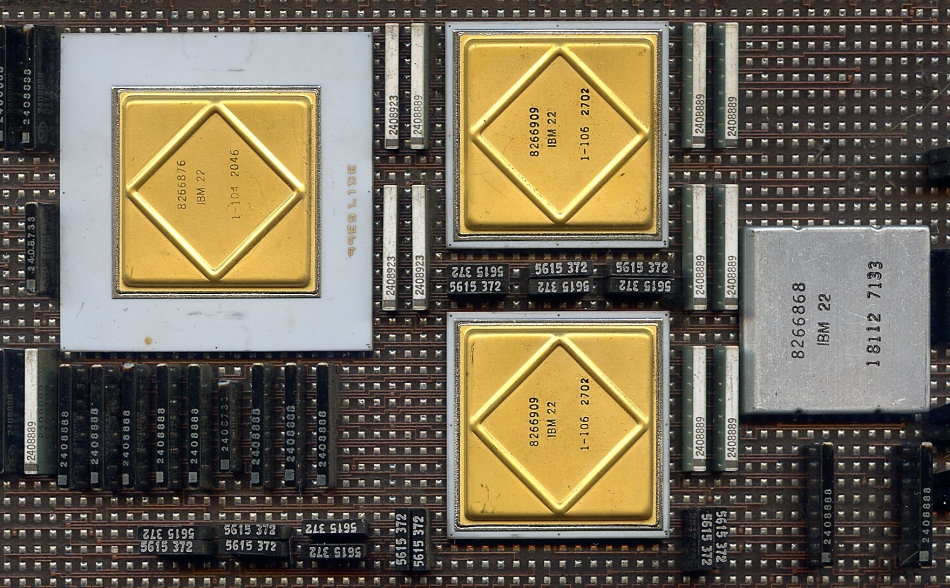

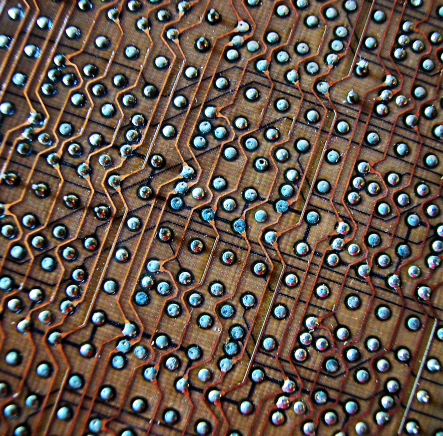

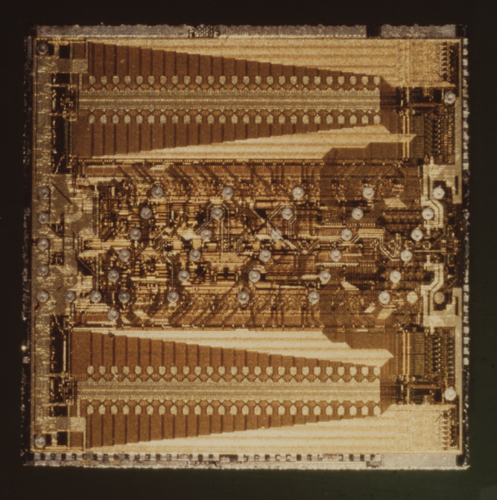

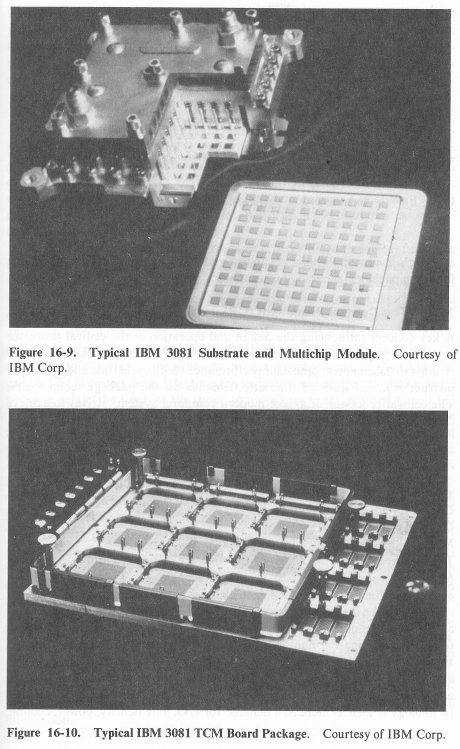

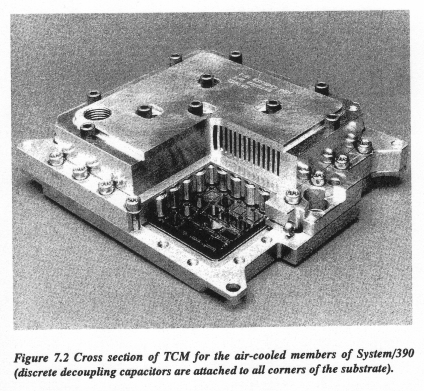

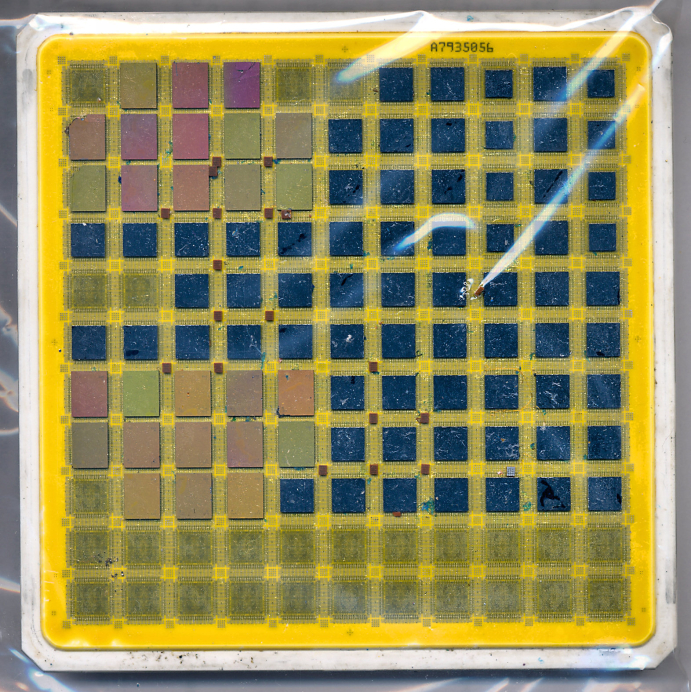

Dettaglio di una parte del wafer IBM riprodotto più sopra, in cui si vedono meglio sia i diversi livelli di interconnessione/metallizzazione, sia le microsfere (solder ball) che servono come punti di contatto tra il chip ed il substrato nel package, e che in fase di saldatura vengono fuse oppure fatte collassare mediante impulsi di ultrasuoni di frequenza ed intensità appropriate (ultrasonic bonding) oppure ancora mediante combinazione di calore ed ultrasuoni (thermosonic bonding). Le dimensioni dei singoli chip sono circa 4x4 millimetri. Un capello presente nella parte alta dell'immagine dà un'idea della dimensione delle solder ball (nell'ordine dei centesimi di millimetro). La metallizzazione è in Alluminio. Circuiti di questo tipo sono stati impiegati, ad esempio, nei mainframe IBM 3081 e 43xx e nell'IBM System/38. La complessità logica massima è di 704 gate per chip.

Vedi: http://flipchips.com/tutorial/bump-technology/solder-bump-flip-chip/.

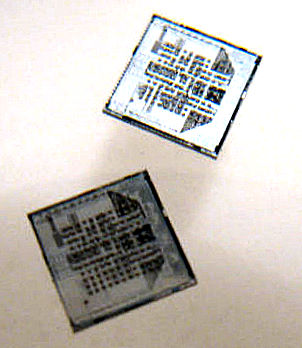

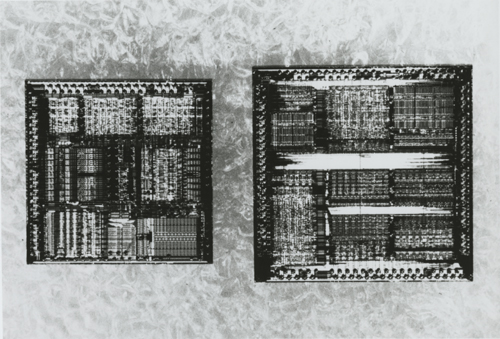

Questa immagine, tratta da questa pagina web, raffigura due chip logici IBM bipolari da 704 gate simili a quelli nel wafer visibile sopra. I chip sono contenuti in una delle diverse versioni di un fermacarte promozionale IBM in plexiglass, del tipo di quelli raffigurati in altra sezione di questa pagina.

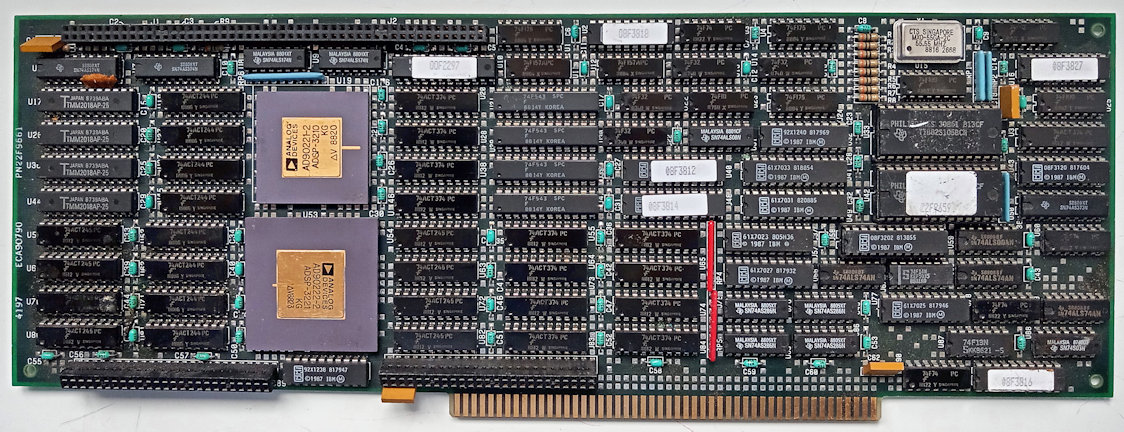

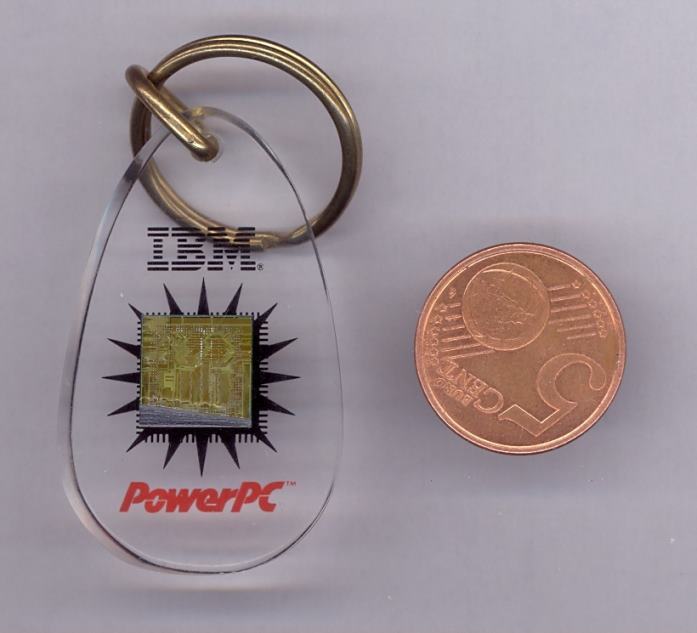

13.5.2015 - Portachiavi promozionale contenente due chip logici bipolari del tipo di quelli riprodotti più sopra. Oggetti come questo venivano offerti ai visitatori degli stabilimenti IBM (in questo caso quelli di East Fishkill) oppure, più di frequente, ai dipendenti degli stessi ed ai rivenditori autorizzati.

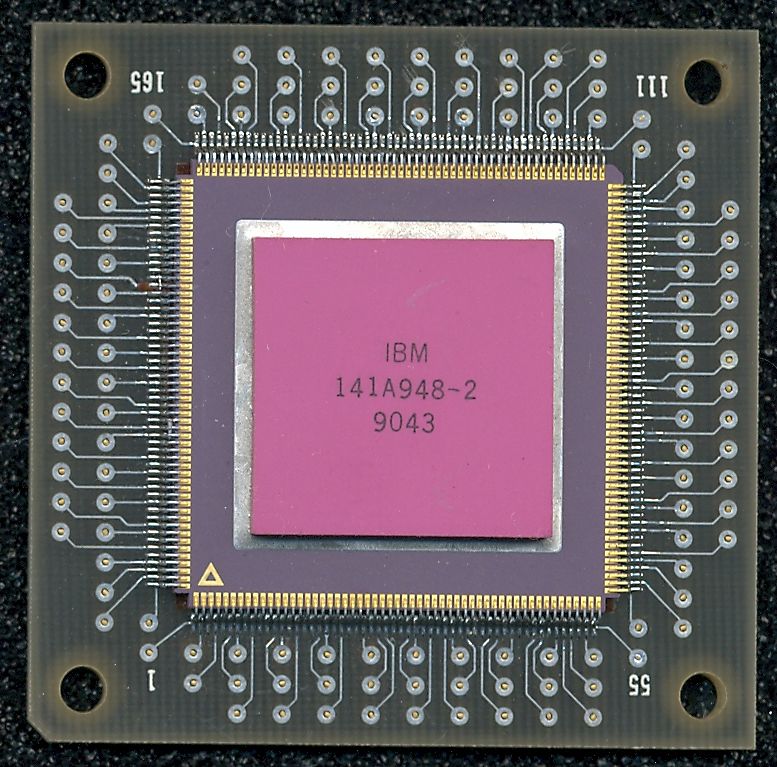

Fermacarte ricordo per i dipendenti degli stabilimenti IBM di East Fishkill contenente un chip logico bipolare fabbricato con tecnologia ATX-4 a 1 micron, utilizzato nei mainframe Enterprise System 9000 prima del passaggio alla tecnologia CMOS. "High-speed silicon bipolar technology continues to meet the demands of integrated circuits for mainframe computers. IBM has developed an advanced bipolar logic and high-speed array technology for its Enterprise System/9000™ systems. This technology, code-named ATX-4, is composed of trench-isolated, double-polysilicon self-aligned bipolar devices, and has four fully planarized wiring levels with interlevel connecting studs. Chip fabrication has been implemented in 1-μm ground rules and is in full-scale manufacturing. ATX-4 represents a significant advance in providing higher-speed and lower-power logic at increased levels of integration compared with that of the ATX-1 technology used in previous generations." (da IBM Journal of Research and Development, vol. 36 issue 5, 1992, pp. 821-828). Vedi: http://researchweb.watson.ibm.com/journal/50th/devices/brown.html. Questo esemplare è stato regalato nel 1993 ad un ingegnere IBM ora in pensione.

Wafer da 4 pollici con integrati VLSI CMOS, 1990, proveniente dalla "fab" IBM di Bromont.

Wafer di integrati VLSI CMOS fabbricati da IBM. Circa 1990.

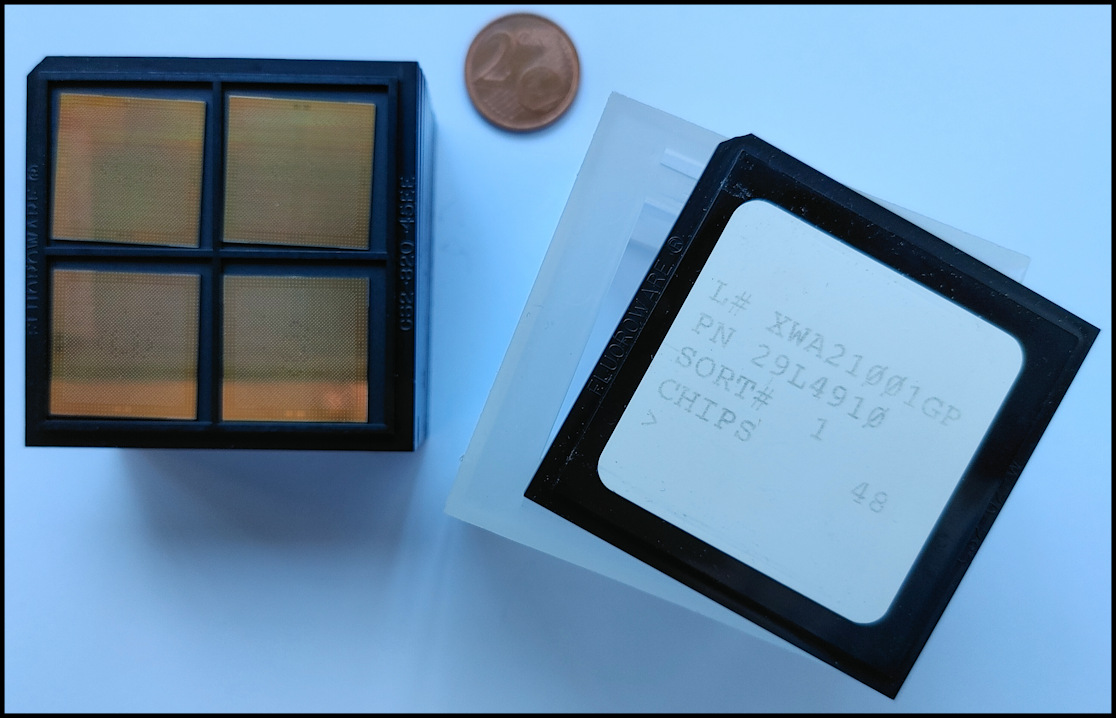

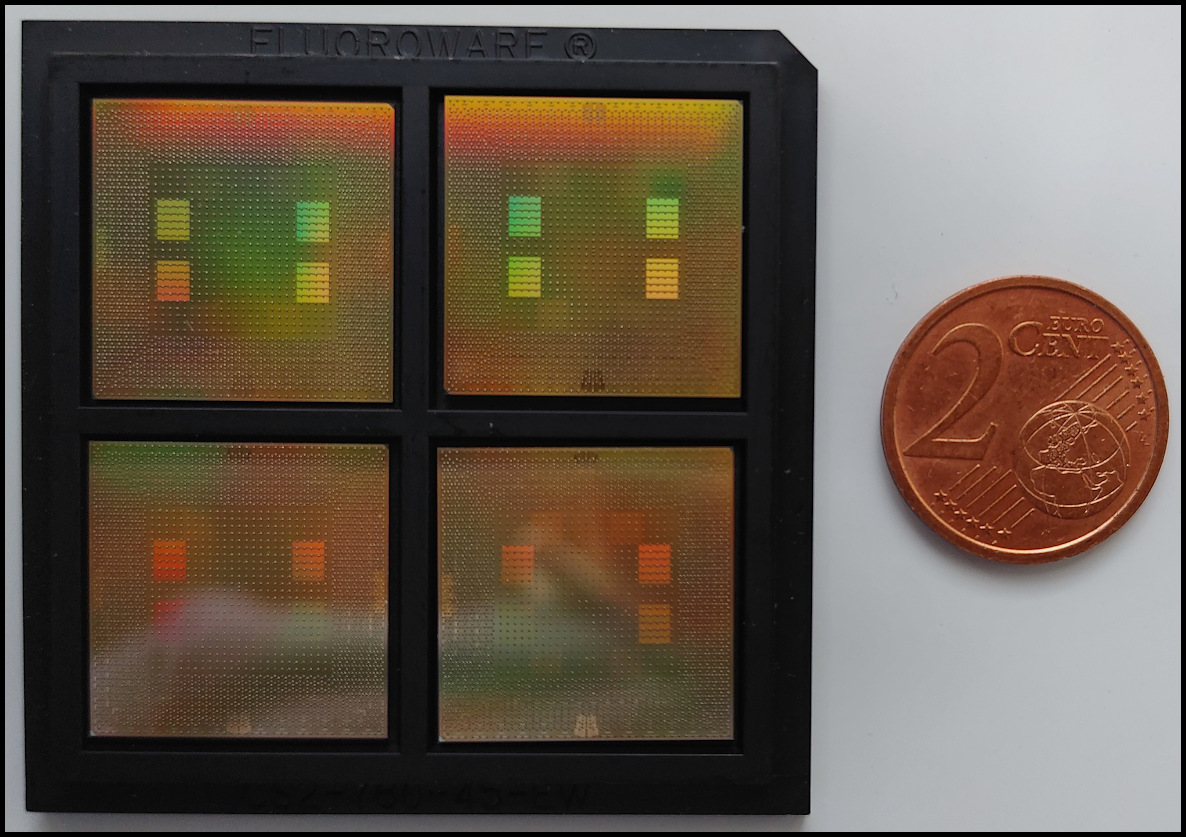

Prototipi di VLSI CMOS prodotti da IBM, forse qualche tipo di CPU, fine anni Novanta.

Prototipi di CPU IBM RS64, non conosco esattamente il modello, circa 2000/2001.

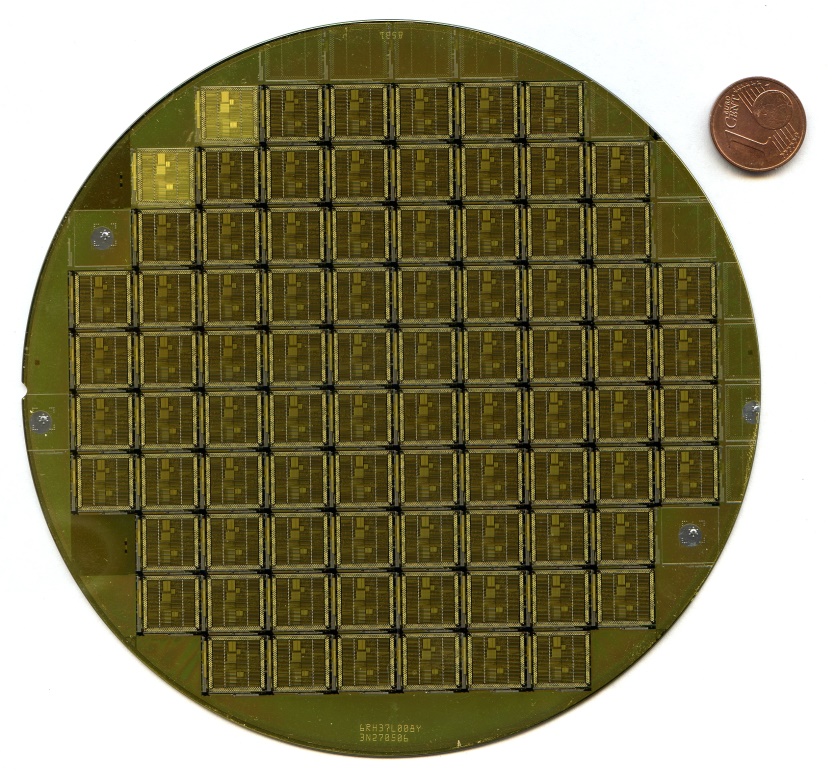

29.7.2015 - Wafer da 125 mm contenente integrati CMOS VLSI IBM, siglato "6RH37L008Y" (in basso), verosimilmente la stessa sigla dei componenti finiti e completi, e nella riga sottostante "3N270506". Apparteneva ad un ex ingegnere IBM che ha lavorato molti anni negli stabilimenti di East Fishkill. Nella parte alta si vede la sigla "8531": è la data di fabbricazione o qualcos'altro? Questo è il primo wafer IBM CMOS integro e completo, fino al livello di metallizzazione superiore, che sono riuscito ad ottenere. Che siano effettivamente integrati CMOS mi è stato assicurato da chi me l'ha venduto, che però non ha altre informazioni al riguardo.

Dettaglio di un chip del wafer riprodotto sopra. Come si può vedere si tratta con tutta probabilità di un ASIC in cui c'è una parte considerevole di logica standard cell (almeno così la vedo io) e alcune memorie. Si vedono molto bene anche i punti di saldatura (balls) con le linee di segnale e di alimentazione del package; il chip viene montato flip-chipped, cioè a faccia in giù. Entrambe le immagini sono state acquisite con uno scanner Epson; ho eseguito la scansione del wafer intero a 300 dpi mentre il dettaglio del singolo chip è a 1.200 dpi. Lo scanner non riproduce esattamente la colorazione visibile a occhio nudo, che al contrario di quanto appare tende al grigio e non al giallo. Qui sotto si può vedere, a destra, la microfotografia di un chip VLSI IBM strutturalmente simile, assieme al relativo package. La foto riuscirebbe probabilmente molto più nitida e dettagliata con un vero microscopio, che io purtroppo non possiedo...

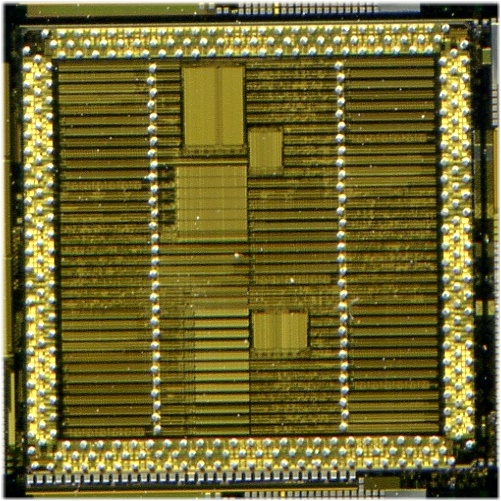

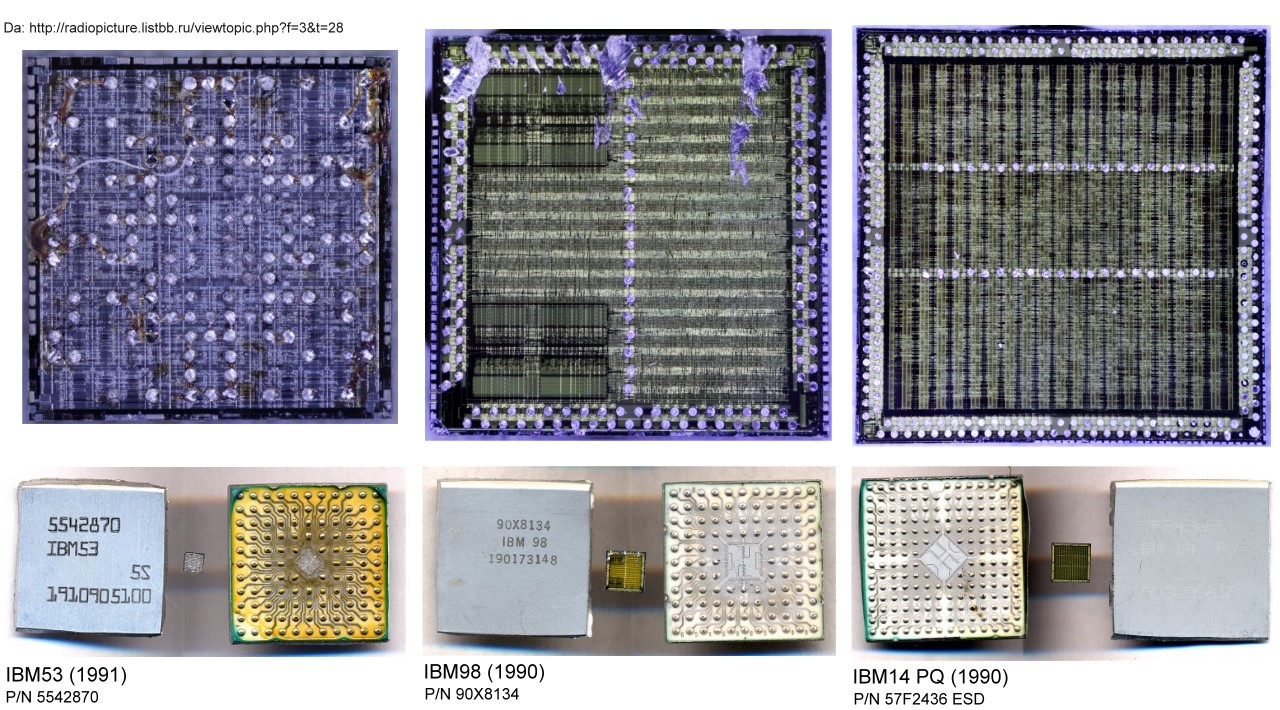

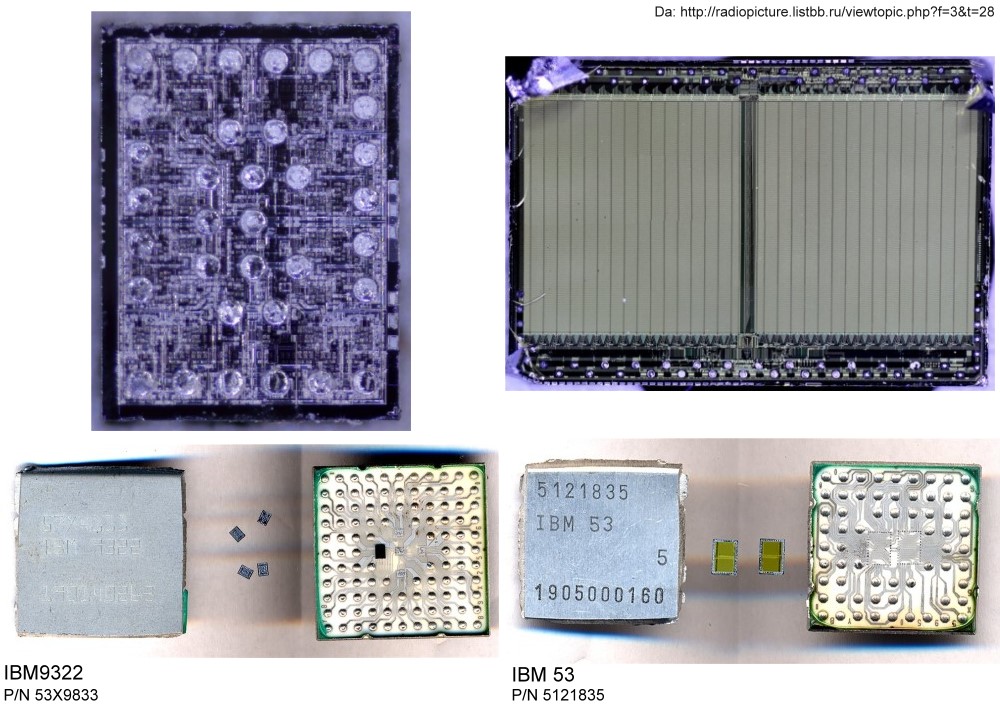

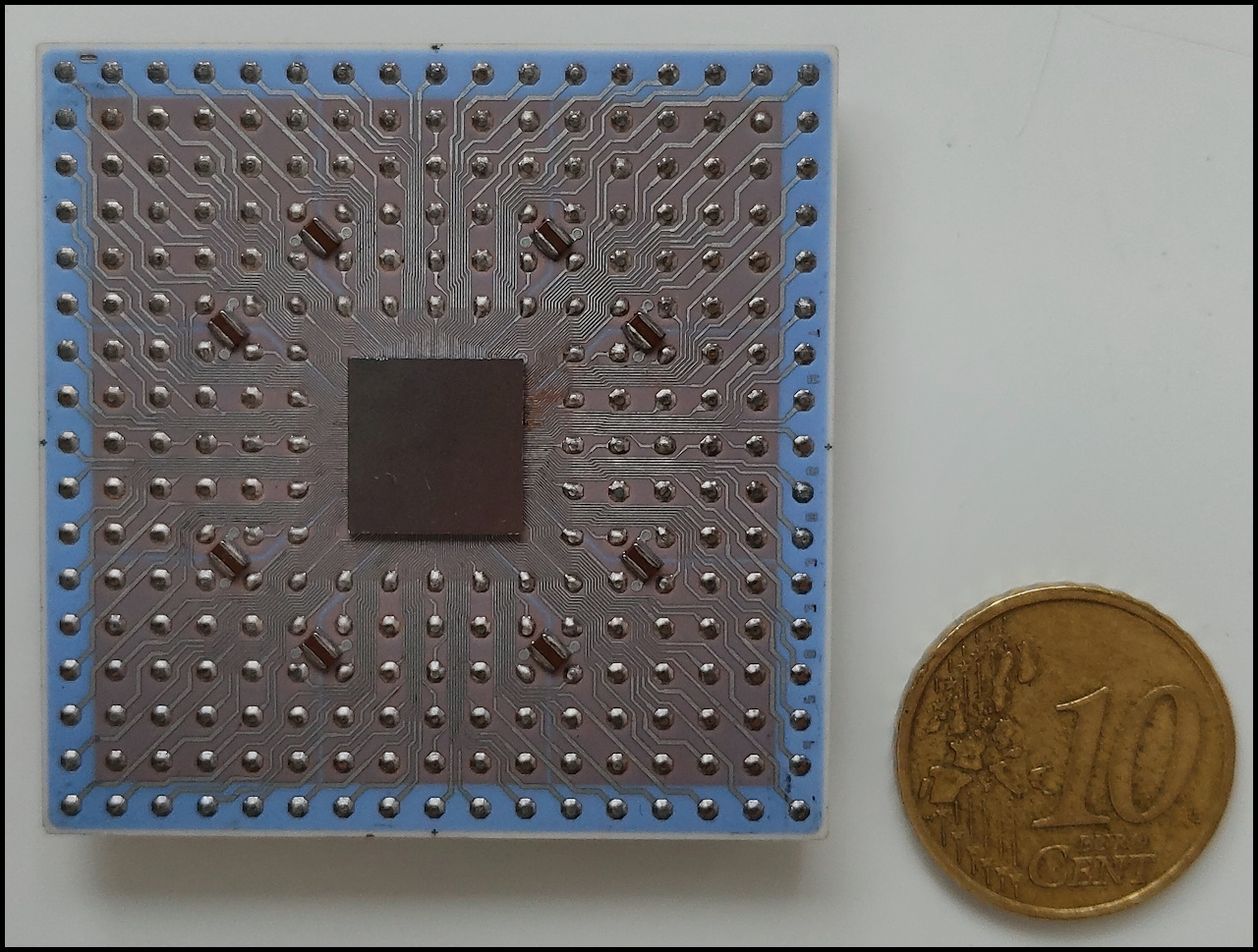

Le fotografie dettagliate di chip IBM sono rare: queste, pubblicate nella pagina http://radiopicture.listbb.ru/viewtopic.php?f=3&t=28 ed in altre dello stesso sito, sono tra le poche disponibili nel Web. L'immagine è un collage di foto eseguite da un utente del sito con una fotocamera digitale Canon EOS 500D, un tubo macro con anello di inversione, un obiettivo 50mm ed un illuminatore anulare a LED autocostruito. Le didascalie sono del sottoscritto. Come si può vedere si tratta di gate array, sicuramente (a destra) e probabilmente (al centro) CMOS, bipolari (forse) a sinistra, tutti montati con tecnologia flip-chip C4 (un brevetto IBM). Le fotografie sono molto interessanti -e ben fatte- anche perché mostrano sia il chip che il suo package ed i punti di contatto tra chip e substrato. Nella pagina Web indicata sopra è possibile vedere e scaricare le immagini a piena risoluzione, davvero notevoli.

Anche queste immagini sono tratte dalla pagina http://radiopicture.listbb.ru/viewtopic.php?f=3&t=28 (il "collage" e le didascalie sono miei). Molto interessanti perché mostrano come i moduli IBM possano contenere anche due o più chip sul medesimo substrato (ad esempio memorie RAM nel caso a destra).

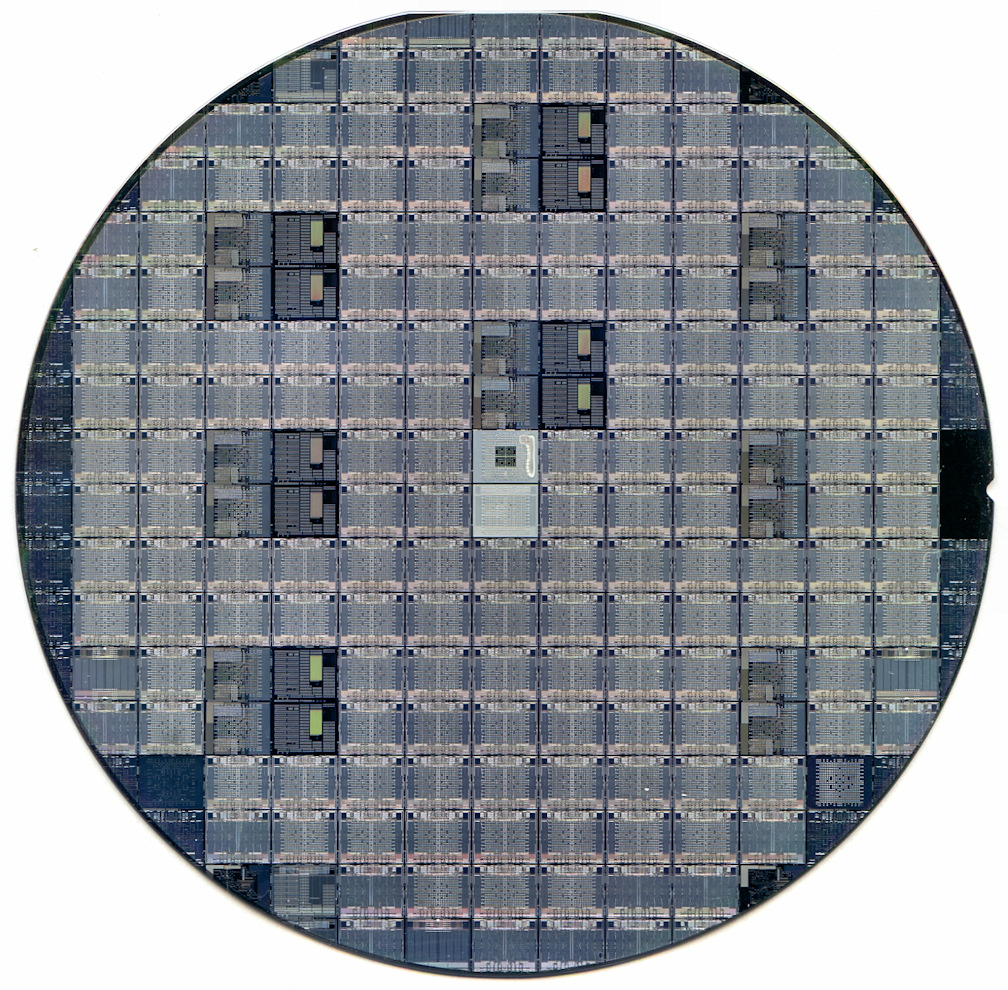

Wafer da 8 pollici proveniente dallo stabilimento IBM di East Fishkill con integrati VLSI CMOS. Sono visibili i punti di interconnessione realizzati con sferette metalliche per la saldatura ad ultrasuoni (solder bumps).

Due prototipi di integrati VLSI IBM (fine anni Novanta).

Prototipo di integrato ASIC CMOS IBM in package PGA (circa 1990), montato con la tecnica flip-chip e saldatura ad ultrasuoni.

Prototipo di ASIC CMOS IBM in package ceramico per montaggio superficiale, circa 1992, con il relativo adattatore PGA.

Prototipo di VLSI IBM (CPU?) con package Micro-PGA (circa 1999/2000).

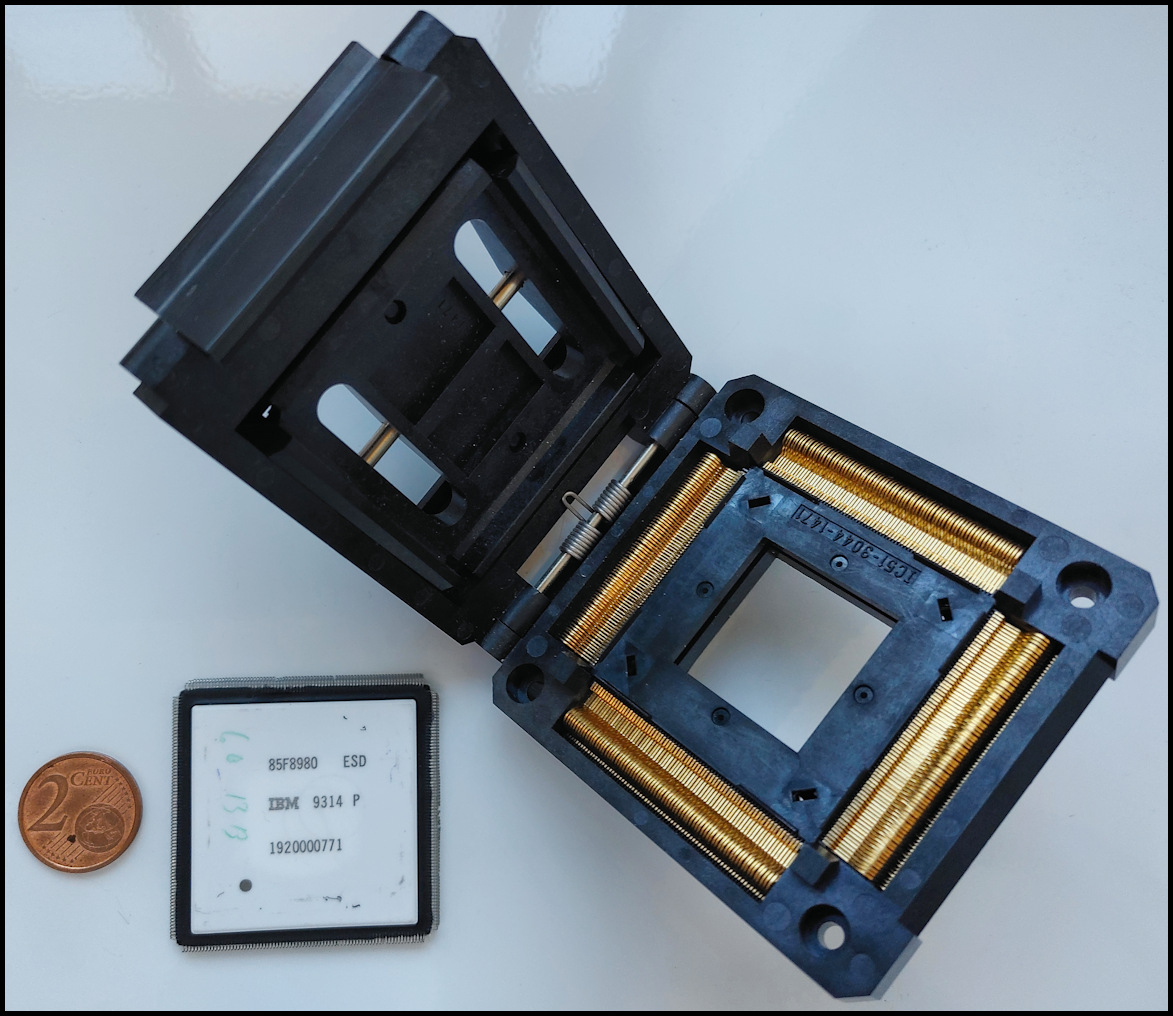

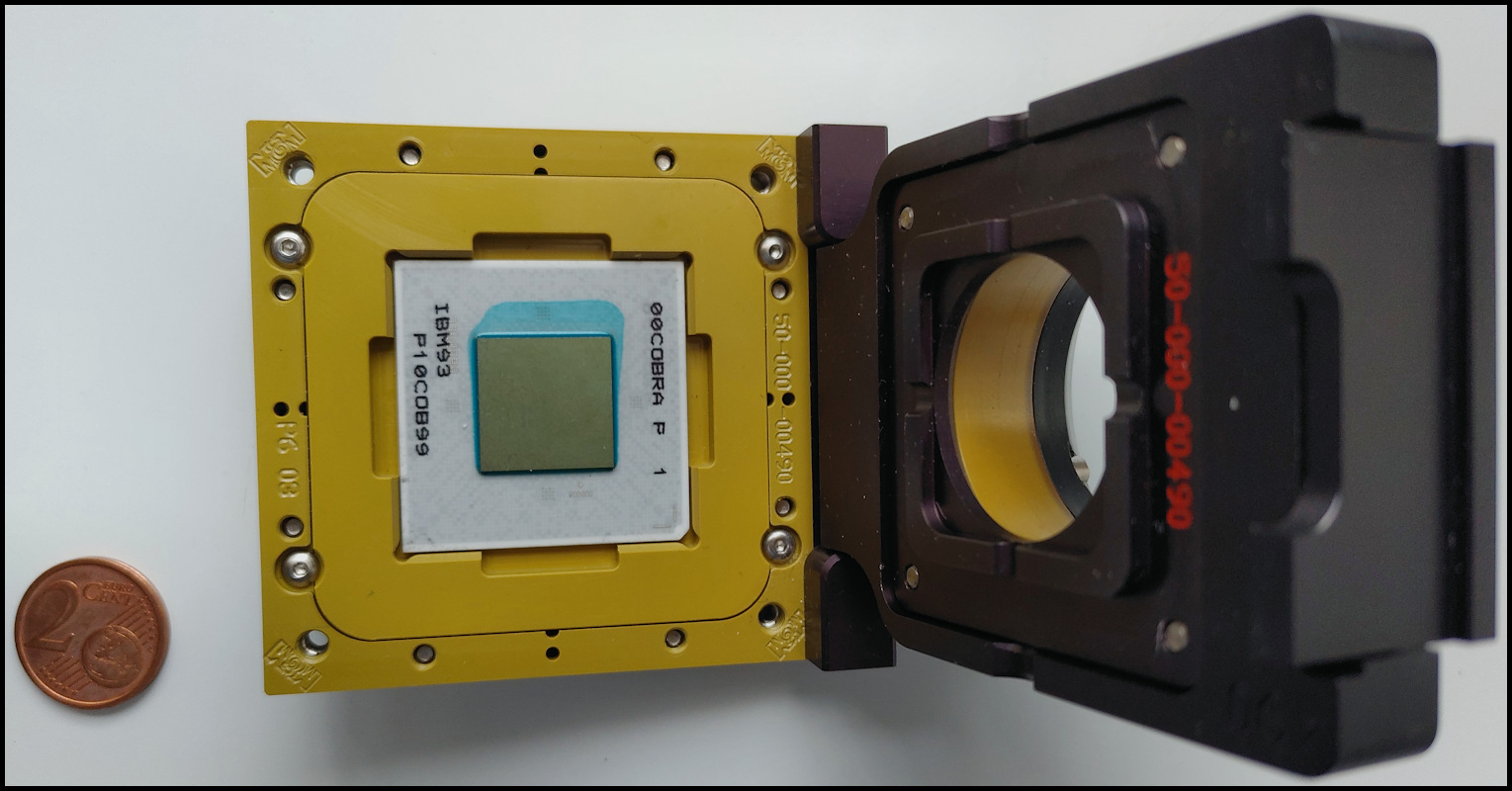

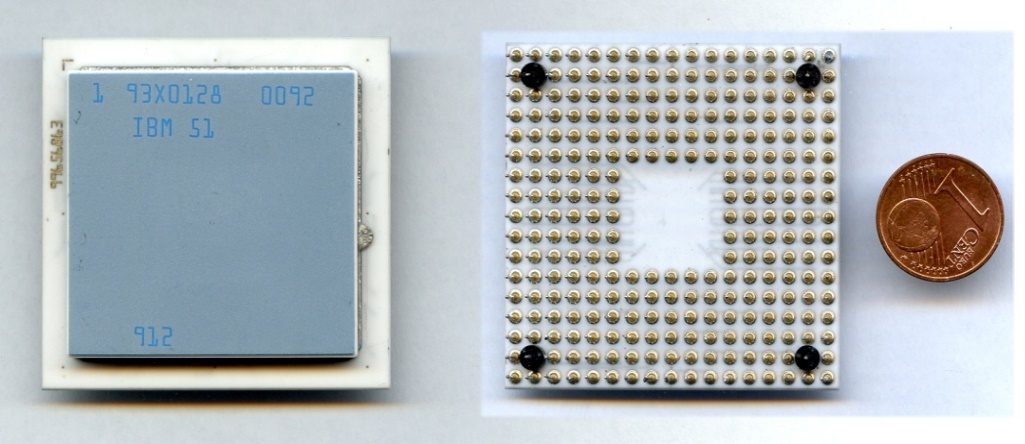

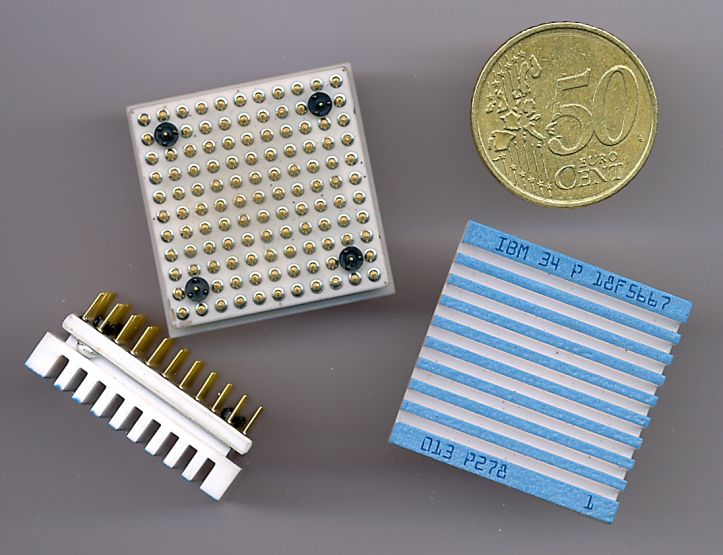

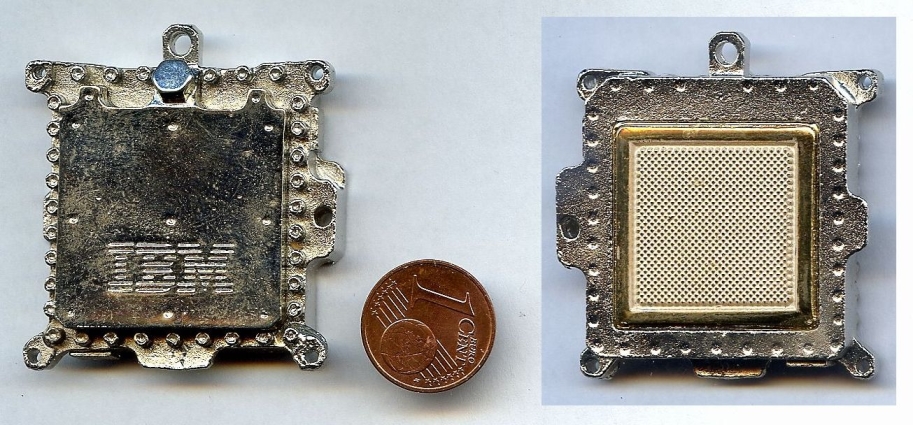

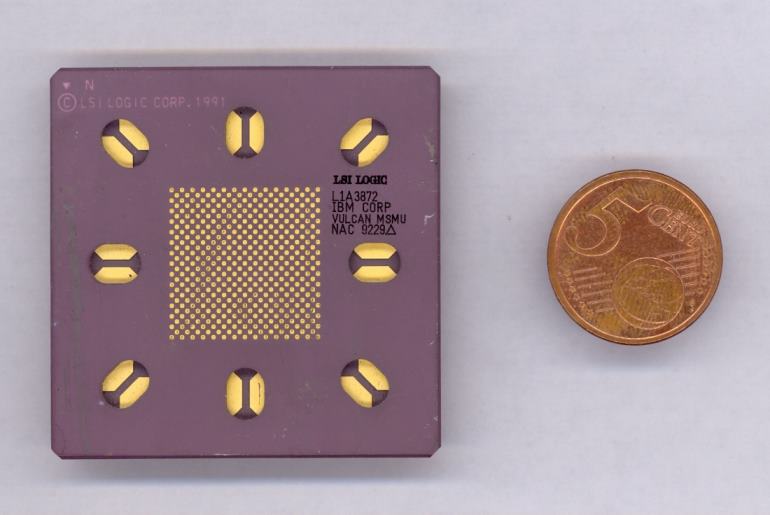

Prototipo di CPU IBM RS64 A10 "Cobra" montato in apposito socket di prova (1995). Si tratta della prima implementazione della microarchitettura PowerPC-AS, dedicata alle macchine della serie AS/400. E' una CPU RISC single-chip a 32/64 bit, funzionante a 50 MHz (ne sono state prodotte versioni successive fino ad una frequenza massima di 77 MHz), sviluppata con tecnologia semi-custom per abbreviare i tempi di progettazione e testing. Realizzata con processo CMOS 5L a 0,5 µm, 4 livelli di interconnessione in alluminio, contiene circa 5,5 milioni di transistor. Le dimensioni del chip sono di 14,5×14,5 millimetri, ed il package è di tipo CBGA (Ceramic Ball-Grid Array) a 625 contatti, con dimensioni di circa 3×3 centimetri.

Fermacarte in plexiglass contenente una serie di chip fabbricati da IBM per Cisco Systems.

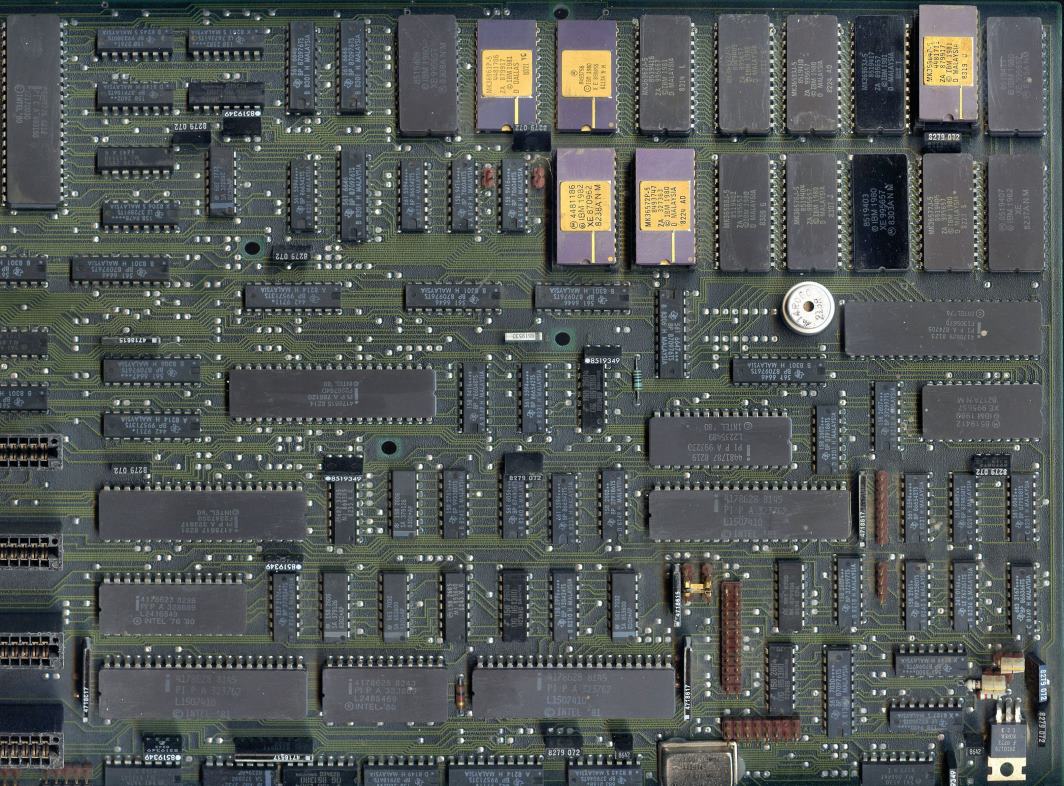

7.5.2015 - Array logici LSI FET in package PGA bianco a 40 piedini sulla scheda processore di un IBM 3740 Data Entry System (DES), circa 1976.

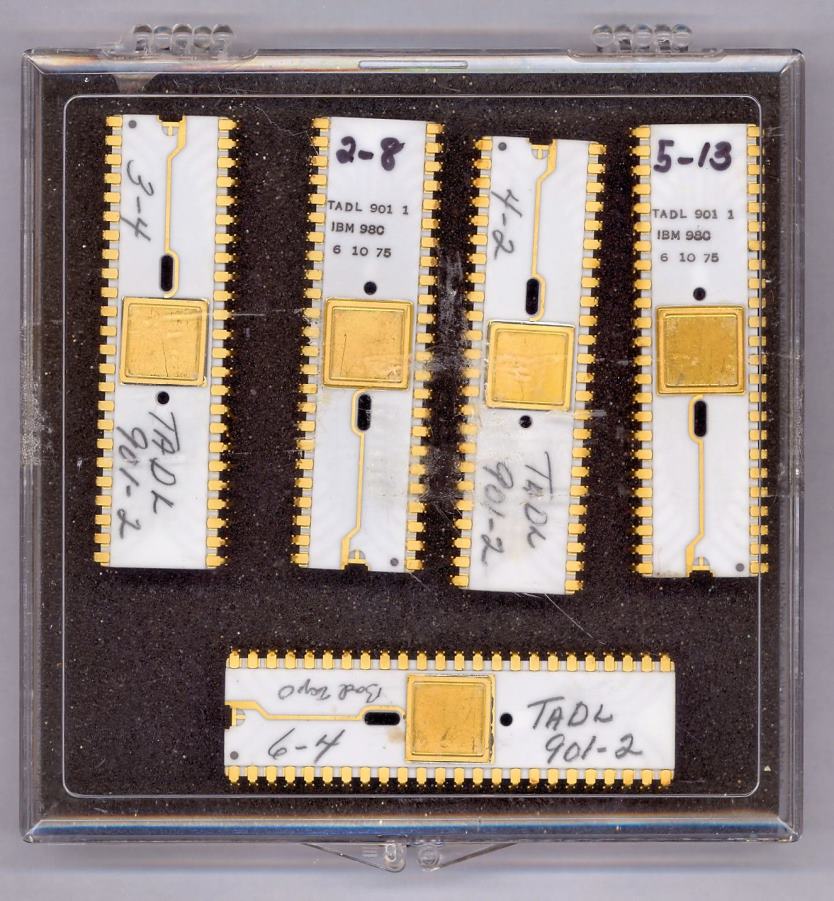

Prototipi di gate array FET IBM (1975/6).

Prototipo di integrato VLSI in package FC/BGA da 1.908 punti di contatto fabbricato da IBM per HP (fine 2005).

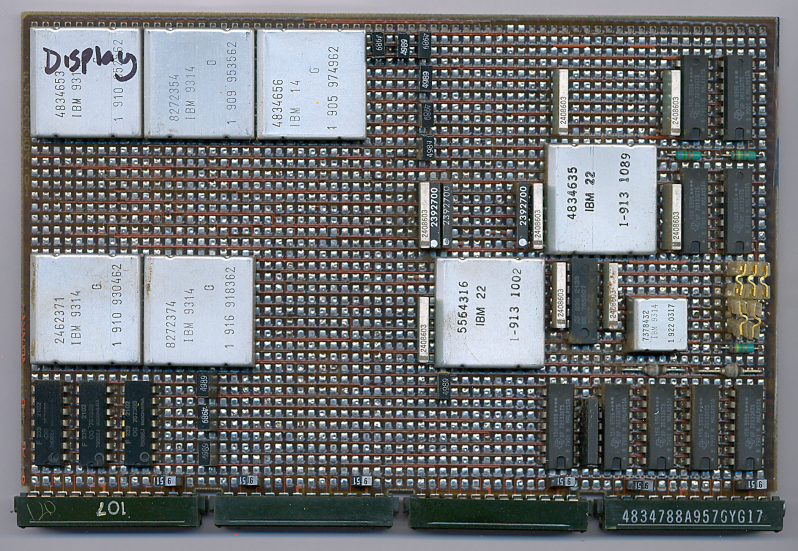

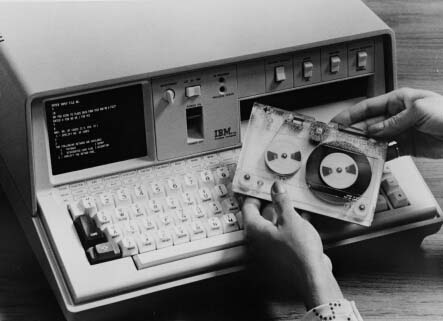

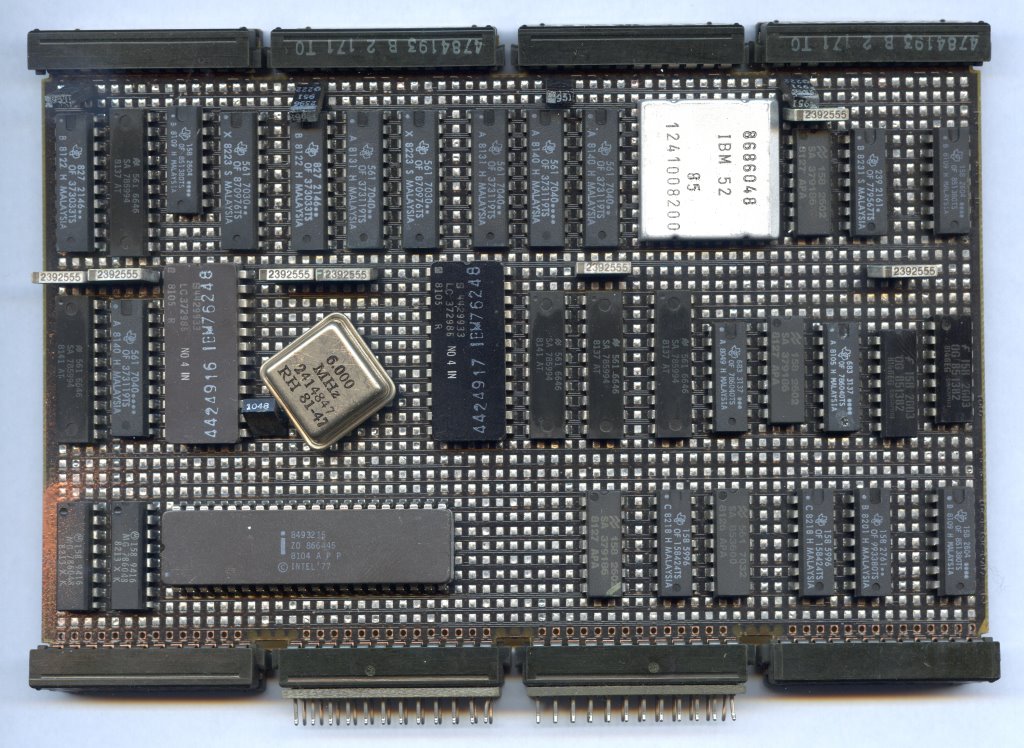

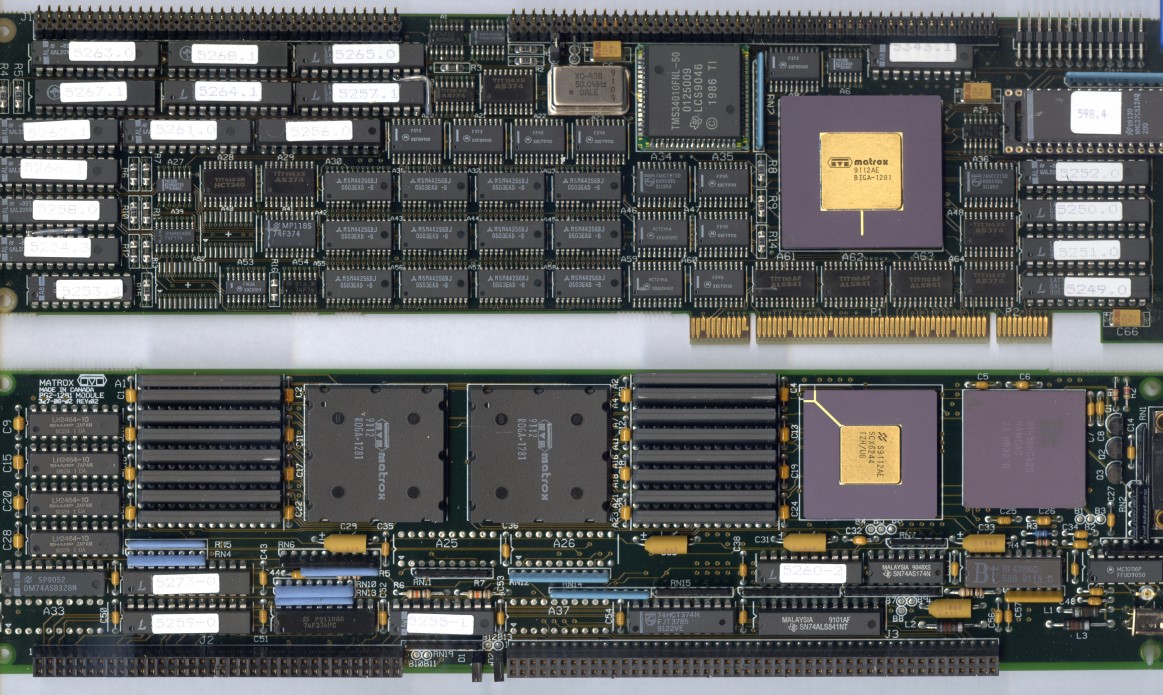

11.2.2016 - Vista parziale della scheda madre di un IBM 5322 "Datamaster" (in Italia più noto come Sistema/23). Questo esemplare è del 1982. Il 5322 è stato introdotto nel Luglio 1981 e commercializzato fino al 1985; tecnologicamente è considerato il diretto predecessore dell'IBM PC (5150), anch'esso presentato nel 1981, ad un solo mese di distanza dal Datamaster. E' storicamente importante in quanto è stato il primo personal computer IBM basato su CPU a microprocessore monolitico (un Intel 8085 a 4,77 MHz, che nella foto si trova a destra immediatamente sotto la doppia fila di ROM di sistema ed è siglato PI P A 874205) ed il primo calcolatore IBM dotato di CPU di terze parti (Intel, appunto). Il predecessore IBM 5120 era invece basato sulla CPU proprietaria IBM PALM a 1,9 MHz. L'aspetto esteriore del 5322 era quello di un desktop all-in-one con display testuale da 12 pollici a fosfori verdi (24 righe/80 caratteri), tastiera a 83 tasti e due floppy drive da 8" (a doppia faccia/doppia densità, con capacità pari a 1,2 MB) integrati; la RAM di base era ampia 64 KB incrementabili fino a 256 (grazie ad un'apposita logica di bank-switching) con l'aggiunta di apposite schede di espansione. La ROM da 112 KB conteneva invece il sistema operativo ed un interprete BASIC. Il Sistema/23 era una macchina abbastanza potente per l'epoca in cui venne introdotta; progettato per essere immediatamente pronto all'uso senza richiedere complicate operazioni di configurazione, ebbe un discreto successo di vendita anche in Europa, soprattutto grazie alla qualità ed al numero di software disponibili, principalmente gestionali ed altre applicazioni da ufficio. Si trattava di un sistema relativamente ingombrante (43 Kg compresa la stampante, anche a causa del doppio drive da 8 pollici) ma non molto costoso rispetto agli standard del tempo (9.000 Dollari il prezzo di lancio in configurazione base nel 1981). Il 5322 venne progettato e realizzato dal medesimo team che sviluppò l'IBM PC. L'IBM scelse probabilmente i floppy da 8'' anziché quelli più moderni da 5,25'', all'epoca già diffusi, probabilmente per poter impiegare anche nel 5322 gli stessi drive già in uso in molti altri suoi sistemi. Il Sistema/23 era rivolto agli uffici di medie dimensioni ed alle piccole imprese, avendo la possibilità di essere adoperato contemporaneamente da due operatori (uno in locale ed uno su terminale).

Vedi: http://www-03.ibm.com/ibm/history/exhibits/pc/pc_9.html; http://www.oldcomputers.net/ibm5322.html.

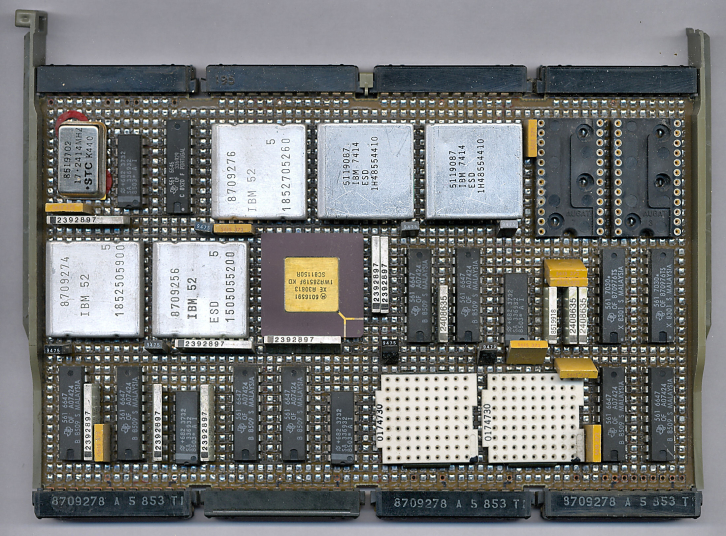

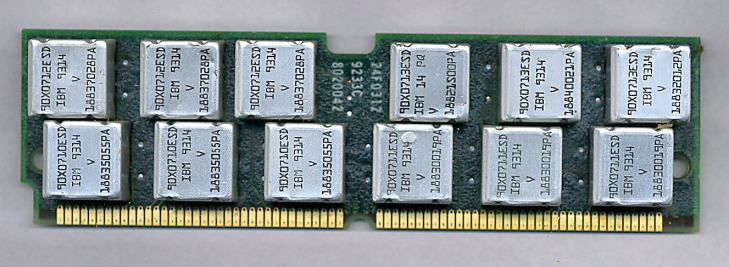

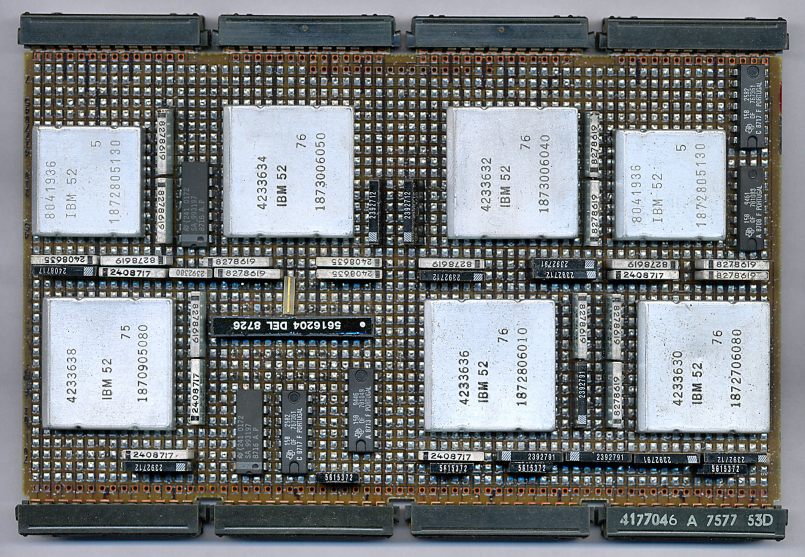

Scheda IBM (1985) con moduli di DRAM CMOS da 64 KByte (siglati IBM 7414 ESD, in alto) ciascuno dei quali contiene 4 chip da 8 KByte.

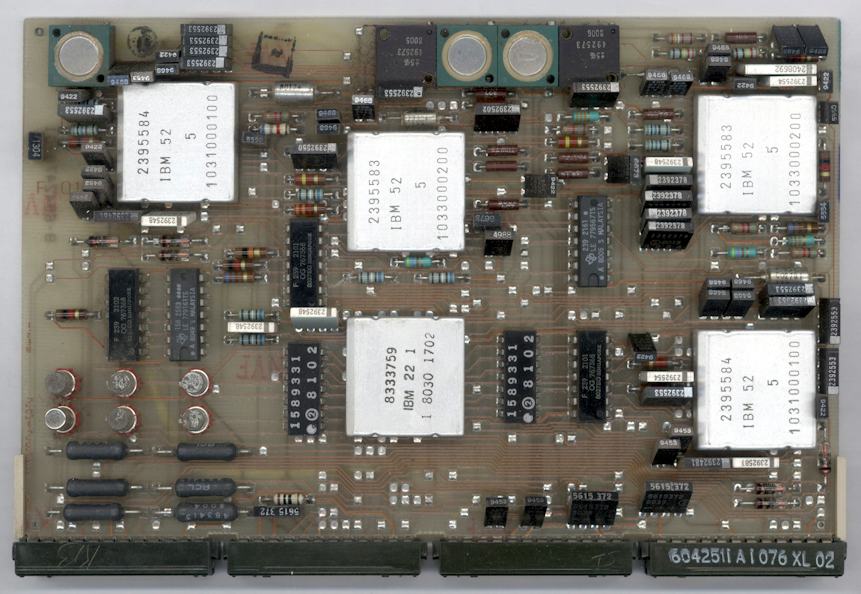

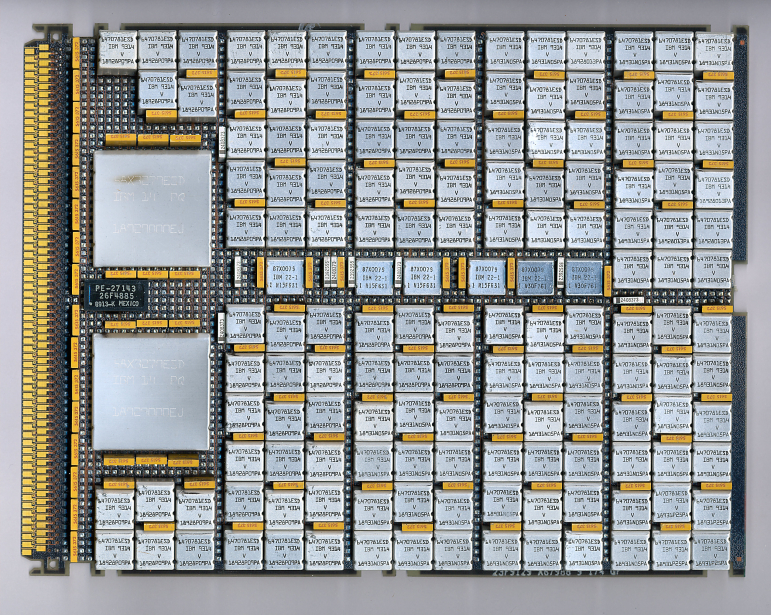

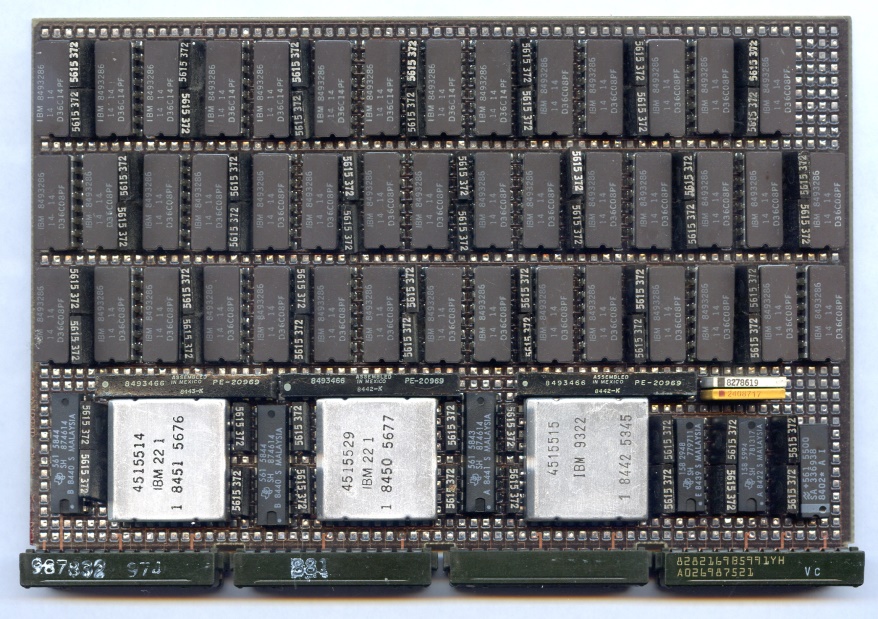

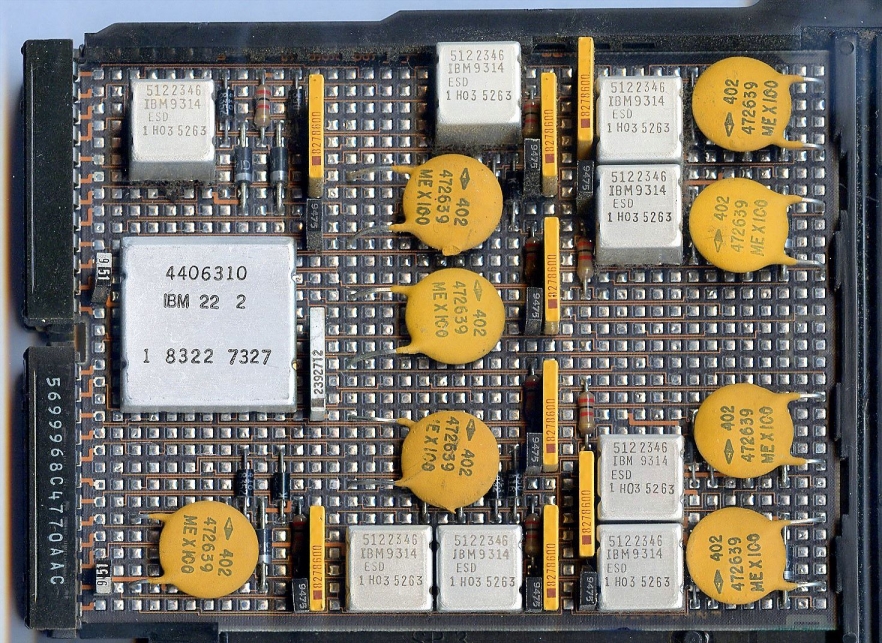

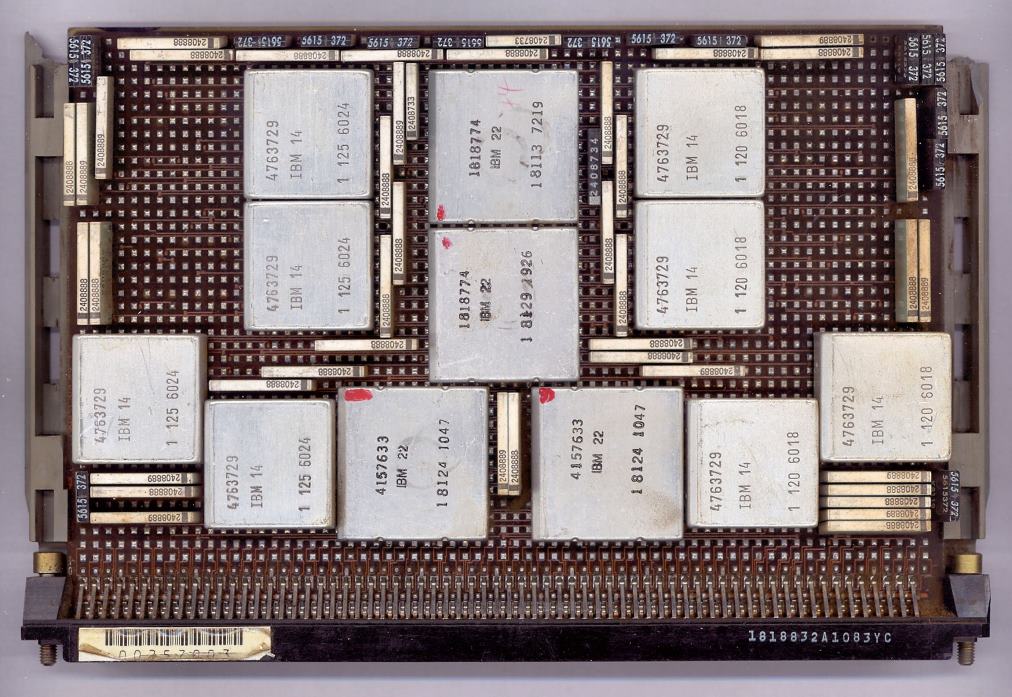

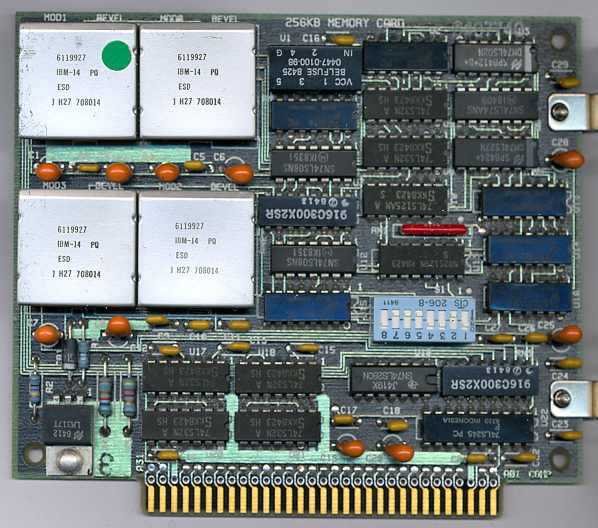

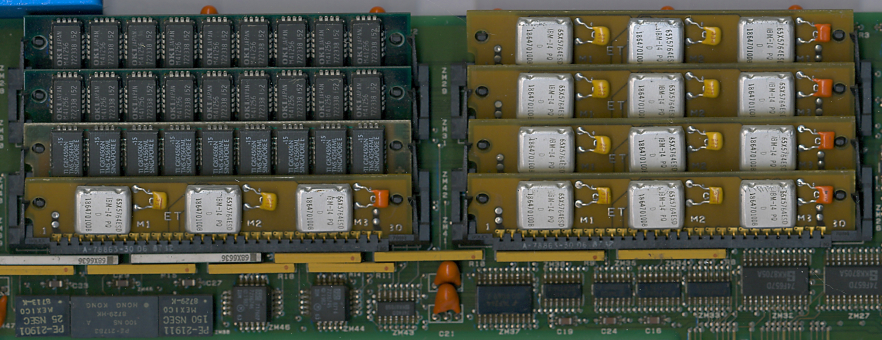

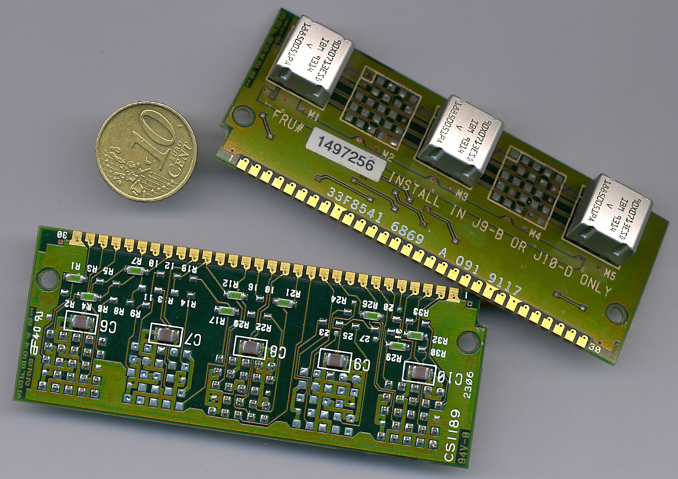

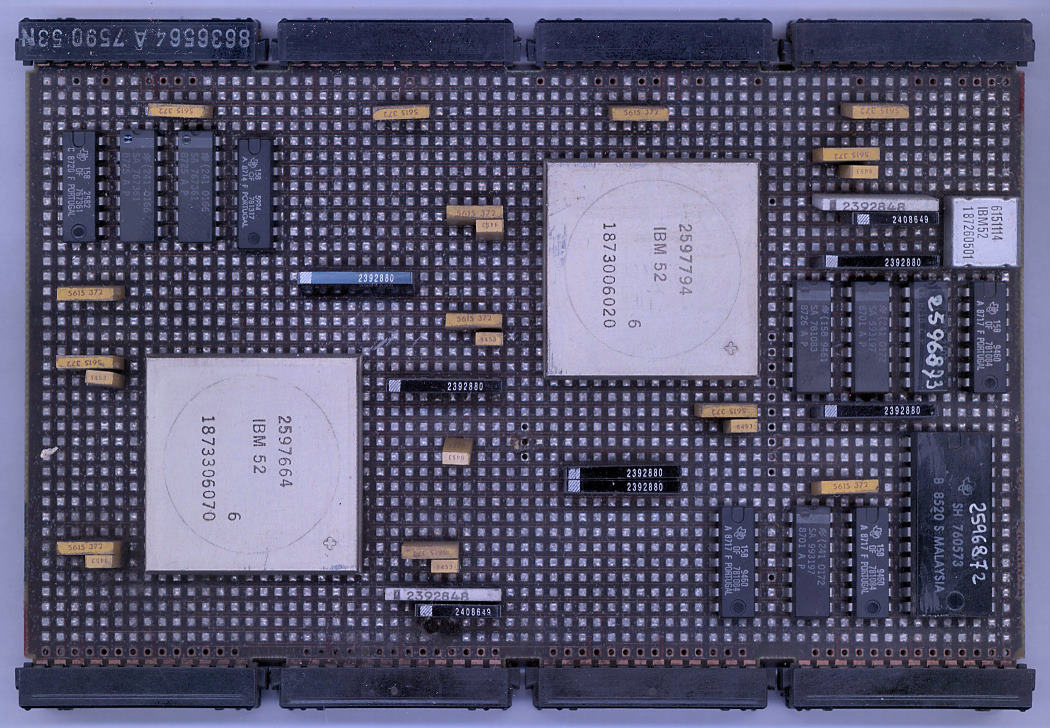

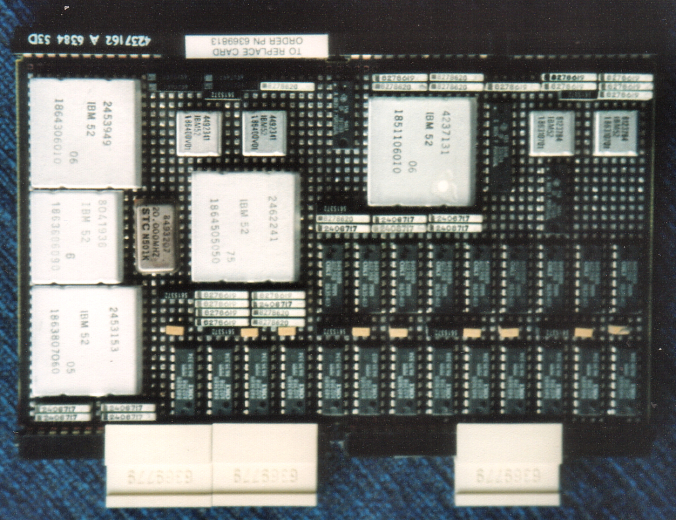

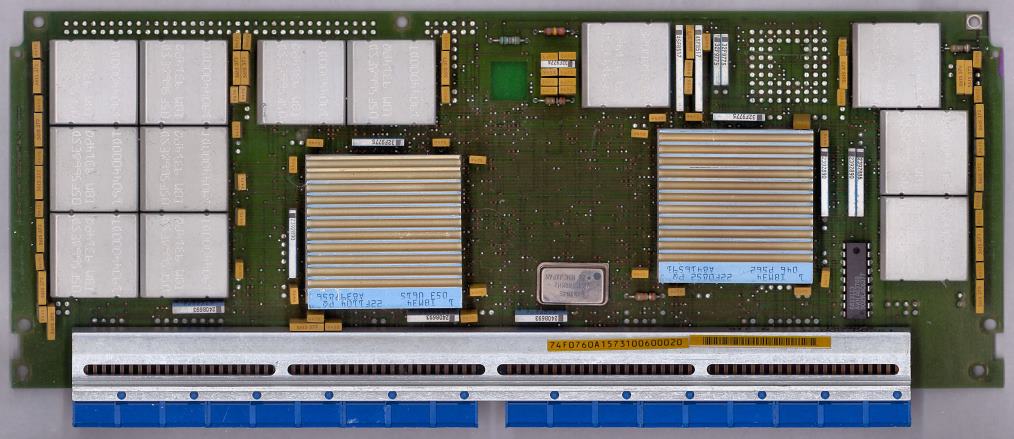

Esempio di scheda di memoria IBM (per AS/400, utilizzata anche nel Disk Cache Subsystem IBM 3990), capacità 8 MB con ECC, che utilizza chip di memoria CMOS da 1 Mbit (ciascuno dei moduli può contenere 1, 2 oppure 4 chip).

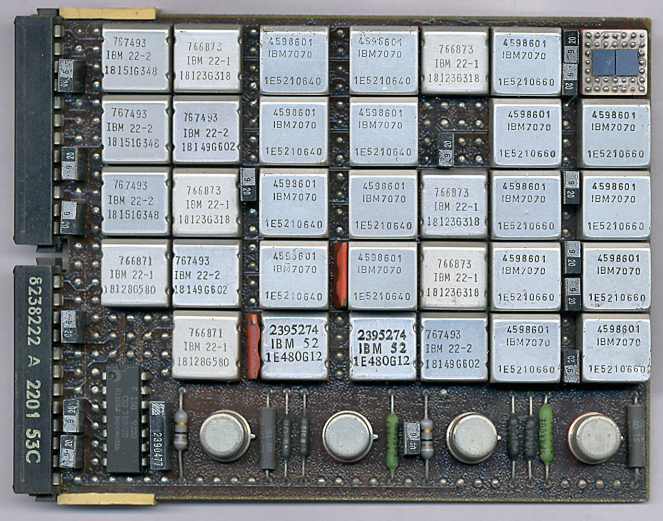

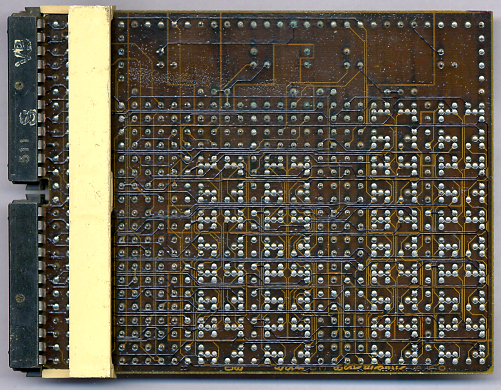

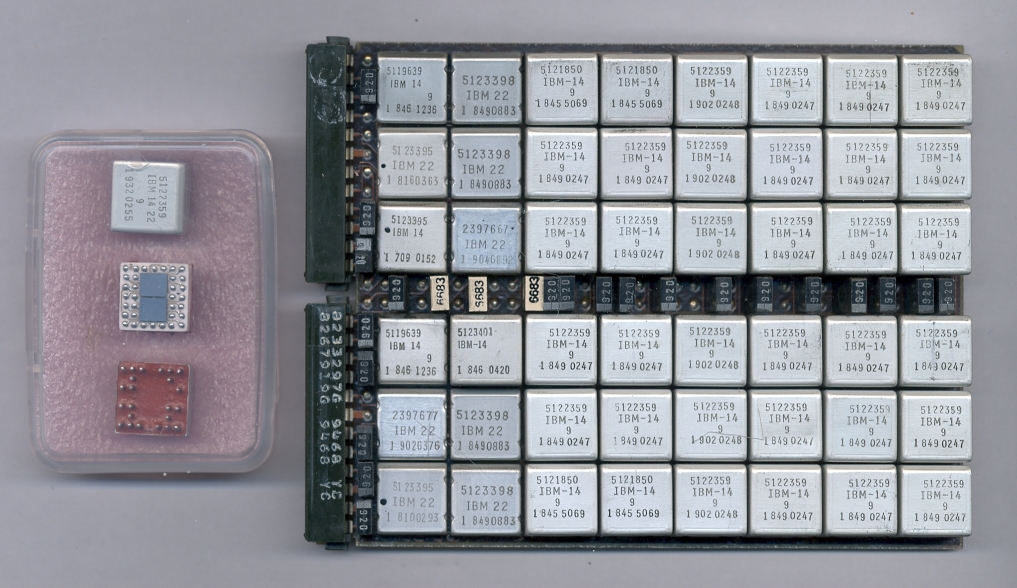

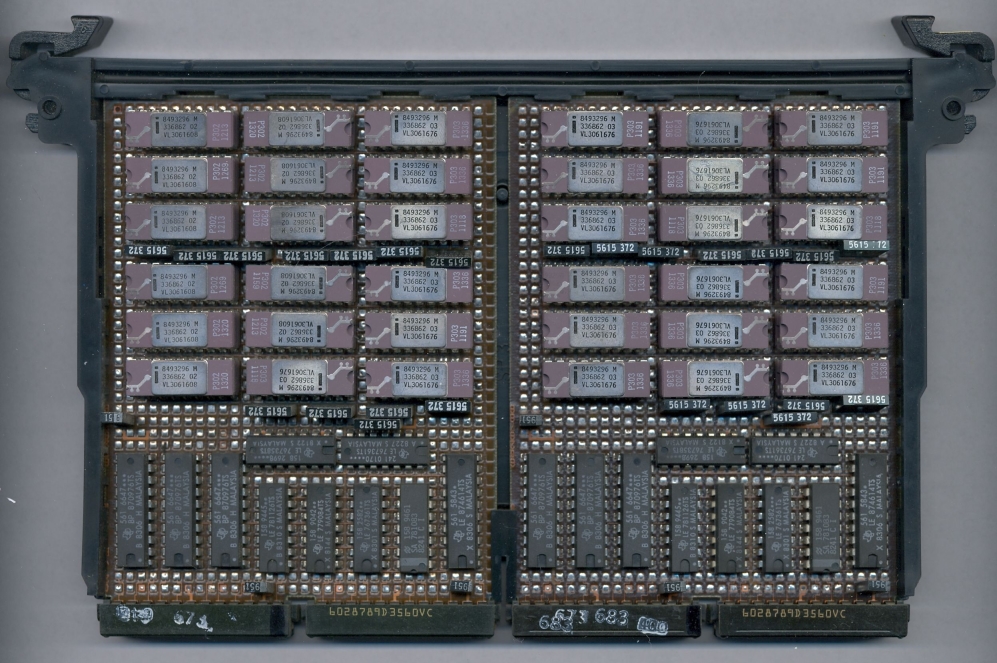

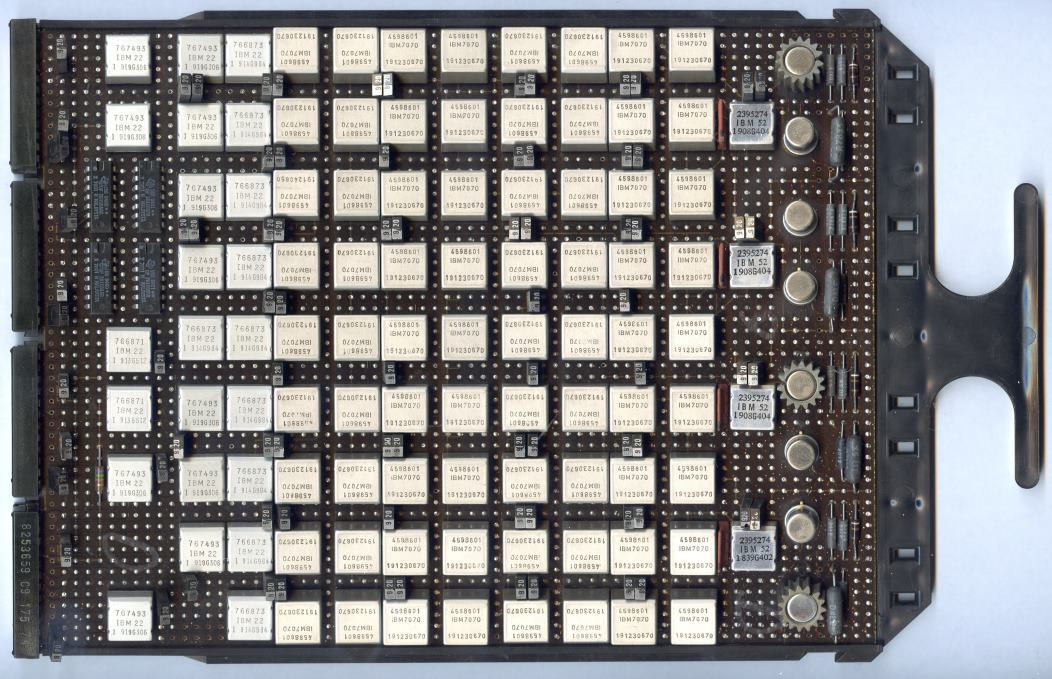

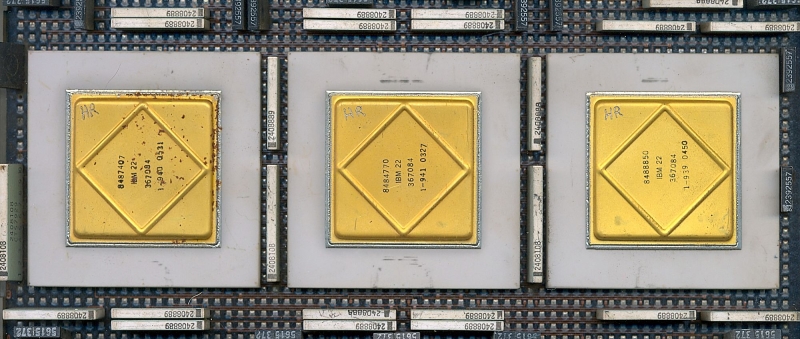

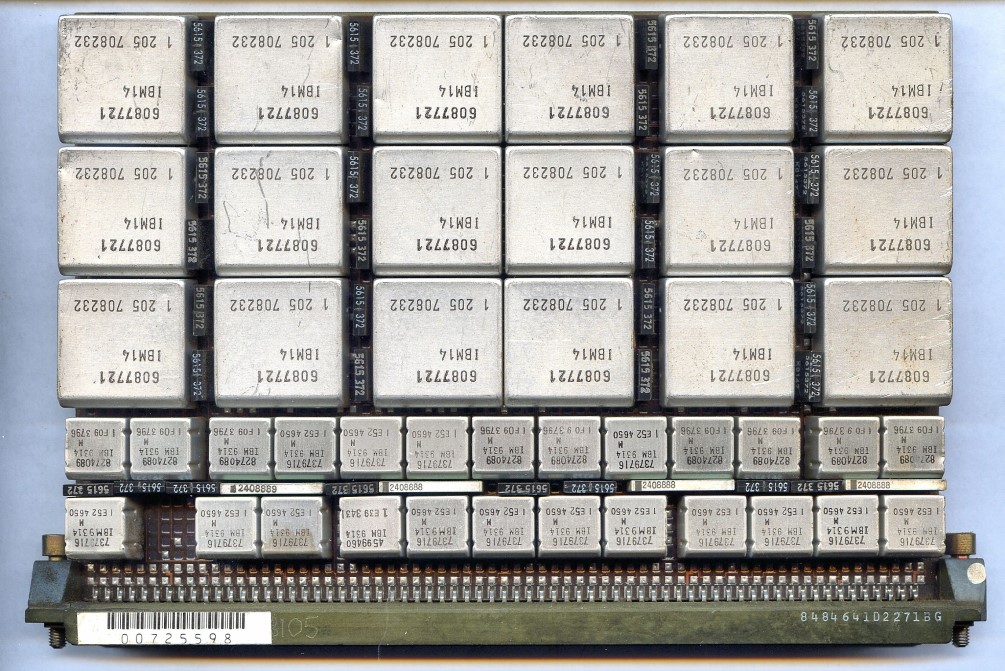

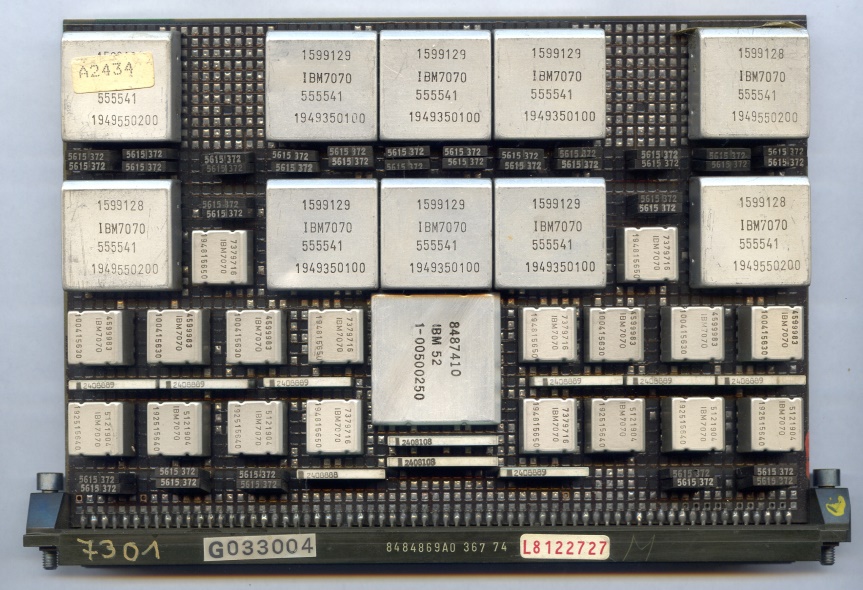

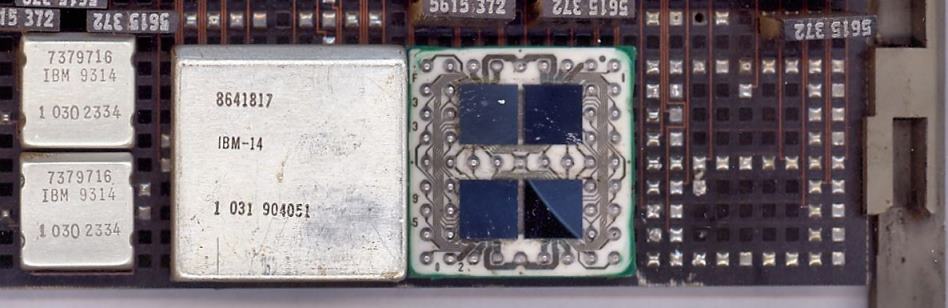

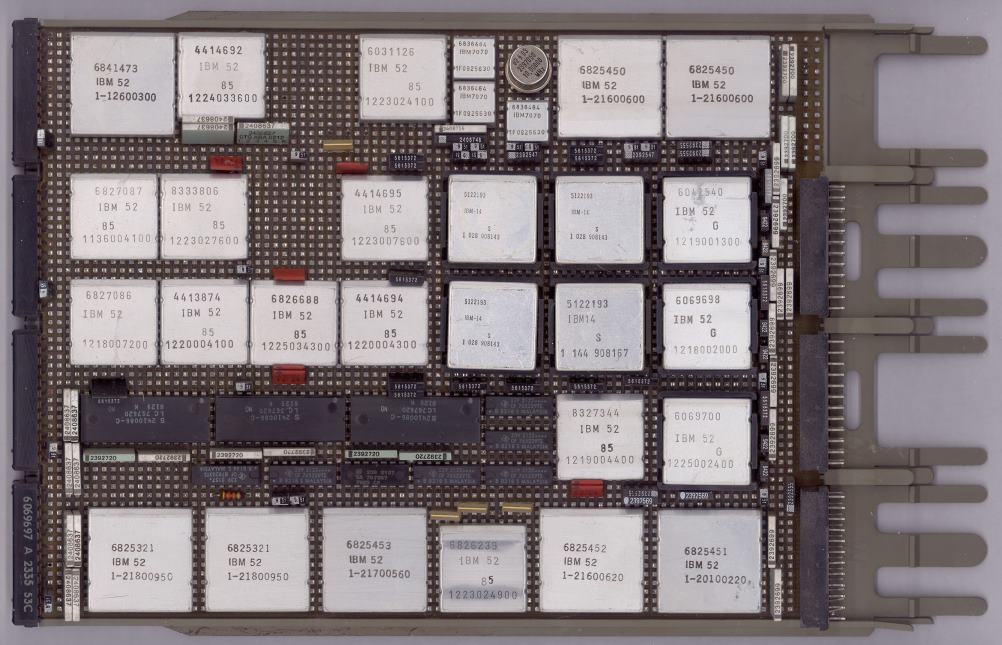

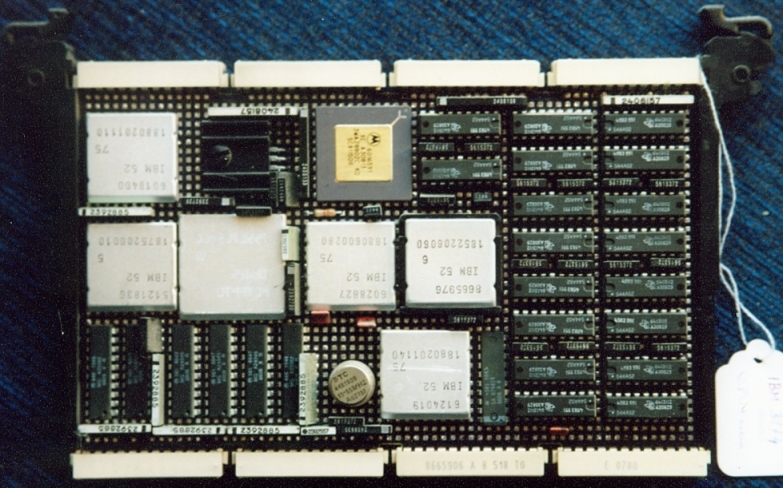

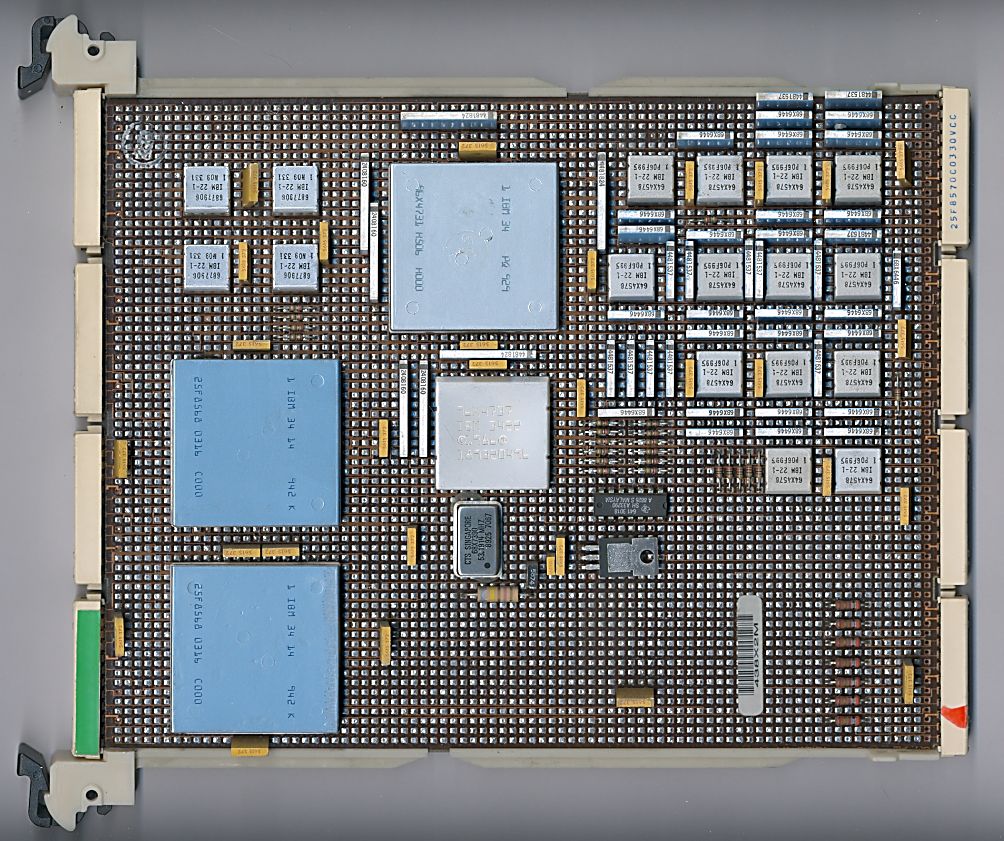

Questa memoria del 1974, a suo tempo impiegata in un minicomputer IBM System/3 Modello 12 (così mi ha assicurato chi me l'ha regalata), impiega chip DRAM da 256 bit basati su transistor FET, con celle a singolo transistor. Ne esistono anche con chip da 512 bit e da 1 kbit. I chip di memoria sono gli otto componenti a sinistra marcati "IBM 7070". Si tratta in effetti di moduli MST ciascuno dei quali può contenere due oppure quattro chip. La capacità totale della scheda è di 2 KB. Vedi http://www.corestore.org/3.htm (System/3). Questo tipo di memoria, sviluppato da IBM all'inizio degli anni Settanta, è stato impiegato in molti diversi calcolatori, dai mainframe S/370 (che già, come gli S/360 più recenti, ad es. il Modello 195, avevano fatto uso di RAM bipolari) al 5100, da molti considerato il primo personal computer IBM. Ricordiamo che la cella DRAM a singolo transistor, elemento base delle moderne memorie RAM dinamiche usate in ogni tipo di computer, venne sviluppata proprio dai ricercatori IBM del Watson Research Center. Le prime versioni impiegate ad es. nel System/370-145 contenevano 4 chip da 128 bit ciascuno, per una capacità totale di 512 bit (0,5 kbit) per modulo (vedi http://smithsonianchips.si.edu/ibm/ibm.htm).

Aggiornamento Novembre 2012

Sulla base del FRU 8238725 (in alto a destra) questa scheda è stata identificata come una memoria RAM da 2 Kword (2 KB) appartenuta ad un IBM 3741 Data Entry System. Una scheda identica è visibile nel 3741 Maintenance Library, disponibile in formato PDF nel sito Bitsavers.org. E' comunque vero che schede RAM dello stesso tipo sono state usate in alcuni modelli di calcolatori System/3.

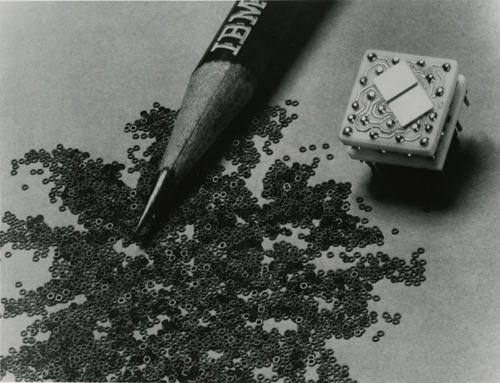

Immagine promozionale IBM (1973 circa) che evidenzia il rapporto di dimensioni tra gli anellini di ferrite utilizzati nelle memorie a nuclei magnetici dell'epoca ed un modulo MST nel quale sono alloggiati due oppure quattro chip di DRAM FET da 512 bit, del tipo di quelli visibili nella precedente fotografia.

Vedi: http://www.ieee.org/portal/cms_docs_sscs/sscs/08Winter/dennard_hi_res01484036.pdf (Evolution of the MOSFET Dynamic RAM - A personal View).

Anche: http://portal.acm.org/citation.cfm?id=1664871 (Solid-state Memory Development in IBM, IBM JRD vol. 25 issue 5, 1981).

Anche questo link (richiede registrazione), MOSFET memory circuits (Proceedings of the IEEE, vol. 59 issue 7, 1971).

Pagina dedicata a Robert Dennard, l'inventore della DRAM MOSFET: http://www.fi.edu/winners/2007/dennard_robert.faw?winner_id=4407.

Anche: http://www.cs.huji.ac.il/course/2003/postPC/docs/Critchlow1999.pdf (MOSFET Scaling - The Driver of VLSI Technology)

Anche: http://icknowledge.com/history/1970s.html.

Delle prime memorie IBM a circuito integrato si parla anche in Main Monolythic Memory, di J. K. Ayling e R. D. Moore, pubblicato in Semiconductor Memories, IEEE Press 1972, pag. 219 e segg.

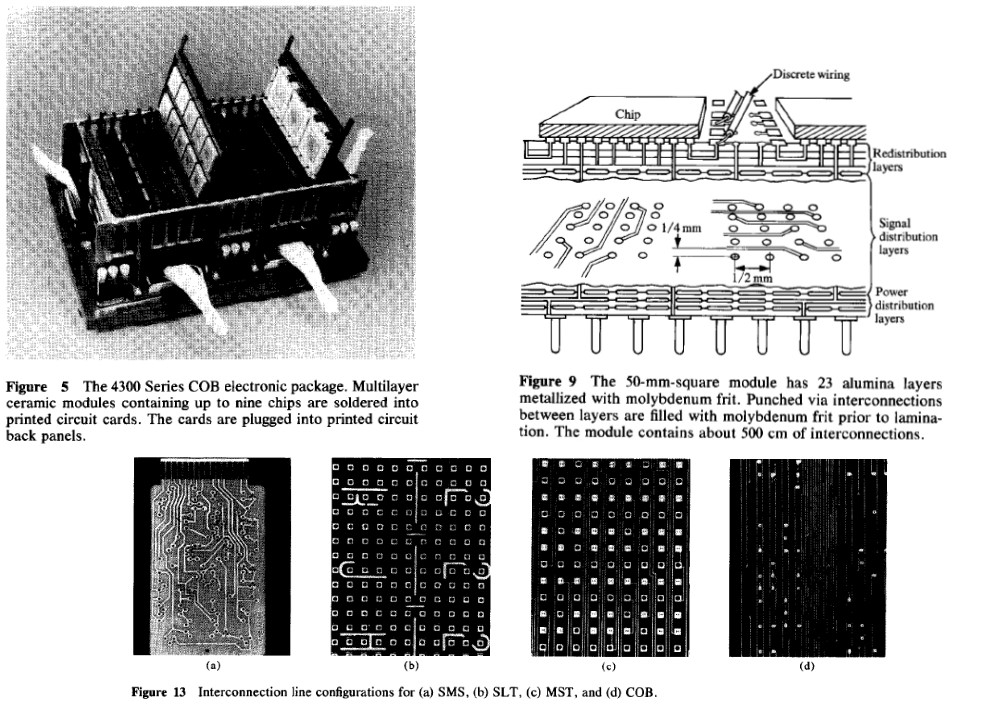

Sviluppo dei circuiti integrati monolitici IBM

Il primo integrato monolitico venne fabbricato da IBM nel 1966: si trattava di una semplice memoria RAM bipolare a 16 bit, chiamata SP-95 (A 16-bit Monolithic Memory Array Chip, Journal of Applied Physics, 37-1966). La sua struttura regolare ed ordinata poteva essere realizzata con le medesime maschere per litografia e gli stessi processi di diffusione già impiegati nella produzione dei circuiti ibridi SLT. Con questo primo circuito, IBM sperimentò già due elementi chiave poi ripresi nelle successive generazioni di integrati logici: l'incapsulamento con ossido di silicio vetrificato e la connessione del chip col metodo C4 (Controlled-Collapse Chip Connection), evoluzione della tecnica flip-chip impiegata nei moduli SLT ed A-SLT. Questo particolare procedimento, che per l'allineamento col substrato sfruttava le forze di tensione superficiale durante la saldatura, è rimasto in uso fino alla metà degli anni Ottanta ed è stato progressivamente perfezionato fino a consentire la connessione di circa 300 terminali per chip (Design of Monolithic Circuit Chips, IBM Journal of Research and Development, 10-1966). Alla fine degli Sessanta quattro impianti IBM, di cui uno in Germania, si occupavano della produzione di circuiti integrati: ciascuno di essi era inoltre specializzato nella ricerca e sviluppo di un particolare aspetto del processo di fabbricazione (diffusione, metallurgia, litografia ecc.) Il lavoro di ricerca portò rapidamente allo sviluppo di tecnologie avanzate per la manipolazione automatica dei wafer, per la loro lappatura di precisione, per l'applicazione del photoresist e così via. Tra il 1967 ed il 1968 vennero completati il progetto e quindi la realizzazione di tutta una classe di nuovi integrati logici, chiamata MST (Monolithic System Technology), impiegata nei calcolatori System/370 ed in molti altri prodotti IBM, caratterizzata da una velocità di commutazione di 6-10 ns. All'inizio degli anni Settanta, dopo il successo del primo chip di memoria da 64 bit, vennero sviluppati i primi moduli multichip, che in unione ai chip di memoria bipolari da 128 bit (A High-Performance Monolithic Store, ISSCC Digest of Technical Papers, 36-1969; Bipolar LSI for Main Memory, ISSCC Digest of T. P., 78-1971) permisero di ottenere i moduli da 0,5 kbit (512 bit) impiegati per la prima volta nel System/370-148. Sempre all'inizio degli anni Settanta cominciarono ad imporsi all'attenzione gli integrati logici basati su transistor ad effetto di campo (FET), noti come IGFET (Insulated-Gate FET). Essi, pur avendo caratteristiche di velocità inferiori rispetto a quelle dei circuiti bipolari, risultavano più semplici da produrre e nello stesso tempo consentivano maggiori densità di integrazione. Un aspetto chiave nella fabbricazione di integrati FET (e MOS) è la pulizia dell'intero processo produttivo, che deve essere molto maggiore di quella richiesta dai circuiti bipolari. IBM si trovò quindi nella necessità di sviluppare nuove linee di produzione ad hoc, parallele a quelle già in funzione. Il progetto della prima famiglia di integrati FET prese il nome di Emerald. Si trattava, contrariamente ad MST, di un gruppo di circuiti logici semi-custom a media scala di integrazione, realizzati facendo uso (per la prima volta) di specifici software di progettazione logica. I circuiti Emerald, introdotti nel 1971 con una capacità media di 300 gate logici per chip, venivano di volta in volta personalizzati secondo le specifiche esigenze di progetto della macchina alla quale erano destinati (Gate Array Experiences in IBM, Paper No. 22-3, Electro-80 Conference Record; A 1500-gate Random Logic LSI Masterslice, ISSCC Digest of T. P., 60-1979). Nello stesso periodo IBM introdusse una ROM FET da 18 kbit, che fu il banco di prova per la tecnologia che venne poi impiegata nella fabbricazione delle prime RAM FET da 1 e 2 kbit (sviluppate in Germania, a Boeblingen). Sempre nel 1971 IBM sviluppò un nuovo tipo di substrato da impiegare con i chip logici LSI, ottenuto con un processo chiamato Metallized Ceramic (MC) e che consentiva un massimo di 100 piedini (pin) per modulo. Alla metà degli anni Settanta IBM iniziò la progettazione di integrati logici a larga scala di integrazione, sia bipolari che MOS. I primi, con una capacità di 704 porte NAND e 80 driver, vennero usati nei calcolatori 3081 e derivati; i secondi, fabbricati con l'innovativa tecnologia SAMOS (Silicon and Aluminium MOS) diedero vita, a partire dal 1981, ad una famiglia di memorie DRAM MOS ad alta capacità (da 18 a 64 kbit per chip: Solid-State Memory Development in IBM, IBM Journal of Research and Development, 25-1981) e basso costo, che vennero impiegate in moltissimi prodotti IBM degli anni Ottanta.

Evoluzione delle memorie IBM a circuito integrato monolitico

Quando alla metà degli anni Sessanta vennero progettate le prime RAM a circuito integrato monolitico, la tecnologia di gran lunga dominante nel campo delle memorie per calcolatori elettronici era quella dei nuclei magnetici, introdotta all'inizio degli anni Cinquanta. Appariva evidente come le memorie a circuito integrato presentassero un innegabile vantaggio e cioè la molto maggiore densità, sia per quanto riguarda la memoria vera e propria sia per la possibilità di integrare nello stesso chip che contiene la memoria stessa anche i driver e le interfacce. Per anni tuttavia le memorie basate su circuiti integrati dovettero fare i conti con un elevato costo per bit e con un'affidabilità non ancora al livello delle concorrenti a nuclei. Le ricerche svolte da IBM si rivolsero dunque innanzitutto alla riduzione del costo medio per bit, che venne perseguita progettando celle di memoria il più possibile compatte (onde minimizzare l'area di silicio occupata). Il processo di fabbricazione bipolare impiegato da IBM si dimostrò poi, alla prova dei fatti, più affidabile di quanto ci si attendeva. La prima applicazione commerciale di una memoria a circuito integrato in un prodotto IBM si ebbe nei calcolatori System/360-91 e -95, in particolare nella piccola e veloce memoria SPM (Storage Protected Memory). La versione a nuclei della SPM era organizzata in 64 parole (word) da 20 bit, con un tempo di ciclo di 350 ns; la controparte a circuiti integrati aveva una capacità di 128 word a 16 bit ed un tempo di ciclo di 300 ns. Il progetto di questa memoria iniziò nell'autunno del 1965; il chip di memoria, basato su celle a 5 transistor, venne concepito da Farber e Schlig e reso pubblico nel 1966. L'impiego delle celle a 5 transistor, relativamente grandi, fu deciso sulla base della loro velocità elevata e della lettura non distruttiva (NDRO), entrambi elementi chiave in una memoria SPM. La prima memoria IBM a circuito integrato, nota come SP-95 o Phase I, usava 16 celle di questo tipo, organizzate in matrice 4 per 4, senza l'aggiunta di circuiti di decodifica né di comando (driver). La capacità totale della SPM poteva arrivare fino a 1024 word da 9 bit. Presentata nel Gennaio 1966, questa memoria fu il primo esempio di RAM a circuito integrato monolitico impiegata in un calcolatore elettronico commerciale. Il secondo impiego di una memoria a integrati bipolari monolitici in un sistema IBM fu la cache del System/360-85, ampia 16 KB con un ciclo di soli 80 ns. Per ottenere questa notevole prestazione IBM sviluppò l'evoluzione della sua prima memoria monolitica, e la chiamò Phase 2. Introdotta nel Settembre 1967 e presentata ufficialmente nel 1969, si basava su chip bipolari con una capacità di 64 bit ed una dimensione di soli 2,85 mm di lato. Essi contenevano anche la logica di decodifica, ed assorbivano circa 112 mW ciascuno. Il tempo medio di lettura era di 7 ns, contro i 12 ns mediamente richiesti dalla scrittura. Tali chip erano fabbricati con processo bipolare a 5 micrometri, con singolo livello di metallizzazione (interconnessione) in Alluminio. Venivano montati a coppie in moduli da 1,27 cm di lato, dotati di 23 piedini. Ciascun chip integrava 664 componenti. Nel 1969 venne quindi sviluppato un chip di memoria, con organizzazione 32 per 3 bit, che impiegava un nuovo tipo di cella progettato da Harper e noto come Cross-Coupled Double Emitter (CCDE - Non Destructive Read Transistor Memory Cell, US Pat. 3.423.737, 6/65). Fu questo il primo chip di memoria di tipo "fully-decoded"; trovò applicazione, fra l'altro, nei calcolatori System/370-158 e -168. La RAM 32 x 3 venne in seguito riprogettata con la nuova tecnologia a 2 micrometri ed isolamento in ossido (1976) e con alcune modifiche circuitali per migliorarne la velocità. Il chip risultante fu impiegato nei calcolatori della famiglia 3030. Ulteriori migliorie vennero presentate nel 1971 all'ISSCC (Wiedmann e Berger: High-Density Static Bipolar Memory, ISSCC Digest of T. P., XVI-1973); esse portarono allo sviluppo di un chip con organizzazione 512 x 10 (con 1 bit di ridondanza) e tempi di accesso compresi tra 30 e 40 ns. Tale chip venne estesamente utilizzato nei calcolatori della famiglia 4300 in appositi moduli multichip.

Nel Gennaio 1968 IBM prese la decisione di sospendere lo sviluppo delle memorie a nuclei magnetici per concentrarsi unicamente su quelle a circuito integrato, da impiegare non solo come cache o nei buffer, bensì anche come RAM principale. Questa decisione condusse allo sviluppo dei chip di memoria bipolari da 128 bit noti come "Phase 2I", che furono i primi integrati effettivamente competitivi con le memorie a nuclei in termini di costo per bit e di affidabilità. Impiegavano le celle di Harper descritte sopra ed avevano una semplice organizzazione 128 x 1. Introdotti nell'Agosto 1969 (Gates, Kinney, North, Bipolar LSI for a Main Memory, ISSCC Digest of T. P., XIV-1971), venivano montati in doppia coppia in appositi moduli a due livelli, ottenendo una capacità di 512 bit per modulo. A loro volta i moduli erano collocati in schede con una capacità di 48 kbit (49.152 word da 9 bit), annunciate nel Settembre 1970 ed impiegate per la prima volta nel System/370-145 (Marzo 1971). Nel 1970 incominciò anche il progetto dei chip da 256 bit, che vennero poi messi in produzione l'anno successivo ed utilizzati in moduli da due integrati ciascuno. La prima memoria IBM da 1 kbit venne completata nel Marzo 1972 ed applicata in un sistema commerciale nel Giugno di quello stesso anno. La dimensione del chip era di 3 per 3,8 mm, con un tempo di accesso medio di 90 ns a livello di scheda di memoria; allorché veniva usata come memoria buffer (o cache), i tempi scendevano a 13 ns per l'accesso ed a 45 ns di ciclo. Anche questo chip di memoria veniva montato in moduli da 4 integrati, disposti in doppia coppia su due livelli. Tali chip furono inizialmente impiegati nei System/370-138 e -148 e successivamente nella cache del -168 e del 3033. Alla metà degli anni Settanta la tecnologia delle memorie si spostò con decisione verso gli integrati MOSFET, dal momento che quelli bipolari, pur veloci, soffrivano di alcune importanti limitazioni in fatto di densità e di costo medio per bit. IBM aveva iniziato molto presto la ricerca nel settore MOSFET, tanto da poter iniziare la produzione di memorie da 1 kbit e buona velocità (50 ns) nel 1971. Queste memorie furono impiegate nel System/370-158. A differenza della prima RAM MOS commerciale, l'Intel 1103 (1970), le memorie IBM erano di tipo NMOS (MOS a canale N). Le prime DRAM IBM da 64 kbit vennero fabbricate nel 1976 e messe in produzione di massa l'anno successivo. Il loro primo impiego fu la memoria principale del calcolatore 4341 (1979). IBM decise di orientarsi sulla tecnologia NMOS piuttosto che sulla concorrente PMOS all'inizio degli anni Sessanta, precisamente nel 1963. Il motivo di questa scelta era la possibilità dei circuiti NMOS di operare a frequenze superiori rispetto alle controparti PMOS. Tuttavia, la fabbricazione di integrati NMOS affidabili, sia logici che di memoria, comportava diverse difficoltà di produzione che vennero di volta in volta superate con l'adozione di processi poi divenuti standard nell'industria dei semiconduttori. I primi passi di IBM nel settore dell'integrazione a larga scala (LSI) NMOS furono tutti tesi alla progettazione di circuiti logici. A partire dal 1966 IBM si concentrò anche sulle memorie, sia statiche che dinamiche. Furono sviluppati alcuni chip di prova da 48 bit (1966), da 128 bit (1967) e da 512 bit (1968). Parallelamente IBM studiò ed introdusse alcune innovazioni-chiave nella tecnologia delle DRAM: in particolare, la cella a quattro transistor (1970), quella a tre transistor ed infine la cella ad un solo transistor. Quest'ultima, concepita da R. Dennard nel 1968, impiega un transistor MOSFET come switch ed un condensatore MOS come elemento di memoria ed è divenuta rapidamente lo standard nelle DRAM ad alta capacità. I primi esempi di memorie MOSFET IBM pronte per l'impiego in sistemi commerciali risalgono al 1968; il loro sviluppo richiese la soluzione di alcuni importanti problemi relativi alla saldatura, all'isolamento ed alle tensioni di lavoro. Le prime memorie MOSFET commerciali di IBM furono i chip da 1 kbit (1971) e da 2 kbit (A High-Performance Low Power 2048-bit Memory Chip in MOSFET Technology and its Applications, IEEE J. Solid-State Circuits SC-11). Questi ultimi, in particolare, vennero usati a estesamente a partire dal 1975 nelle macchine della serie 3030, laddove erano montate in appositi moduli da 4 chip per un totale di 8 kbit, con un tempo di accesso medio di 50 ns ed una capacità di 32 KB per scheda. Gli integrati DRAM da 64 kbit, presentati nel 1975 e basati sulla tecnologia SAMOS (Silicon and Aluminium MOS) a 45 nm, anch'essi montati in moduli da 4 od 8 chip, furono invece introdotti nel 1979 e trovarono impiego nei sistemi 4331/4341 e nel System/38.

Vedi Pugh et al., Solid State Memory Development in IBM, IBM Journal of Research and Development, vol. 25 - 1981, pag. 585.

Aggiornamento Luglio 2012 - Breve storia dell'evoluzione dell'industria delle DRAM

La storia delle memorie DRAM, in termini di tecnologia e di strategie commerciali, è strettamente legata a quella più generale dell'industria dei semiconduttori, il cui sviluppo e le cui dinamiche competitive hanno un significativo e diretto effetto sull'evoluzione delle memorie. Iniziando dall'introduzione della prima DRAM a circuito integrato si possono riconoscere tre distinti periodi, corrispondenti alle diverse regioni geografiche che hanno dominato il mercato delle memorie: Stati Uniti, Giappone, Corea. Nel 1975 i produttori americani (Intel in primis, col 46%, seguita da Texas Instruments col 25% e da Mostek col 14%) si dividevano oltre il 90% del mercato globale delle DRAM; nel 1990, più nessuno di essi aveva una quota superiore all'8% (ed i 5 principali erano stati nel frattempo sostituiti da altrettante compagnie giapponesi e coreane: Toshiba, Samsung, NEC, Mitsubishi, Hitachi); nel 1992 infine, cominciò l'epoca di predominio dei fabbricanti coreani (Samsung e altri) che si afferarono definitivamente entro l'inizio del 2000. Fino dall'invenzione del transistor nel 1947 ad opera di ricercatori dei Bell Labs (Laboratori Bell), i notevolissimi finanziamenti governativi - soprattutto nel settore aerospaziale e della difesa - avevano sostenuto in modo rilevante lo sviluppo dell'industria statunitense dei semiconduttori, al punto che è possibile oggi affermare che senza tali sussidi essa non sarebbe potuta crescere così rapidamente come è avvenuto nel corso del ventennio 1950-1970. La realizzazione delle prime DRAM a circuito integrato da parte di Intel (che si è affermata con la famosa 1103) ed altri pionieristici produttori oggi scomparsi o dimenticati (Fairchild, Advanced Memory Systems, AMI) è anch'essa figlia, sebbene indirettamente, di questi investimenti pubblici e del supporto dato da essi all'industria USA. I produttori statunitensi potevano quindi contare su una profonda relazione in termini di recerca e sviluppo col Governo da una parte e con l'industria della difesa dall'altra, che rappresentava per loro un notevole vantaggio competitivo sui loro concorrenti. Alcune specifiche caratteristiche dell'industria delle memorie (elevati investimenti iniziaoli richiesti, breve ciclo di vita dei prodotti, necessità di continua innovazione) la rendono particolarmente sensibile alla dimensione ed alla pronta disponibilità dei capitali, siano essi pubblici oppure privati, in essa impiegati.

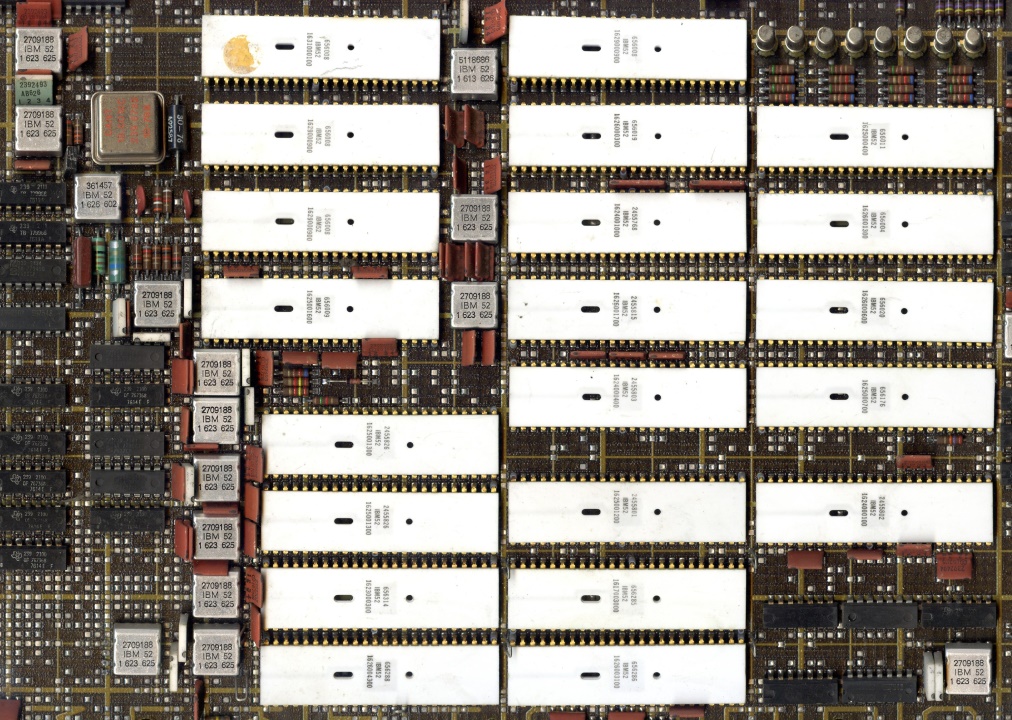

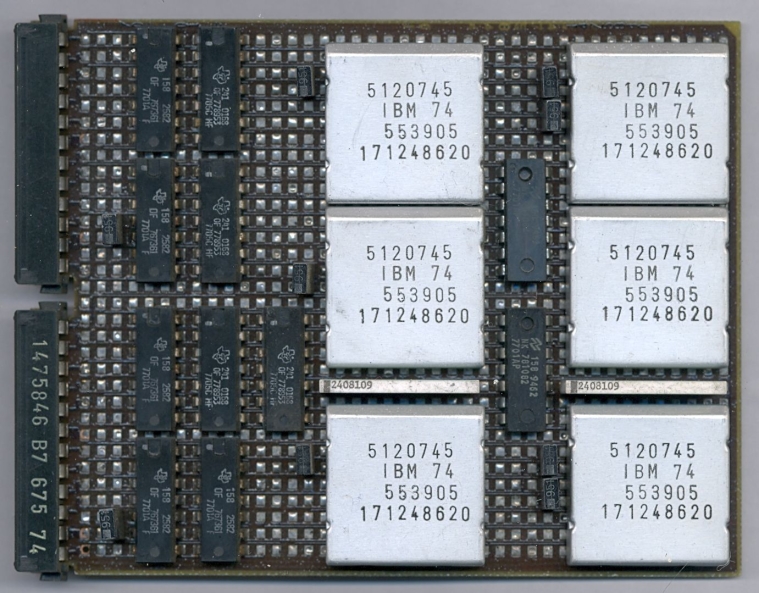

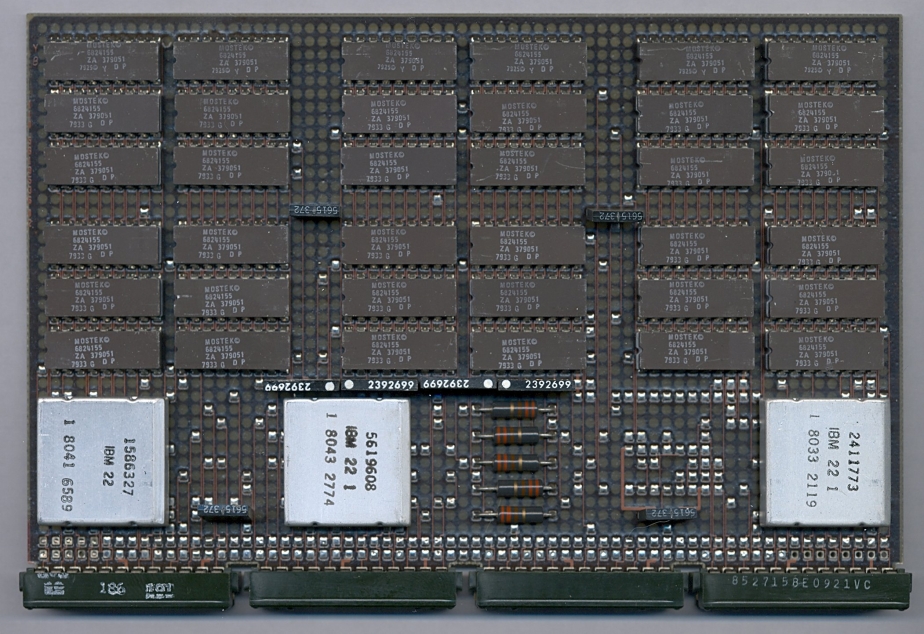

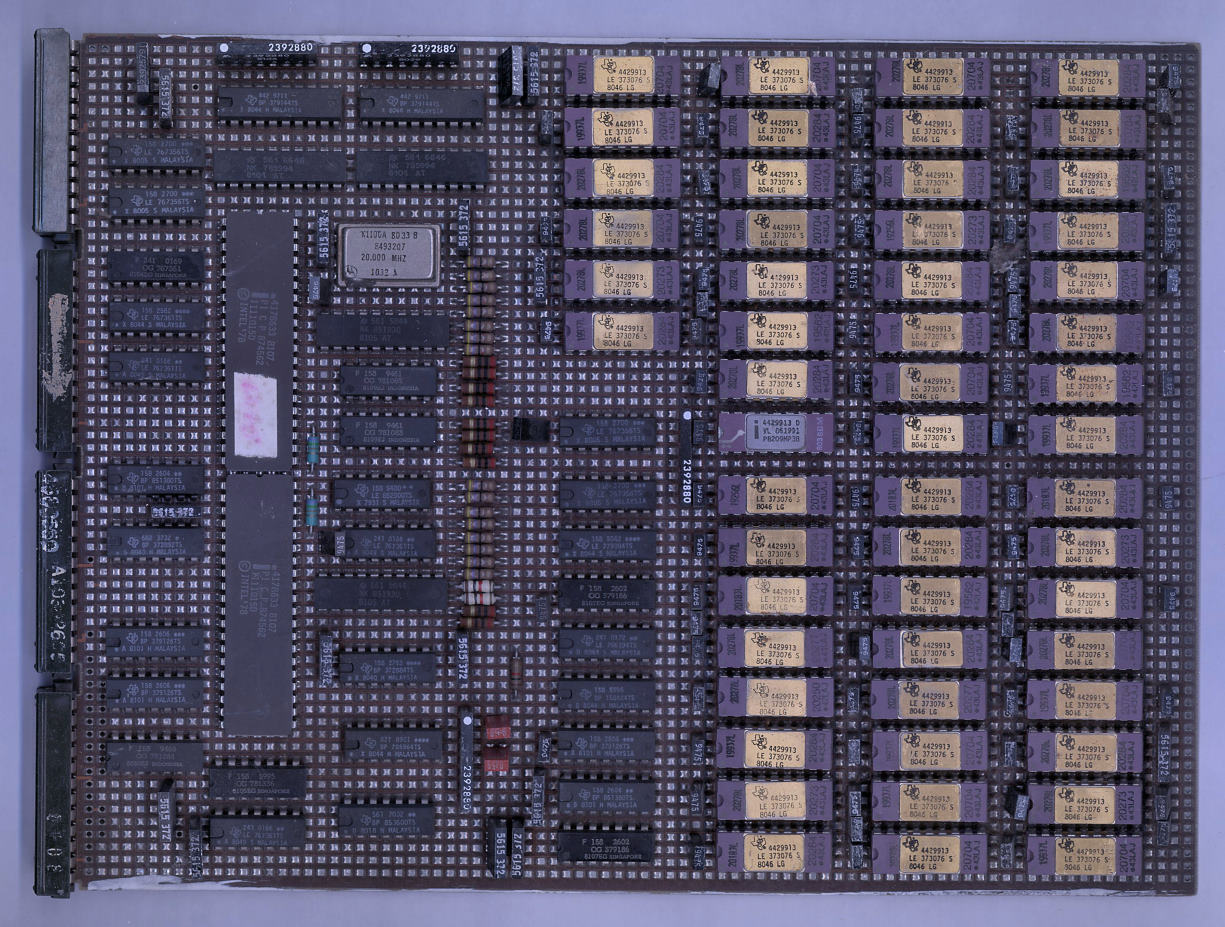

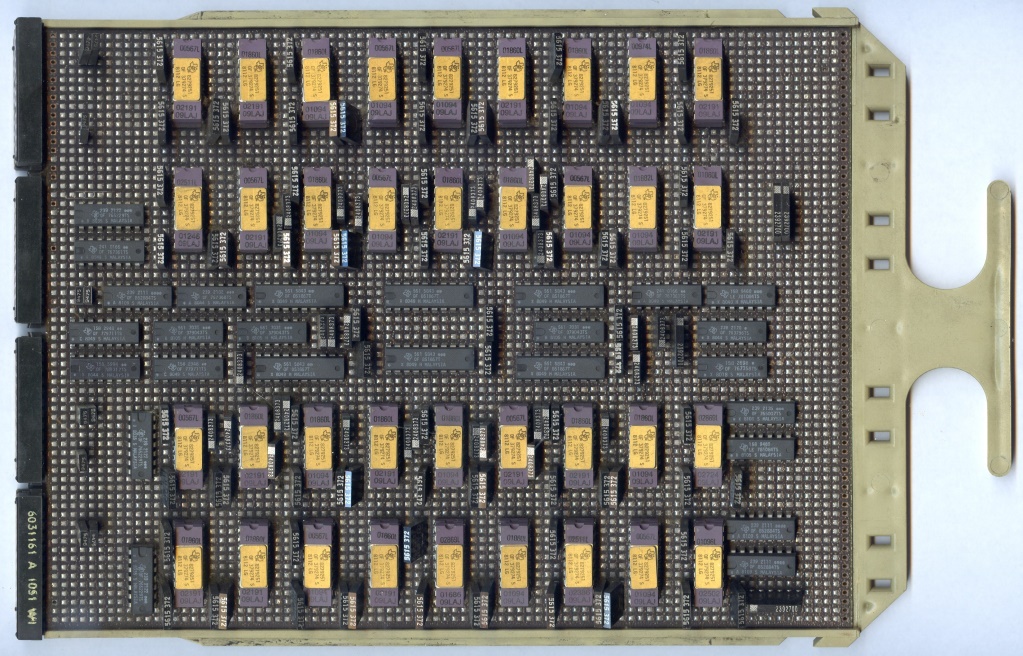

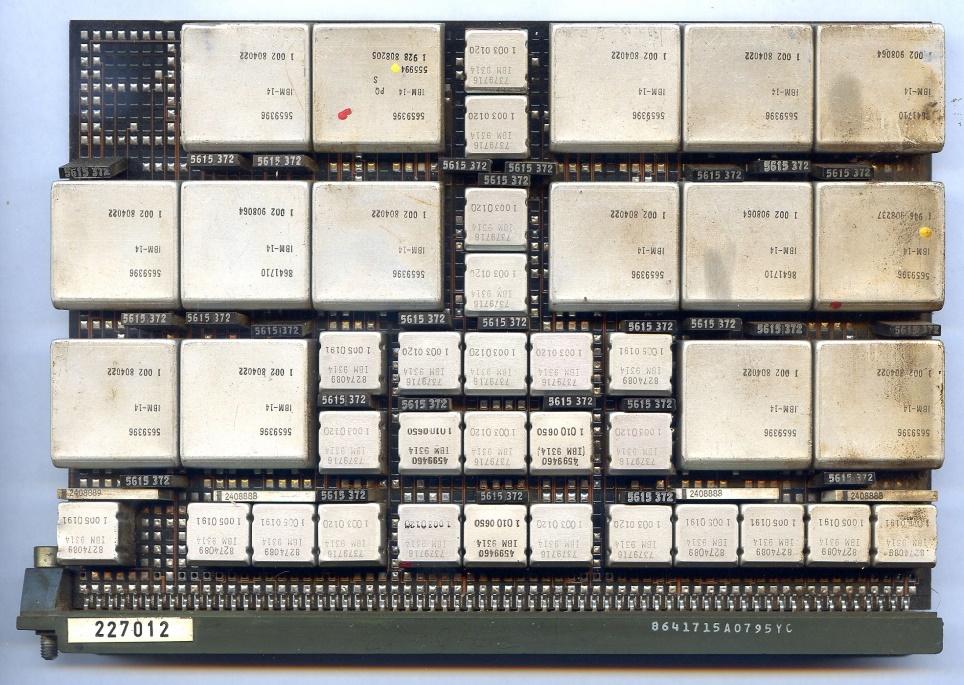

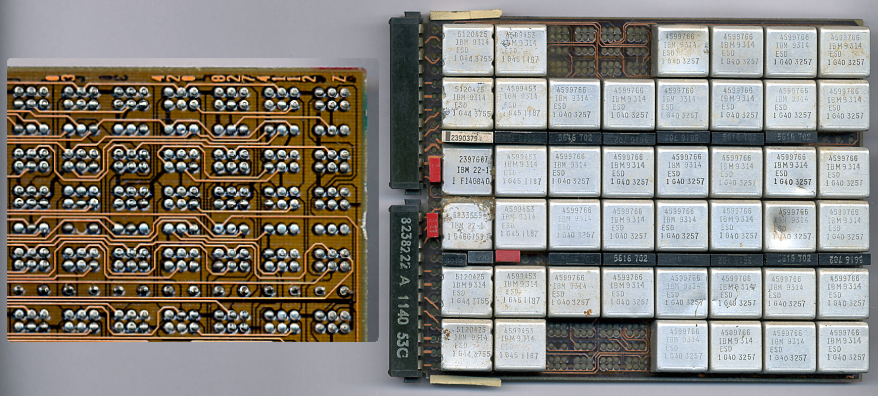

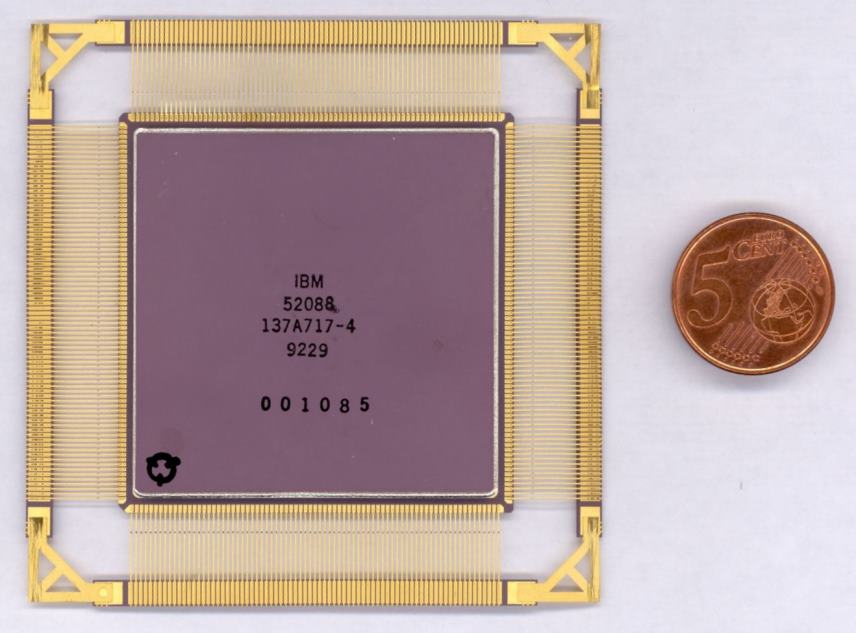

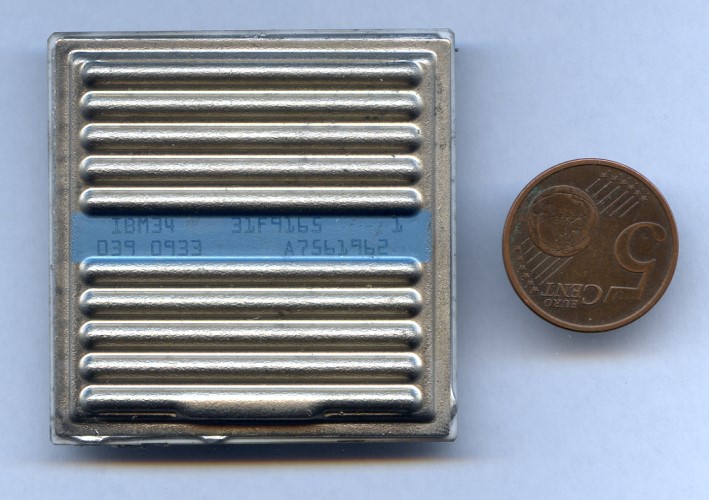

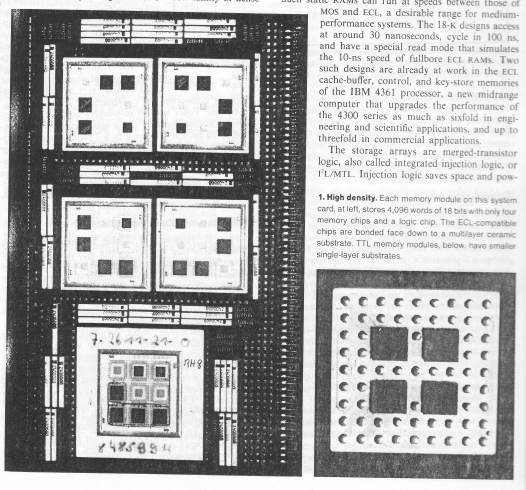

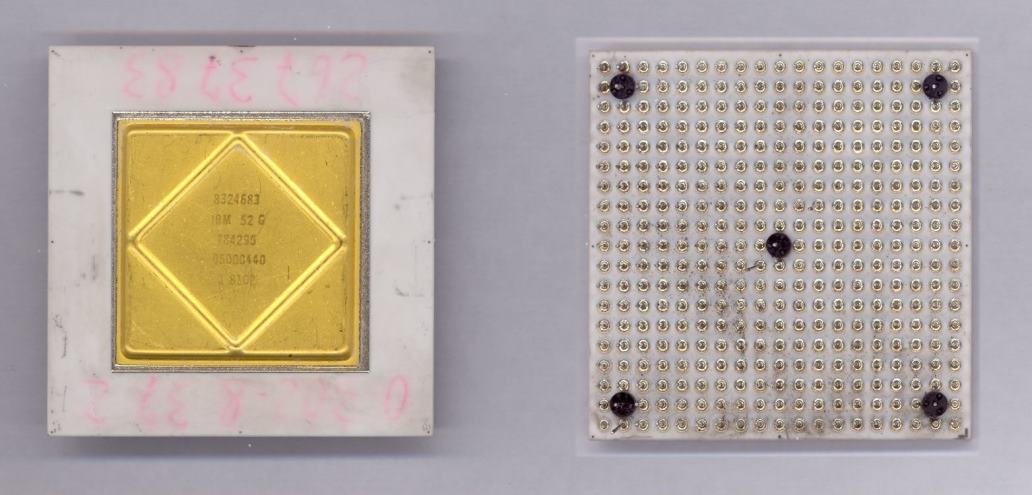

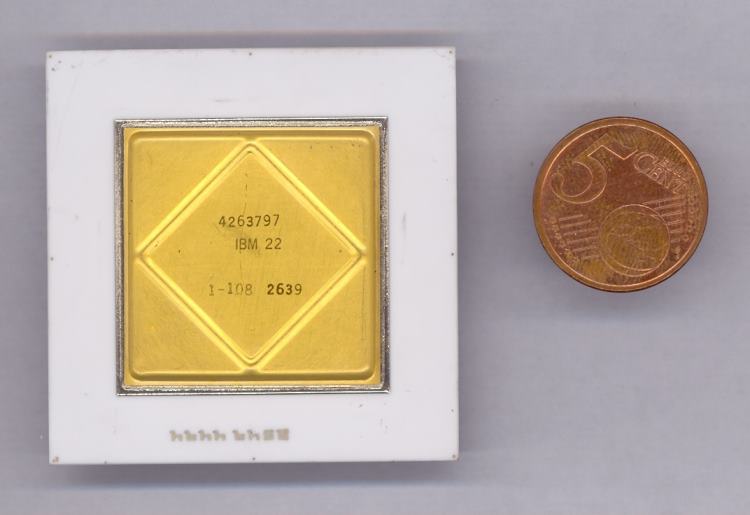

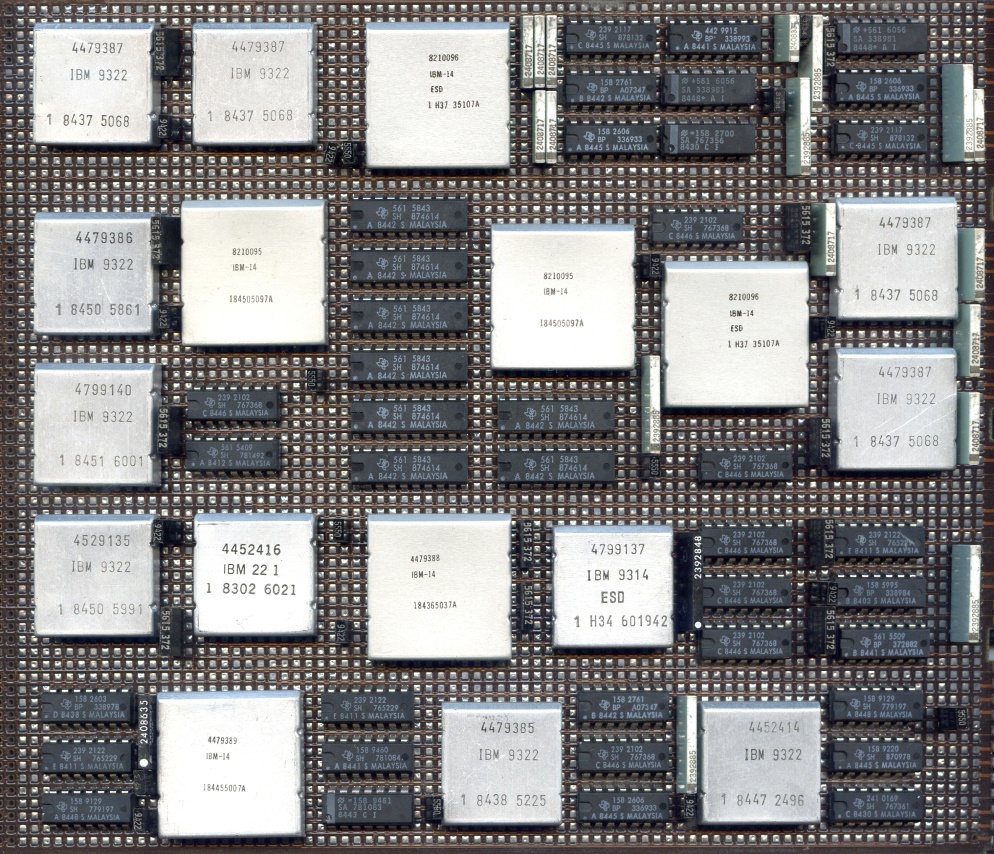

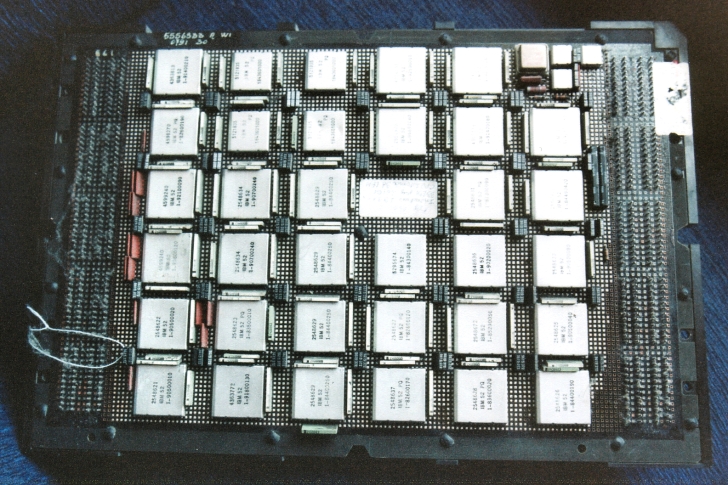

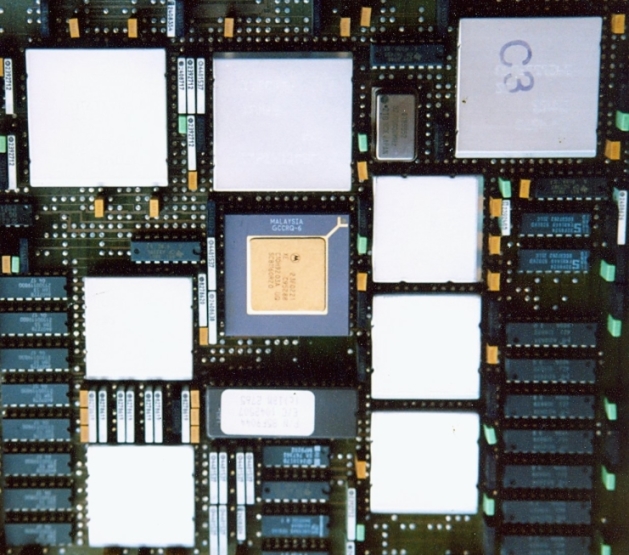

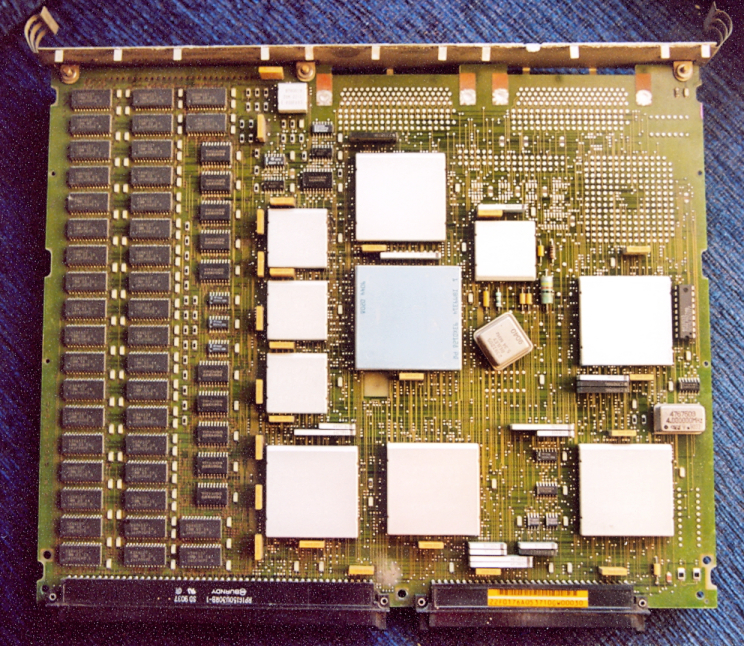

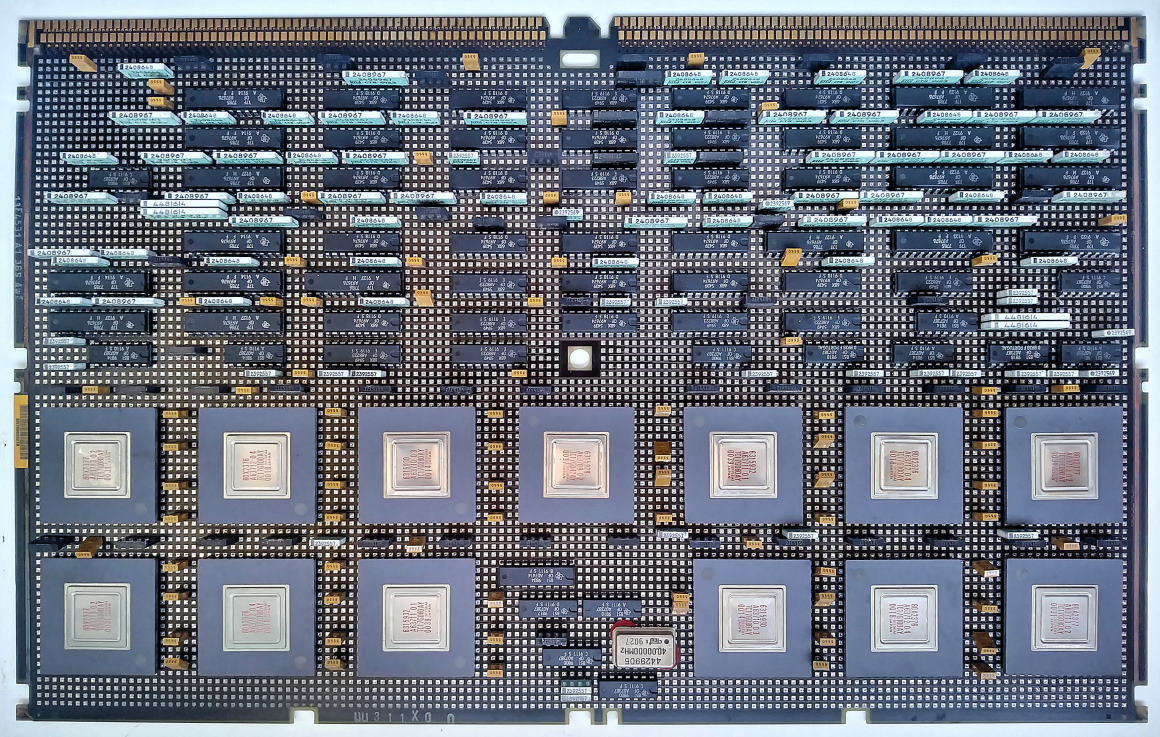

Memoria DRAM IBM a FET (1977) con una capacità di 8 kword con parità. Non mi è noto a quale macchina appartenesse; la scheda è comunque in "stile MST". Ciascun modulo contiene 2 integrati di memoria; il resto sono comuni TTL Texas Instruments denominati, in gergo IBM, VTL (Vendor Transistor Logic, cioè "TTL di terze parti"). Nella mia esperienza tutti i moduli "IBM 74" così come gli "IBM 7070" si sono rivelati memorie RAM. Come noto, c'è una lunga discussione tra appassionati e collezionisti circa il significato esatto di queste sigle, in mancanza di documentazione ufficiale; l'opinione prevalente, che condivido, è che esse identifichino l'impianto di produzione dei chip e dei moduli.