Chip e schede varie (2) - Interesting chips & cards (2)

Principali novità e modifiche (dal 1.1.2020): Intel Pentium 4 Prescott paperweight, Amdahl 5860 board, Amdahl 470/V6 MCC CPU module, Cmosis-Leica medium format sensor prototype, NCR Century paperweight, Amdahl 580 paperweight, Amdahl 470 V6 paperweight, Cray Y-MP C90 paperweight, Cray Y-MP paperweight, Solbourne SPARC board, Burroughs large board, Bull DPX2-360 CPU board (68040RC), Italtel 68040RC/Transputer T425 board, Unisys 5000 CPU board (4×68020), Altos 3068 CPU board, Wang VS5000 CPU board, Intel EPROM evolution paperweight, Convergent S280 CPU board, Concurrent Computer Corp. Micro-5 3200 CPU card, Zilog S8000 CPU card, HP Superdome CPU board (4×PA-8900), Elbit Systems military-grade CPU card with Motorola 68040RC, Ericsson card with Vitesse VGFX350 GaAs VLSI gate array (350K NAND-equivalent gates), Evans & Sutherland ESIG-3000 Vector Scanner board, E&S ESIG-1000 boards, Abekas Mira dual CPU board (2×Motorola 68000), AT&T promotional card with 256 kbit and 1 Mbit DRAM chips, Intel Pentium MMX Wafer, 8th Microprocessor Forum (1995) leather binder with embedded chips, Intergraph board with Clipper C3 CPU, MIPS R3000A wafer, Cray 1 ECL card, Russian avionics card (MIG-35?) with 2 ADSP-2101, Motorola 88K-based CPU card, Microprocessor Forum (1992) big lucite paperweight with many embedded chips of that year, Prime 2950 CPU board, Prime 4000 CPU board, CDC 7600 circuit module, Hitachi F7/MP5600 MCM, Hitachi HITAC M-220K MCM, Siemens Nixdorf Primergy 350 P60 CPU

Questa pagina raccoglie materiali di diversa natura appartenenti alla mia collezione, tutti a mio avviso interessanti: microprocessori ed integrati particolari, schede, memorie ecc. Vedete anche pagina 1.

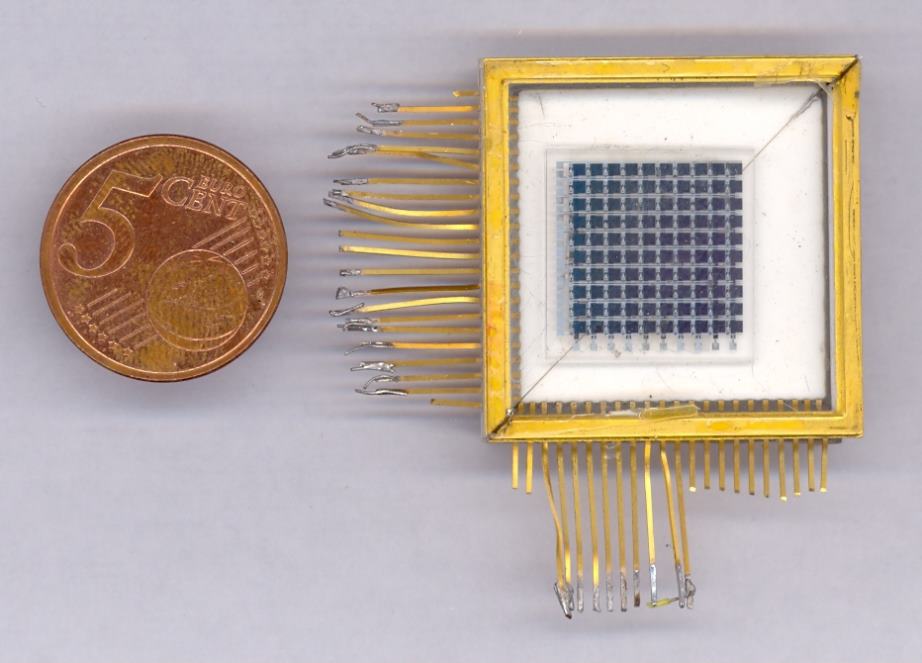

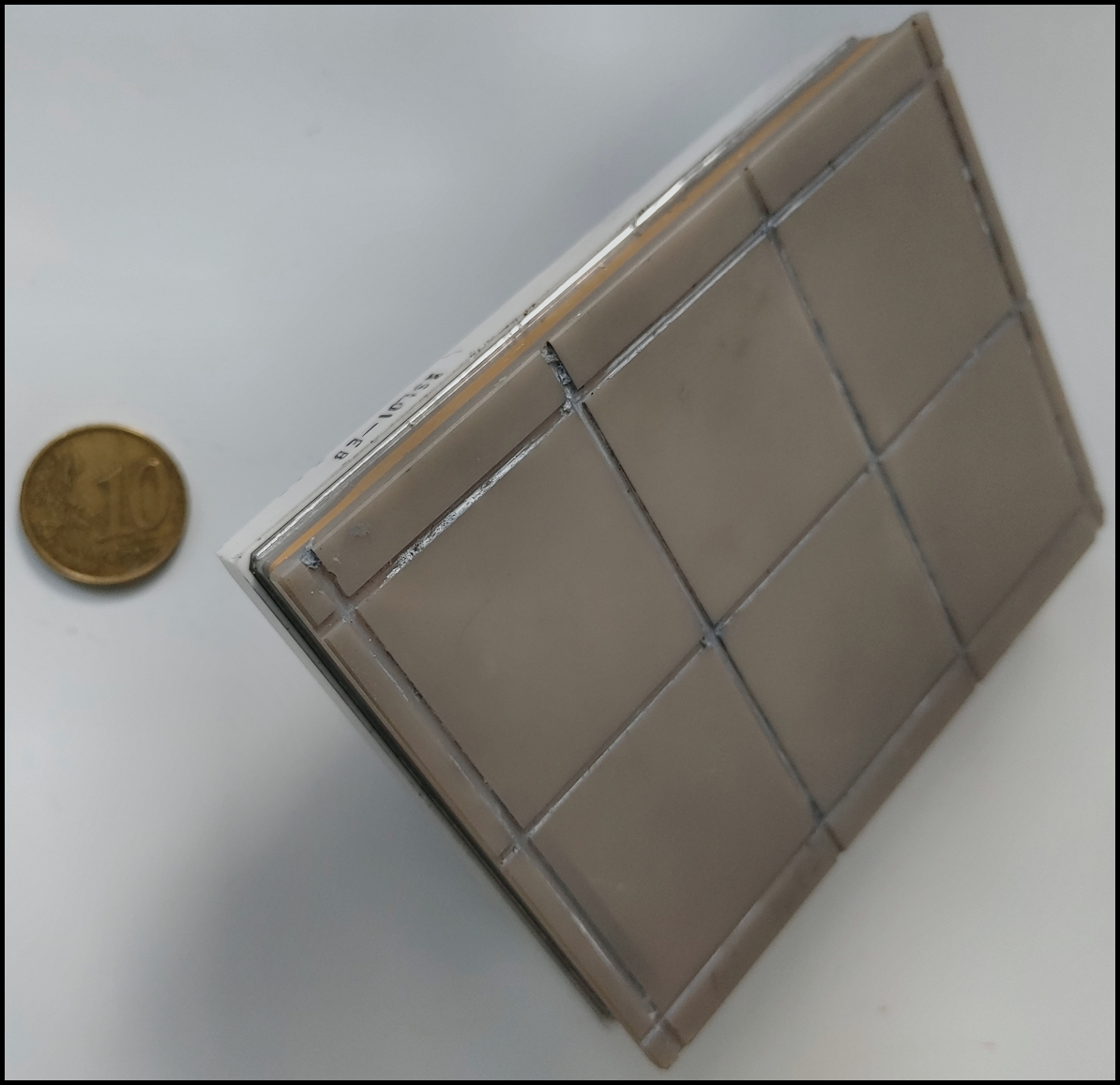

Questo è un vero "oggetto misterioso" nel senso che non assomiglia a nessun tipo conosciuto di componente e non riporta nessuna sigla o data che possa aiutare ad identificarne natura e provenienza. E' chiaramente un prototipo o una versione sperimentale, ma di che cosa? Un sensore? Un qualche altro tipo di componente ottico? Una memoria? Al momento è impossibile dire di più.

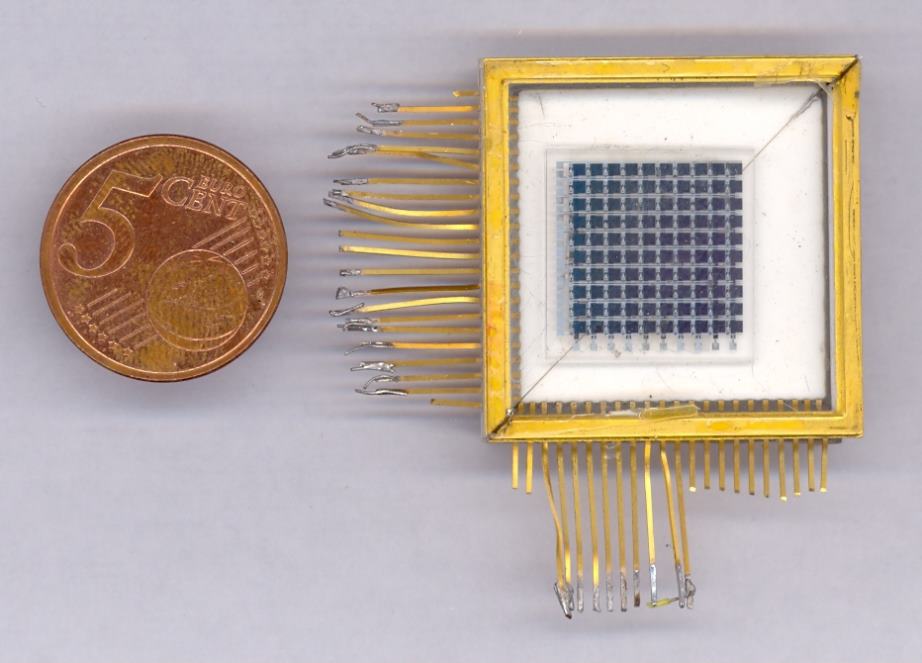

Prototipo di integrato ibrido per avionica fabbricato da TRW (1980).

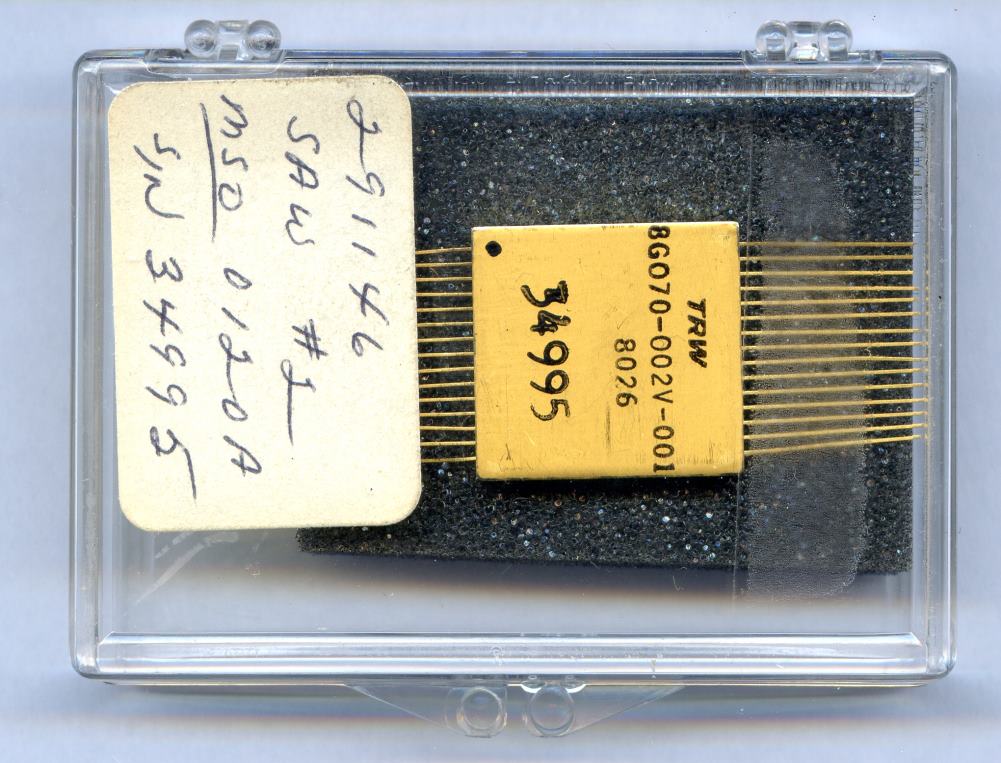

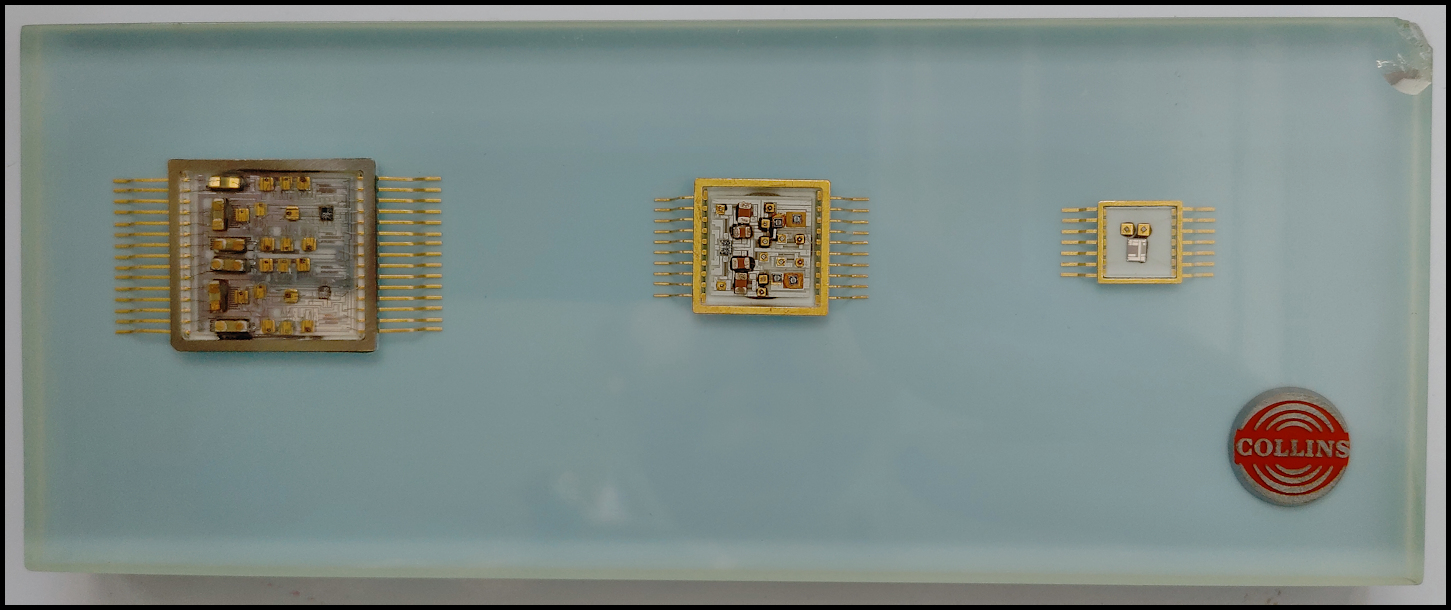

Fermacarte in plexiglass (circa 15 × 5 cm) contenente 3 esempi di moduli ibridi thick-film per applicazioni aerospaziali fabbricati da Rockwell Collins a inizio anni Settanta, con vari componenti discreti (resistenze, condensatori, transistor) ed alcuni integrati a bassa densità.

Circuito ibrido multi-modulo thick film di fabbricazione sovietica KMP204 (1989). Si tratta di un modulatore QAM (Quadrature Ampliture Modulation, modulazione numerica di ampiezza) prodotto per usi commerciali (iniziale della sigla "K").

Integrati RCA (la sigla "SSTC" sta per Solid State Technology Center) montati un un apparato per radionavigazione DECCA (1984).

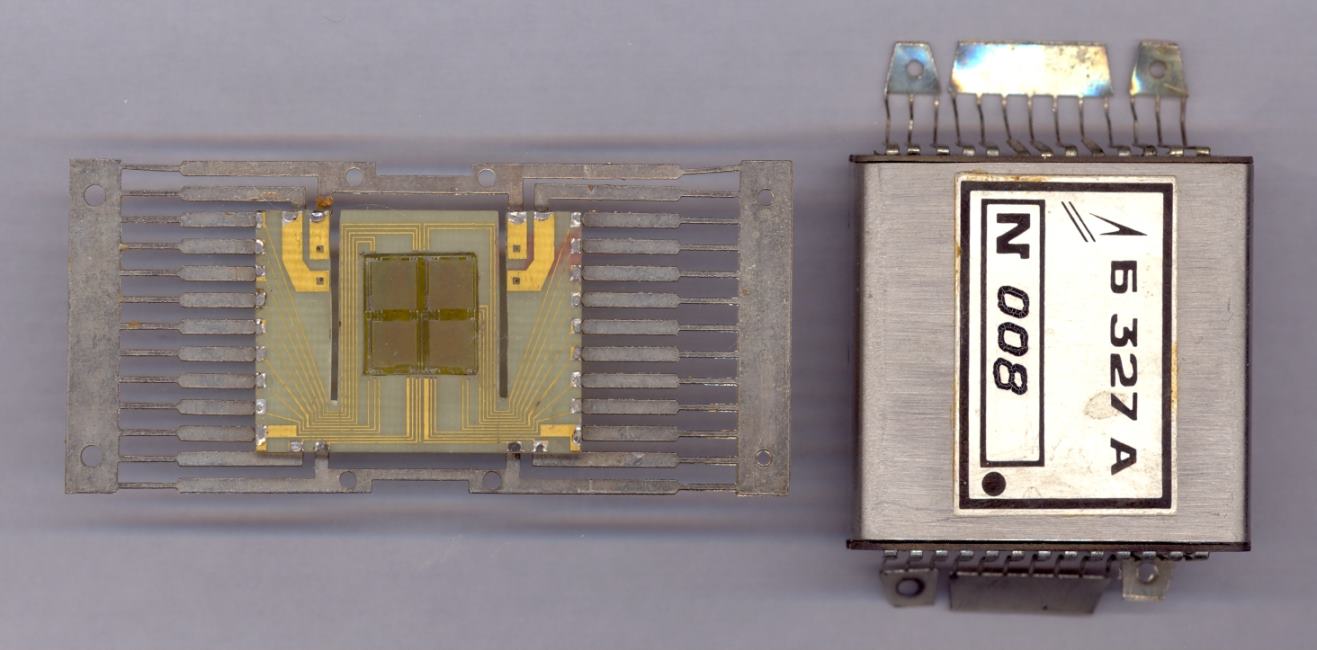

Due prototipi di memorie a bolle magnetiche di fabbricazione sovietica, di cui uno -a sinistra- incompleto, privo del magnete permanente.

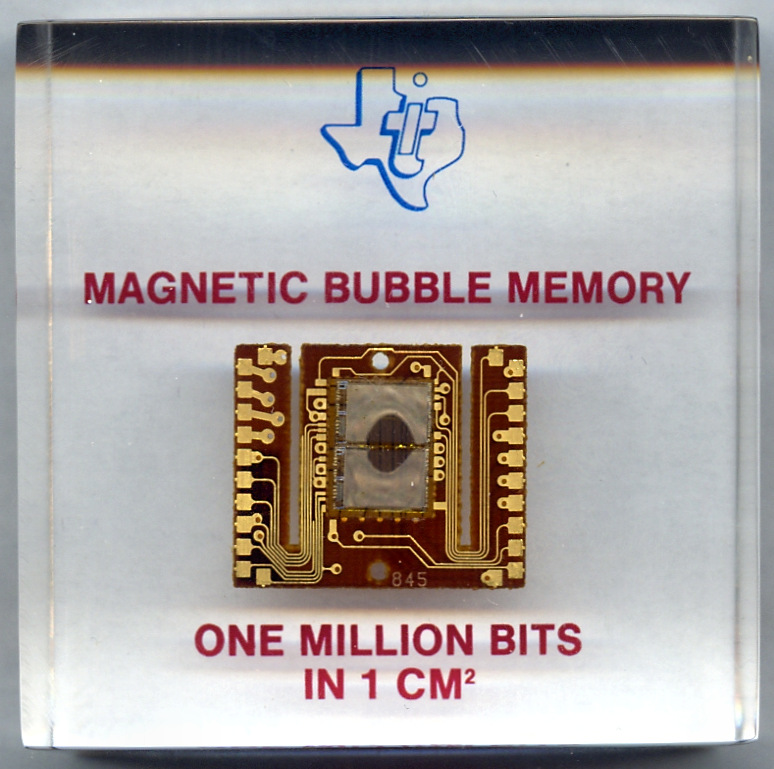

Fermacarte Texas Instruments con memoria a bolle magnetiche da 1 Mbit, 1985.

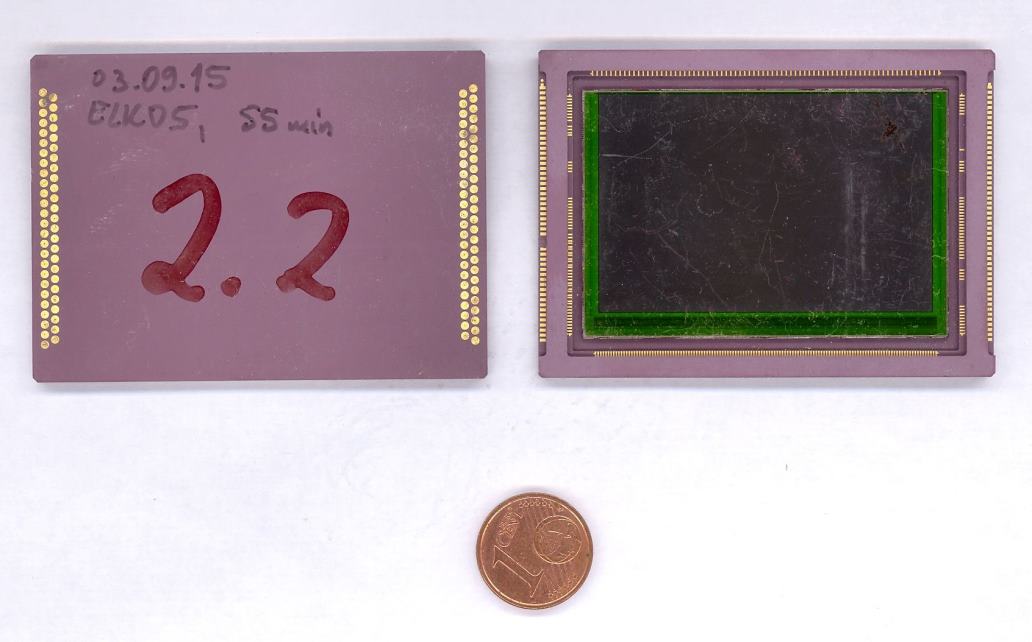

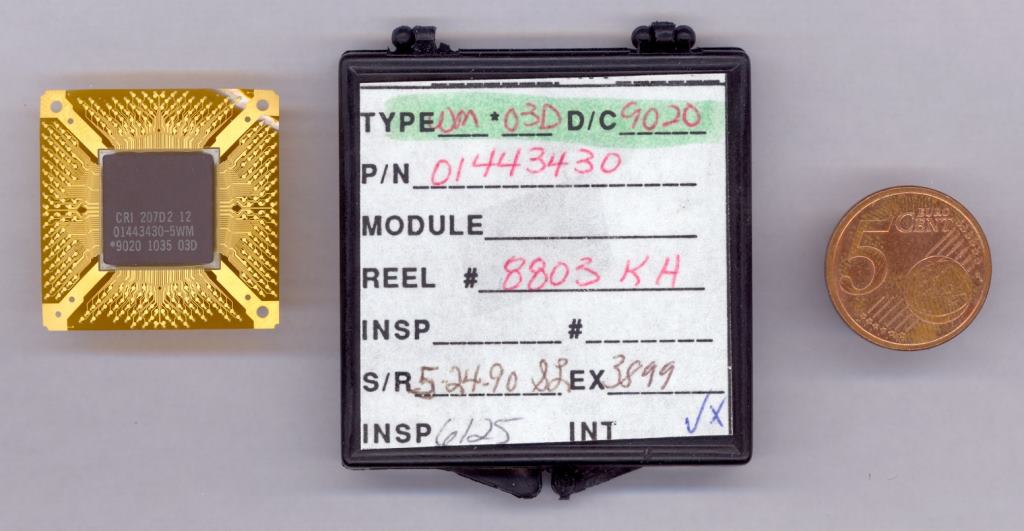

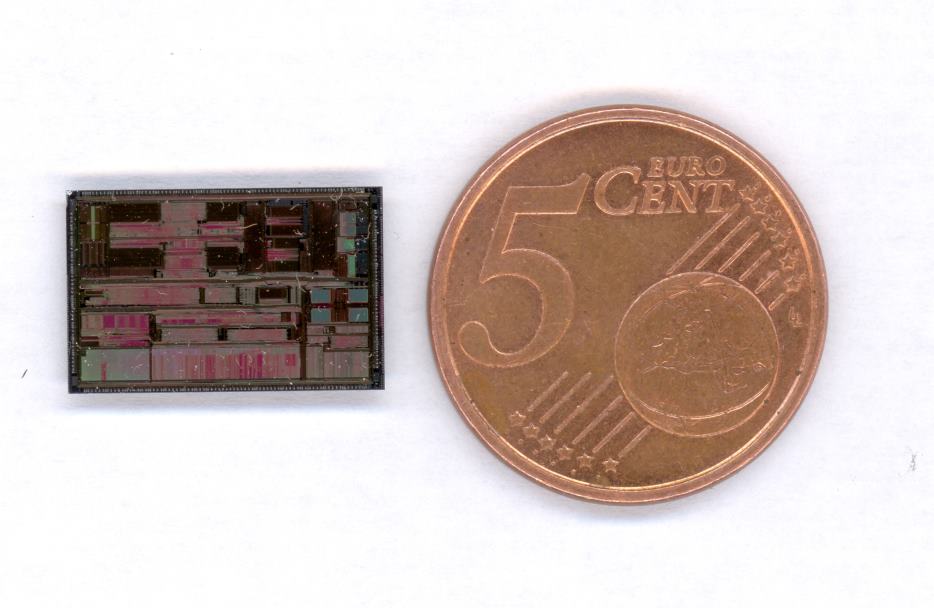

Prototipo di sensore d'immagine Cmosis/Leica medio formato (45×35 mm) da 30 megapixel, 2015, utilizzato in alcuni dorsi digitali della stessa Leica e, in una versione leggermente diversa, in apparati di machine-vision e motion detection (rilevamento del movimento) ad alta risoluzione.

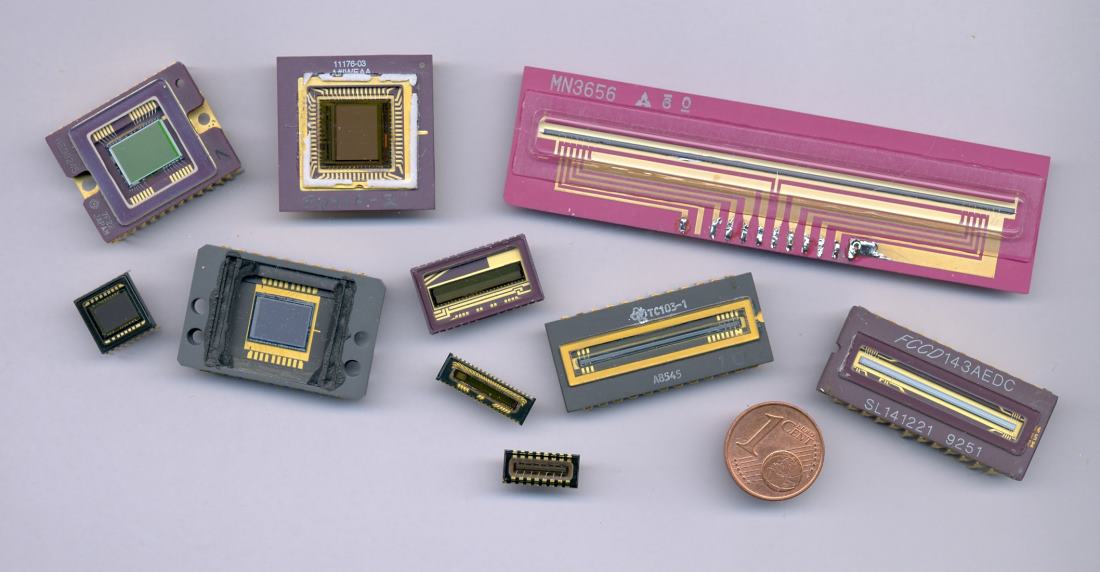

Vari tipi di sensori CCD.

Fermacarte RCA contenente un prototipo di sensore CCD da 128×160 pixel, circa 1982, uno dei primi fabbricati con questa tecnologia, e un dettaglio della sua struttura.

Fermacarte pubblicitario NCR dedicato alla famiglia di computer NCR Century, introdotta nel 1968, che rappresenta la prima serie di elaboratori NCR interamente basata su circuiti integrati monolitici. Nella parte sinistra si vedono appunto un chip logico (da precisare che tutte le funzioni erano ottenute collegando tra loro integrati di un unico tipo, contenenti due o quattro porte NAND, per formare circuiti più complessi come flip-flop, registri ecc.), un integrato parzialmente finito ed uno completo, fabbricato da Texas Instruments e siglato NCR80. A destra ci sono invece, in alto, due elementi di memoria a "barrette magnetiche" (rod memory), un tipo di memoria alternativa alla classica memoria a nuclei magnetici e derivato dalle memorie a film sottile (thin film), una parte della matrice contenente le barrette e, in basso, una testina di lettura/scrittura del disco magnetico. Tutti questi elementi sono interessanti perché la rod memory, introdotta nel 1964 sull'elaboratore NCR 315 RMC, è stata un'esclusiva delle macchine di questo produttore e perché l'unità disco del Century 100 rappresenta il primo esempio di hard disk commerciale a testine "volanti" (flying head), cioè testine che non vengono a contatto con la superficie magnetica ma rimangono sospese a una minima distanza da essa su un cuscino d'aria creato dalla rotazione del disco stesso. I vantaggi di questa tecnologia, poi diventata di uso universale, sono principalmente due: il venir meno dell'usura della superficie magnetica dovuta al contatto con la testina e la maggiore densità di registrazione, in quanto il "traferro" (separazione) esistente tra disco e testina ha l'effetto di concentrare il flusso magnetico.

Vedi: https://en.wikipedia.org/wiki/Rod_memory, http://www.thecorememory.com/NCR_Higashi.pdf, https://en.wikipedia.org/wiki/NCR_Century_100.

Un oggetto identico è visibile qui: http://www.chipsetc.com/ncr.html.

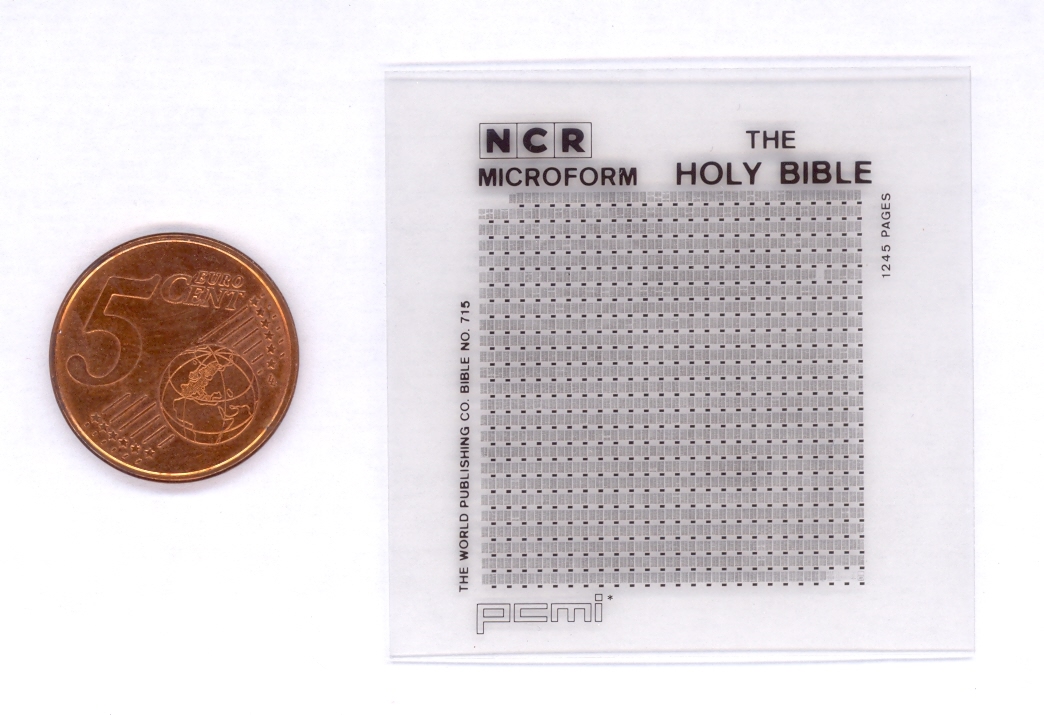

"The smallest Bible in the world". Tra la fine degli anni Cinquanta e la metà dei Sessanta ci fu, da parte di quasi tutti i principali produttori di computer dell'epoca, un'ondata di interesse nei riguardi di forme "alternative" di memorizzazione di dati e documenti. Tra di esse sembravano particolarmente promettenti quelle ottiche, in quanto basate su tecnologie già ampiamente collaudate ed impiegate -ad esempio- nei microfilm (considerando che già dagli anni Venti era possibile ridurre immagini di documenti in micropunti fotografici delle dimensioni di pochi decimi di millimetro). Attorno al 1960 la NCR sviluppò una nuova tecnica di microfilmatura chiamata PCMI grazie alla quale diventava possibile "memorizzare" un intero libro di più di mille pagine su un singolo "form" plastico di circa 2 centimetri di lato. NCR contava che tale tecnologia avrebbe potuto essere presto impiegata anche per la registrazione di documenti in formato digitale leggibile da calcolatori elettronici. Tra il 1962 ed il 1969 realizzò a fini promozionali qualche migliaio di "micro Bibbie" su Microform PCMI. La dimensione delle singole pagine (1.245 in totale) è a tal punto ridotta che il testo può essere letto soltanto con l'aiuto di un microscopio da almeno 100 ingrandimenti, visto che i caratteri sono alti circa 8 micron. Mentre le varie forme di microfilmatura sono state e tuttora sono ampiamente utilizzate quali mezzi convenienti per archiviare grandi quantità di documenti analogici in volumi ridotti, esse non hanno mai riscosso successo nella memorizzazione di dati digitali rimanendo confinate in questo specifico settore a poche applicazioni di nicchia, ad oggi completamente soppiantate da mezzi più "ordinari" quali dischi rigidi, nastri magnetici ecc.

Scheda Intel MD-080 con memoria a bolle magnetiche Memtech da 1 MB e relativi chip di supporto (a sinistra) e, a destra, kit OEM Memtech BPK 70A con 1 modulo di memoria a bolle magnetiche da 1 MB identico all'altro e chip di supporto fabbricati da Intel e Siliconix. La MemTech, oggi scomparsa, era una società californiana che negli anni Ottanta aveva acquisito la divisione Intel Magnetics continuando per qualche tempo a commercializzare i prodotti di quest'ultima, finché le memorie a bolle -rimaste sempre un prodotto di nicchia o, se volete, una promessa mancata- non cedettero definitivamente il passo a quelle a semiconduttore.

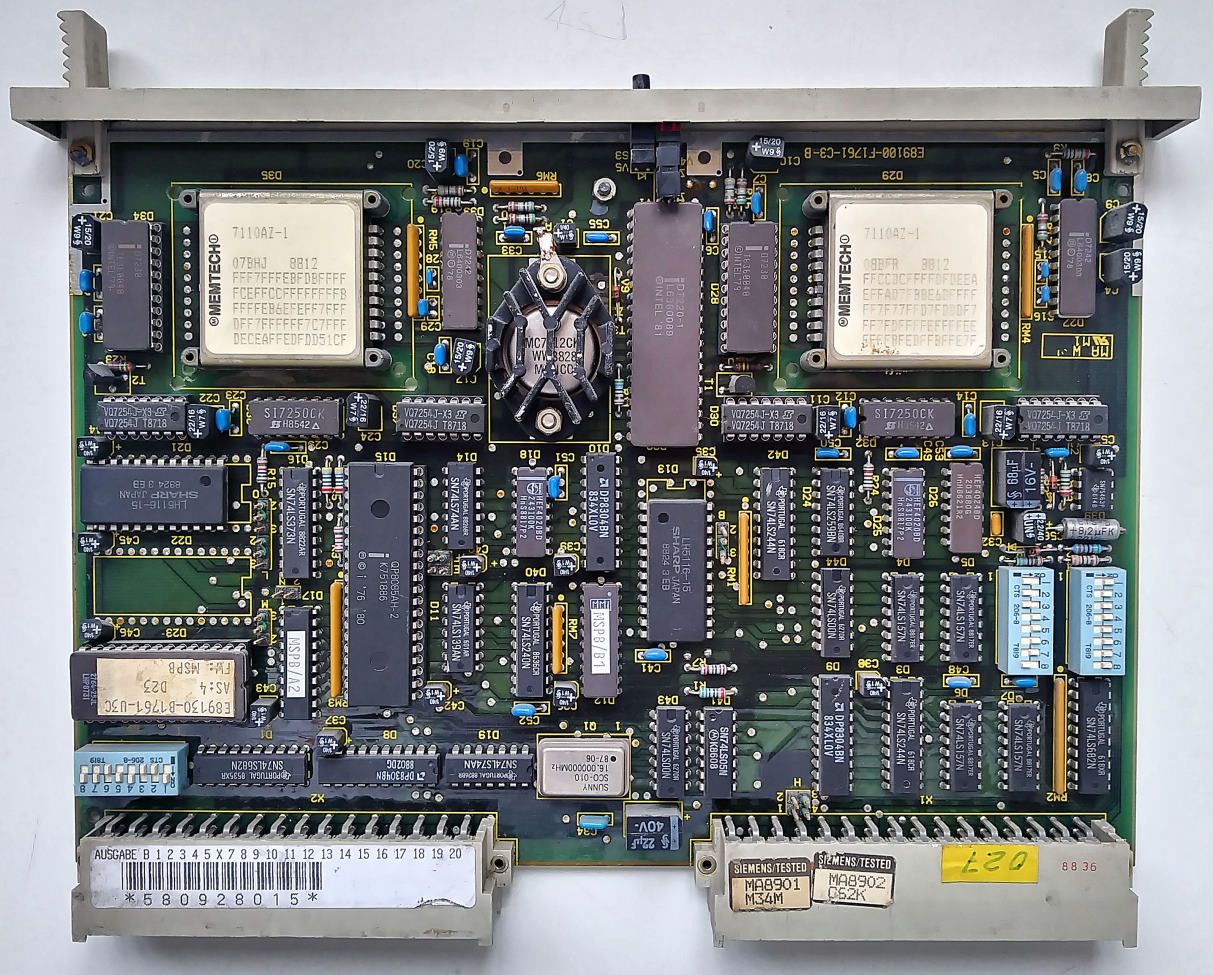

Scheda Siemens (1988) con 2 moduli di memoria a bolle magnetiche da 1 MB Memtech (spin-off di Intel Magnetics) 7110AZ-1, probabilmente il tipo più diffuso di memorie di questo tipo. La 7110 fu sviluppata e commercializzata da Intel dopo aver acquistato da IBM il diritto a sfruttare alcuni suoi brevetti relativi all'allora nuova tecnologia delle memorie a bolle magnetiche. Qui si trova il suo datasheet: http://www.wylie.org.uk/technology/computer/bubblmem/7110.pdf.

Vedi: http://www.wylie.org.uk/technology/computer/bubblmem/bubblmem.htm.

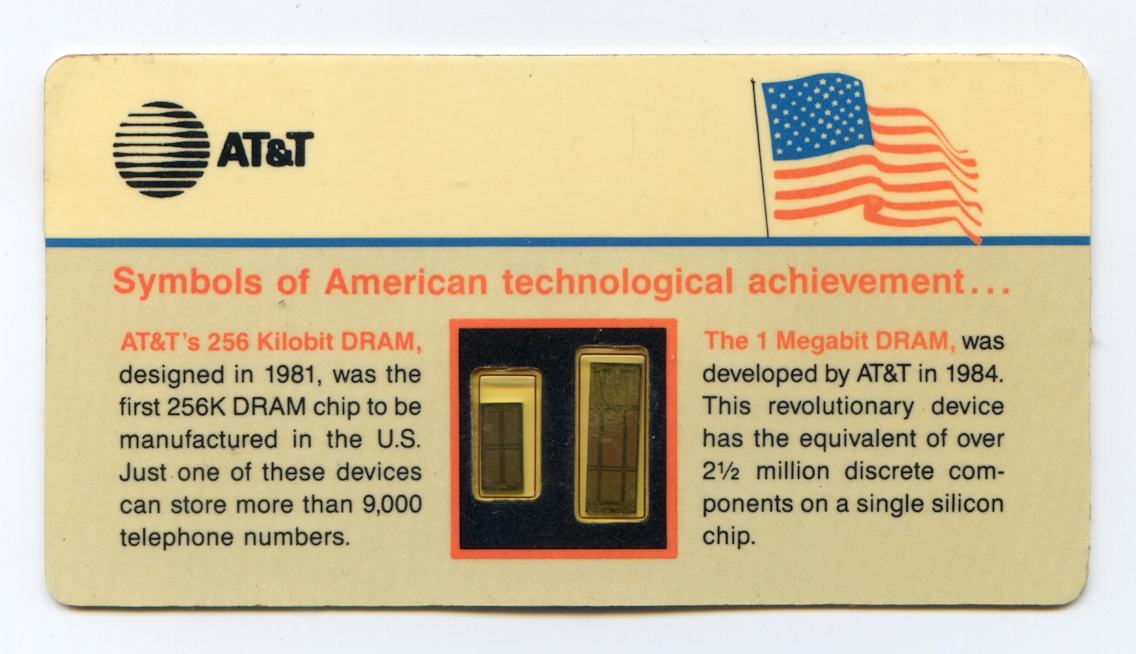

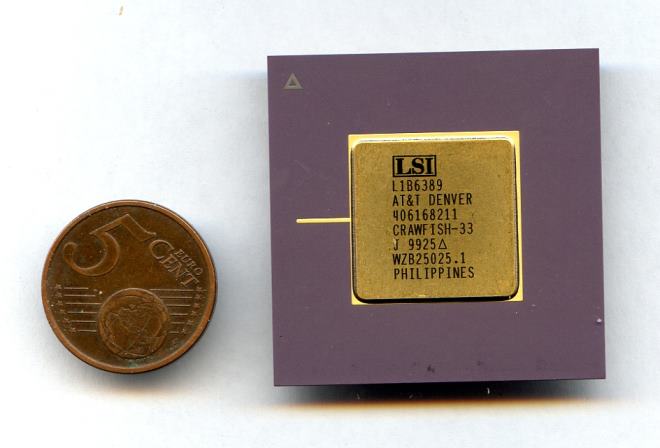

Schedina pubblicitaria della AT&T in formato carta di credito (1985) contenente due chip di DRAM, rispettivamente da 256 kbit e da 1 Mbit.

Fermacarte di plexiglass contenente un chip di SRAM CMOS da 64 kbit fabbricata da Lattice Semiconductors (1984).

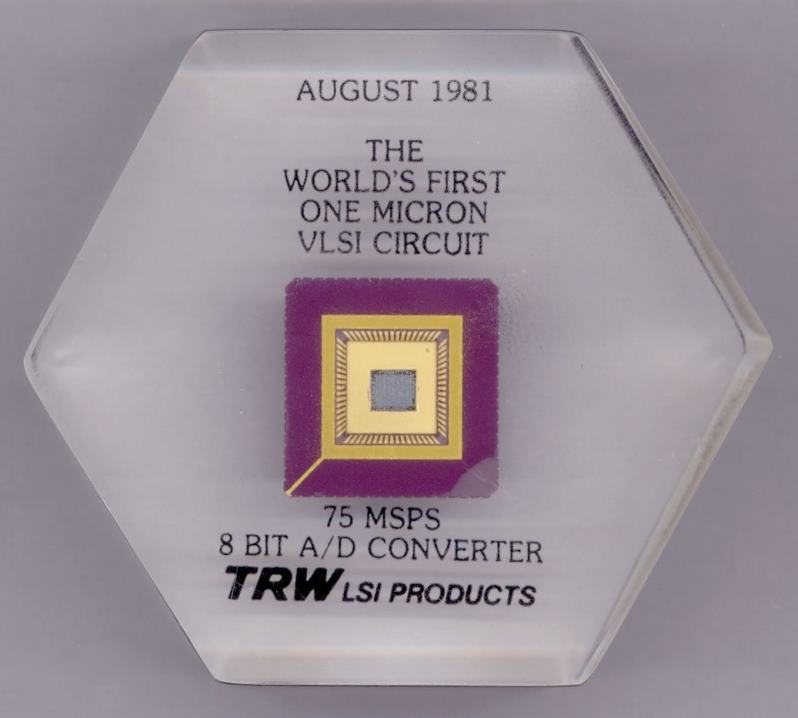

Fermacarte pubblicitario della TRW (acronimo di Thompson, Ramo e Wooldridge) che ricorda la produzione del primo integrato VLSI commerciale con processo (CMOS) a 1 micron. La TRW era una grande società statunitense di ingegneria, specializzata nei settori aerospaziale, automobilistico e difesa. Introdusse molte innovazioni in vari campi tecnologici (circuiti integrati, telecomunicazioni, reti di computer...). E' nota soprattutto per aver progettato e prodotto alcune famose sonde spaziali come la Pioneer 1 e la Pioneer 10 oltre che per aver introdotto il primo sistema di airbag per automobili ed aver partecipato alla realizzazione dei primi missili balistici intercontinentali USA (Atlas e Titan-I).

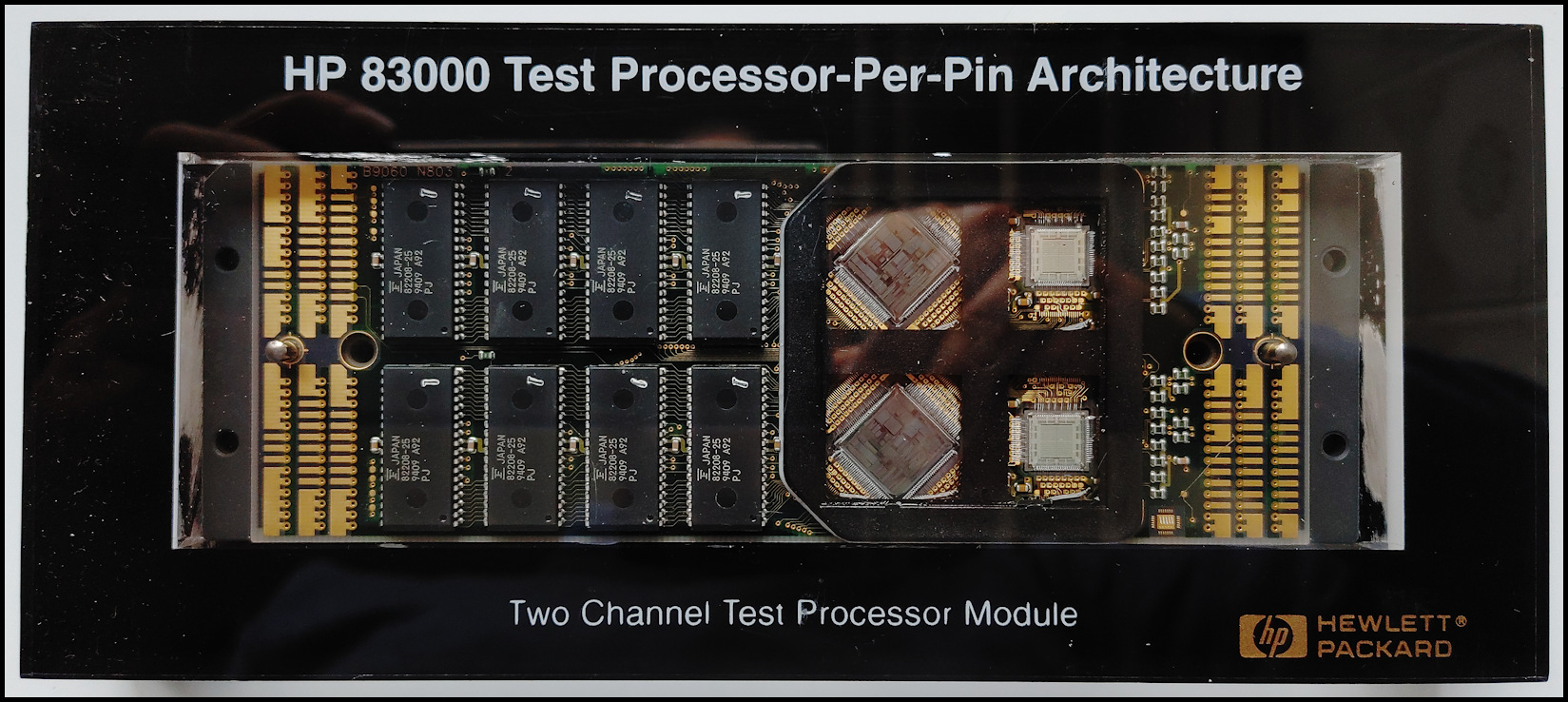

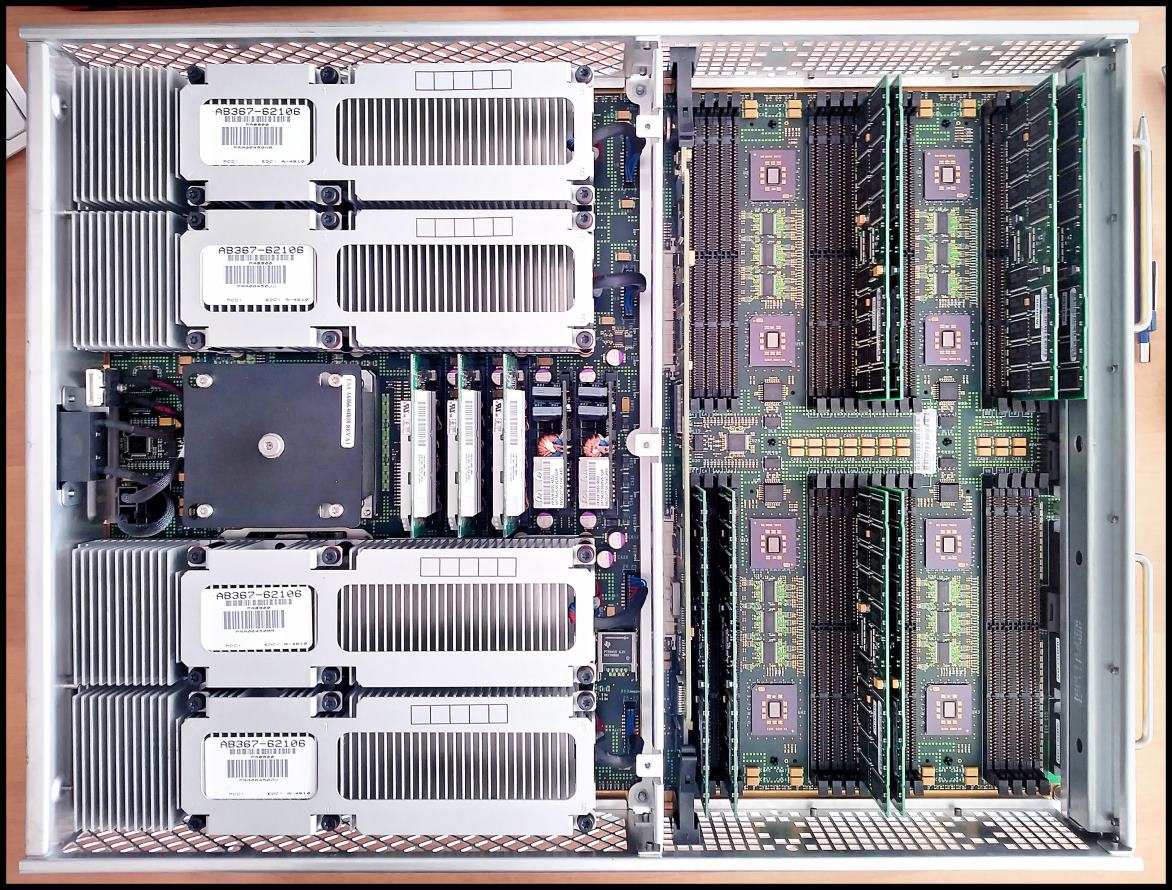

Fermacarte HP (1994/5), circa 20×10 cm, che contiene un modulo processore/memoria utilizzato nel HP 83000, un sofisticato apparato per prove automatizzate su circuiti integrati e microprocessori, utilizzato appunto nelle fasi di sviluppo di e con questi dispositivi. Le 2 CPU visibili hanno architettura HP PA-RISC.

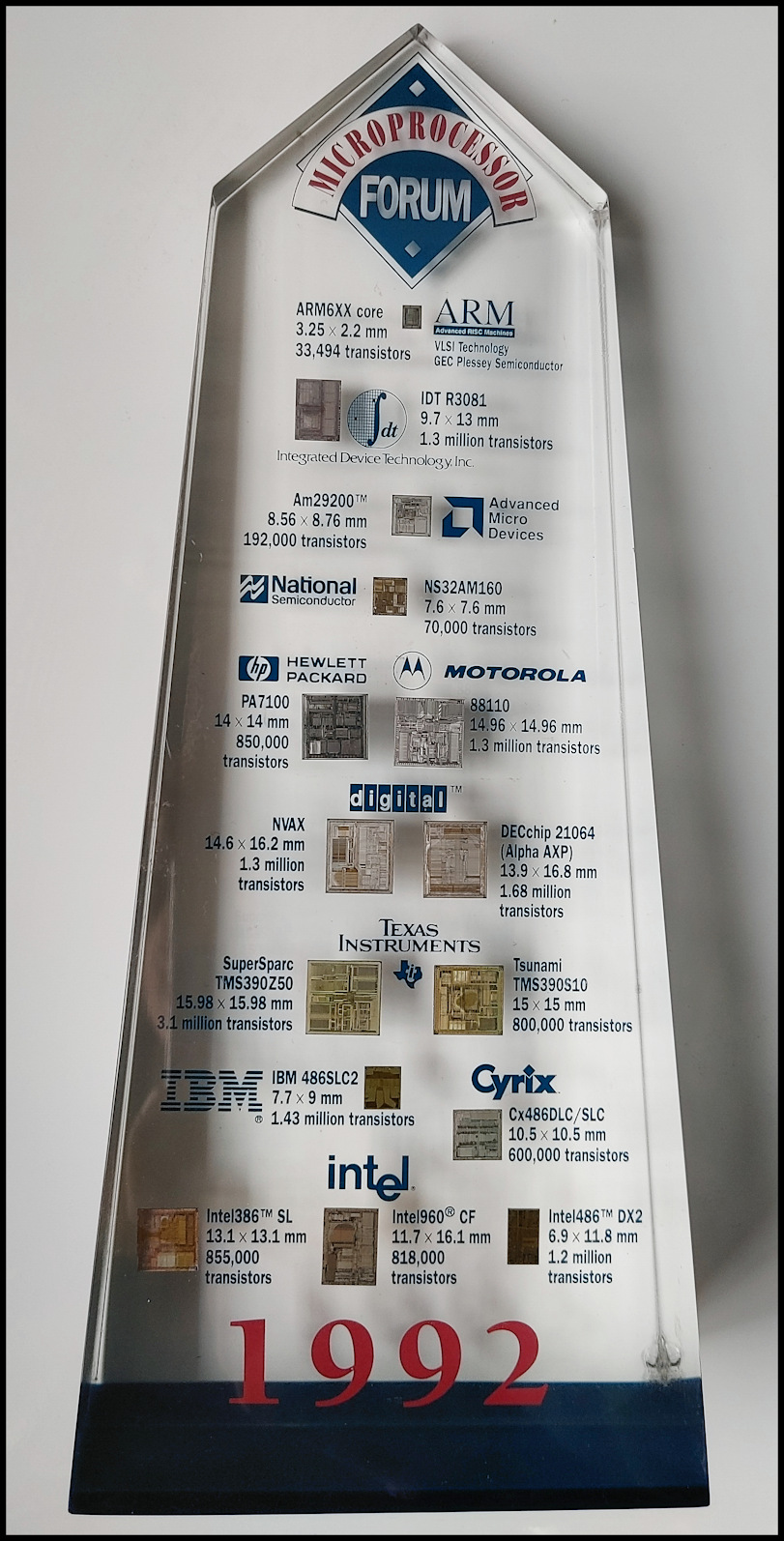

In occasione dell'edizione 1992 del Microprocessor Forum è stato realizzato questo corposo fermacarte in plexiglass (le dimensioni sono, approssimativamente, 15×35 cm e peso quasi 2 kg) contenente i principali chip presentati o discussi nel corso del convegno.

Intel i386 SL (versione CMOS a basso consumo, per computer portatili, del 386SX con supporto hardware alla cache esterna ed al System Management Mode): http://www.cpu-collection.de/?l0=co&l1=Intel&l2=i386+SL (un esempio di laptop che utilizza questa CPU è visibile qui: http://www.computinghistory.org.uk/det/37842/Zenith-MasterSport-386SL/).

Intel i960 CF (evoluzione, migliorata e più veloce, del RISC superscalare i960 CA): http://datasheets.chipdb.org/Intel/80960/PRODBREF/272211_3.PDF.

Cyrix Cx486DLC: http://www.cpu-collection.de/?l0=co&l1=Cyrix&l2=Cx486%20DLC, https://en.wikipedia.org/wiki/Cyrix_Cx486DLC.

IBM 486SLC/2 (evoluzione dell'IBM 386SLC, impiegato nei PS/2 mod. 56 e 57): https://en.wikipedia.org/wiki/IBM_386SLC, http://john.ccac.rwth-aachen.de:8000/alf/ps2_56slc2/.

Raccoglitore per documenti ed appunti (binder, in inglese) distribuito agli iscritti alle sessioni di conferenze dell'ottavo Microprocessor Forum (1995). E' una cartellina in similpelle di circa 23×30 cm nella cui copertina sono inseriti i chip dei principali microprocessori presentati e discussi al Forum. All'interno ci sono un blocco note col logo del Microprocessor Forum ed un libretto (Die Photogallery) con fotografie e brevi descrizioni di tutti i chip. Questi binder erano disponibili in quantità limitata e dovevano essere prenotati per tempo. I processori inseriti nella copertina hanno tutti raggiunto una fase di sviluppo avanzato, o sono entrati in produzione, tra la fine del 1994 e l'estate del '95.

Vedi: https://www.computerhistory.org/revolution/digital-logic/12/330/1580 (edizione 1996), https://www.computerhistory.org/collections/catalog/102674746 (edizione 1998), http://archive.computerhistory.org/resources/access/text/2013/03/102677779-05-01-acc.pdf.

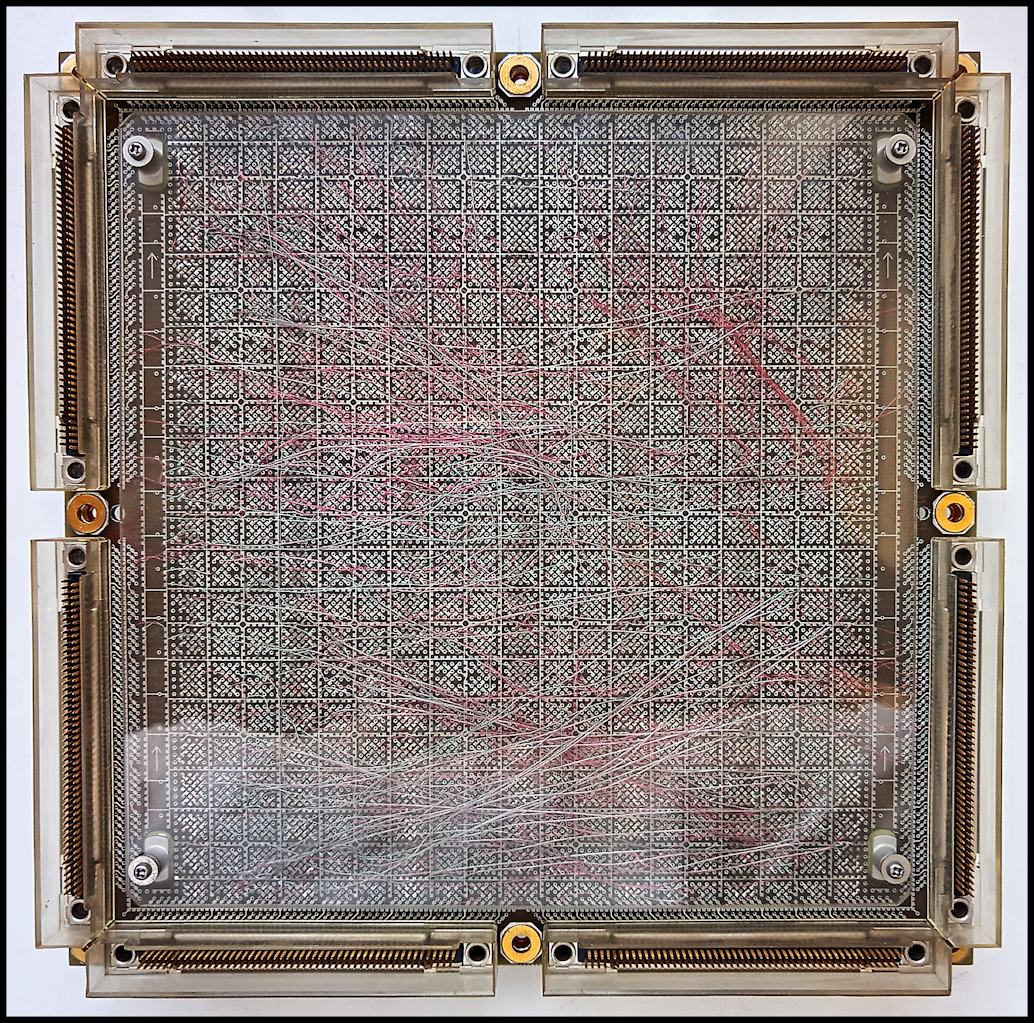

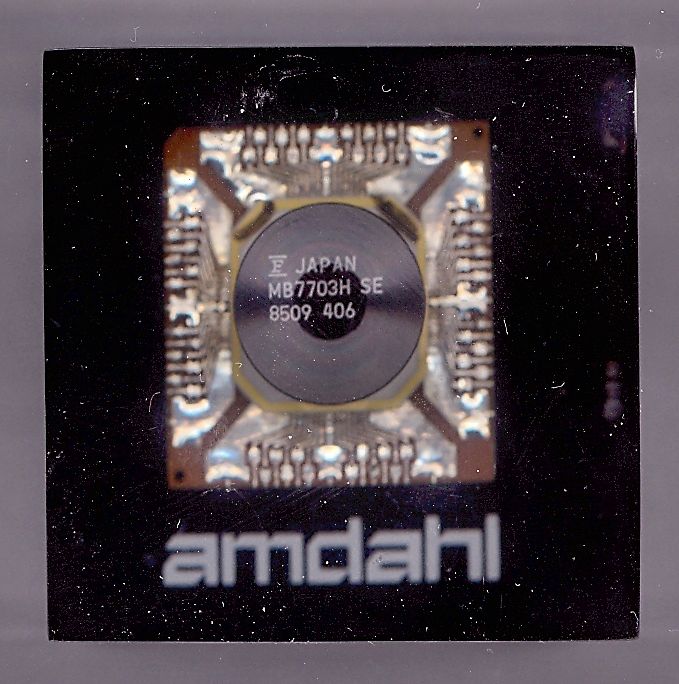

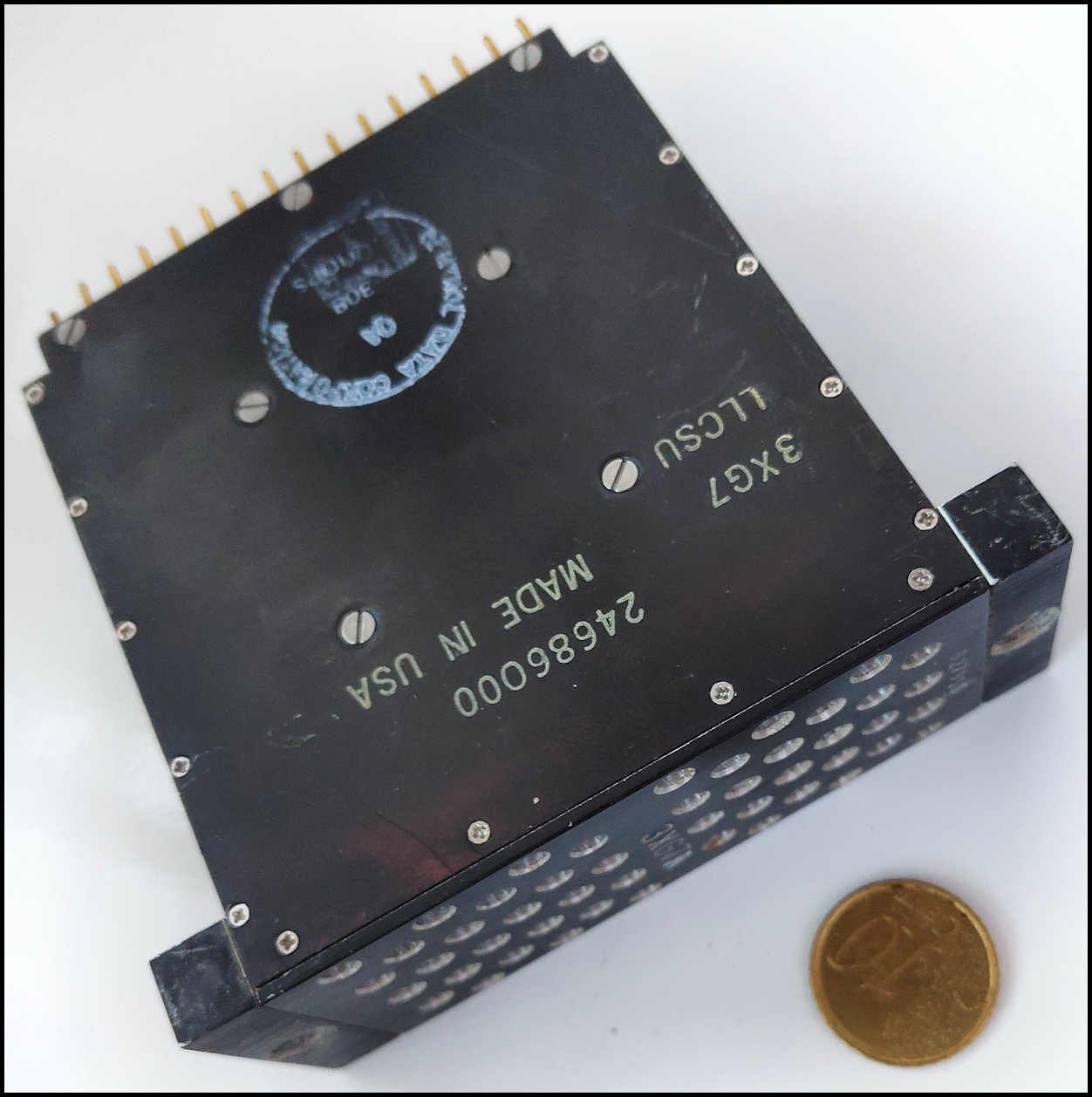

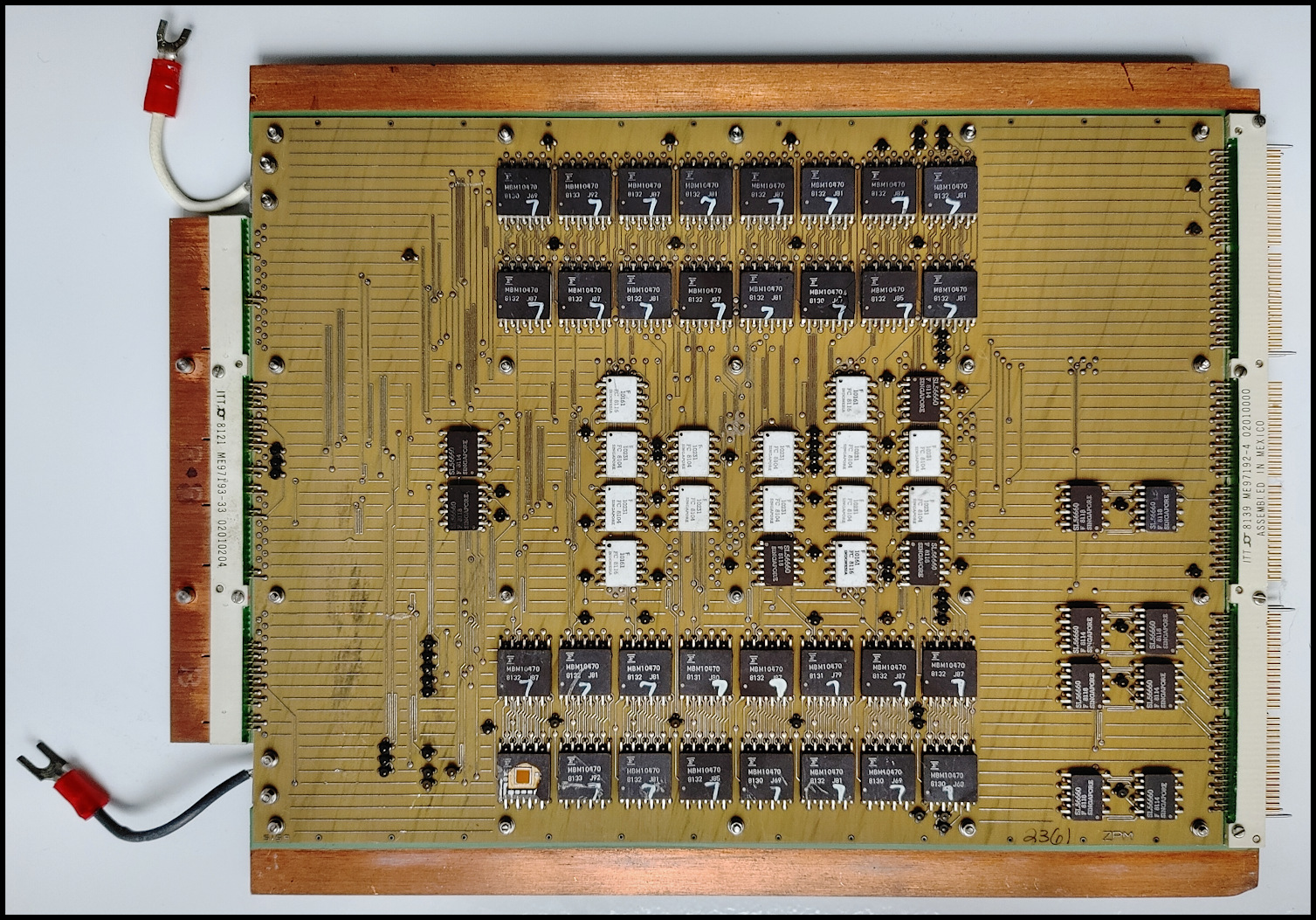

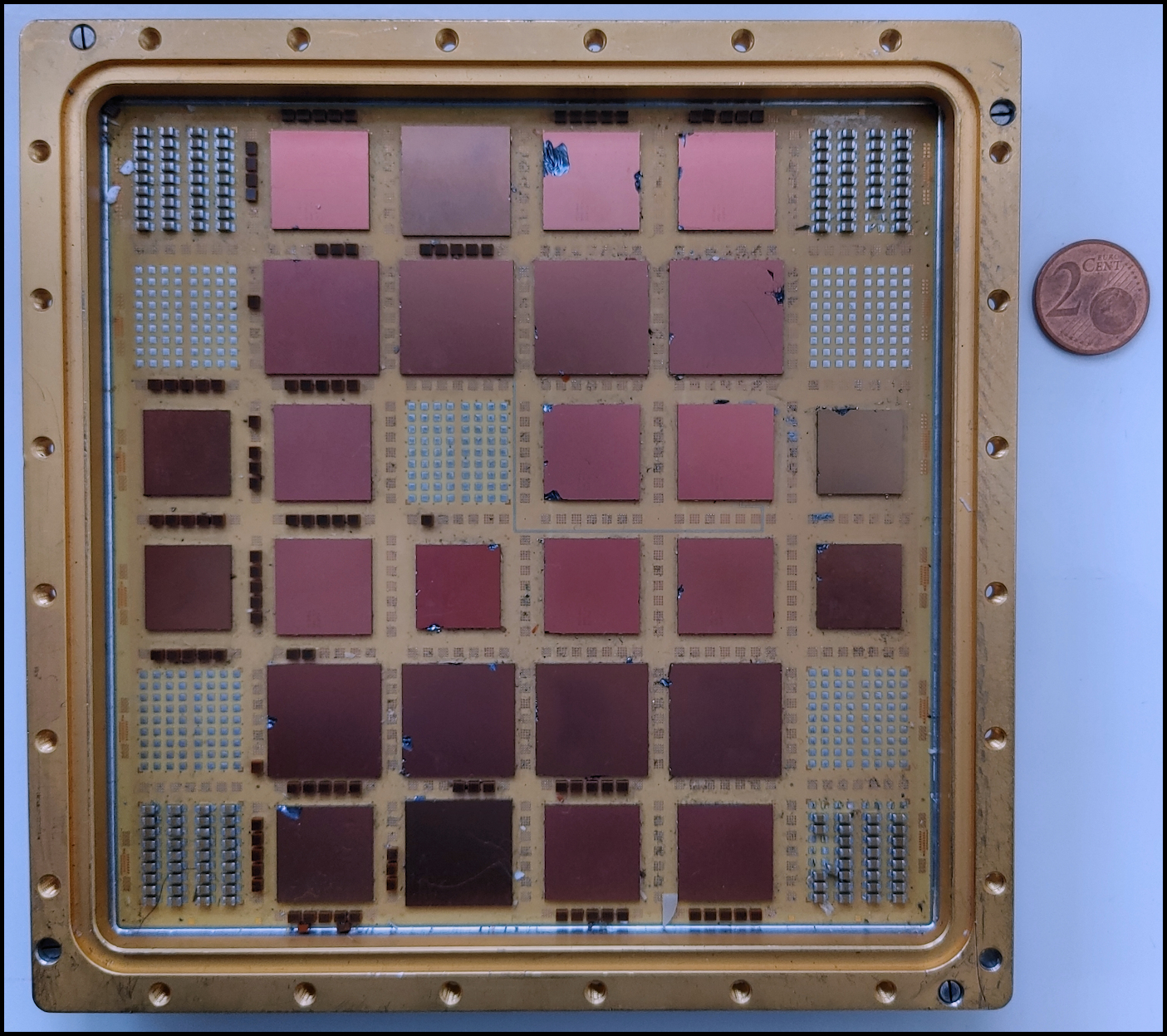

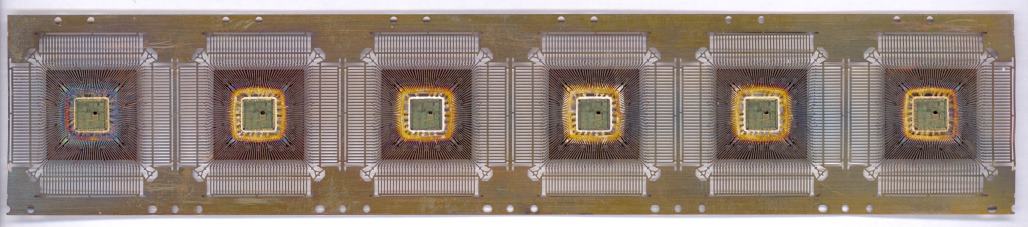

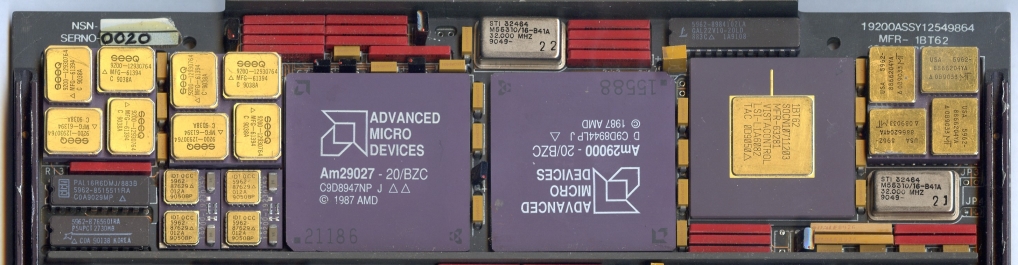

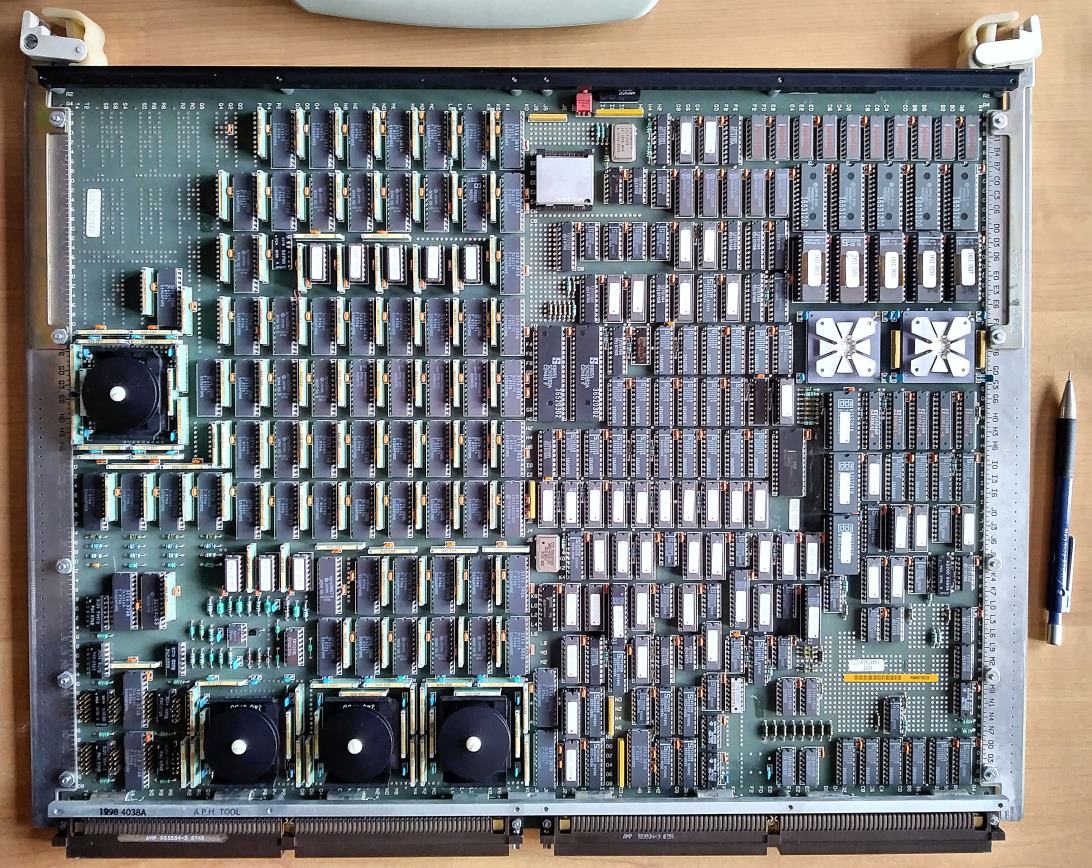

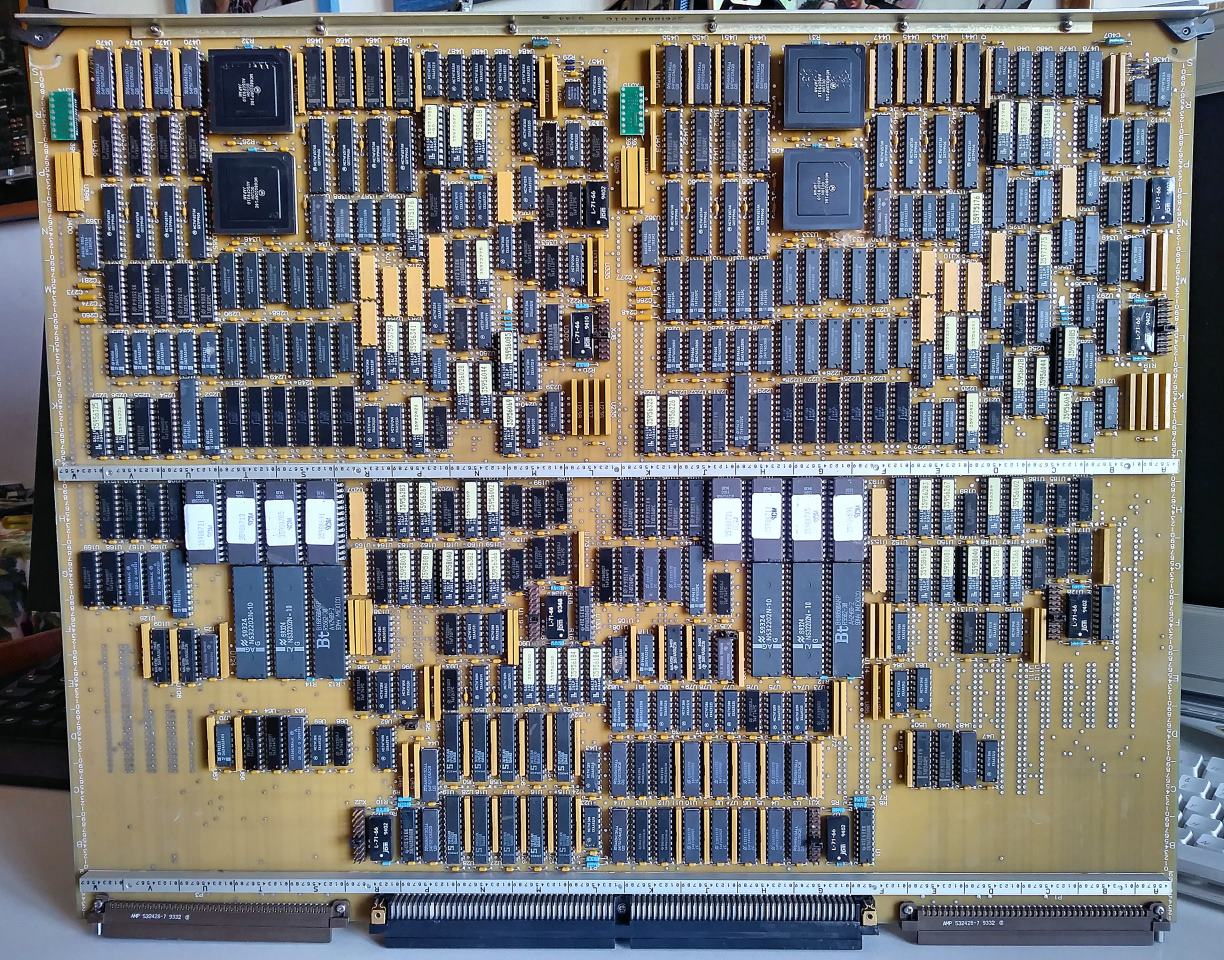

Modulo della CPU di un mainframe Amdahl 470/V6 (1977). Il 470/V6, commercializzato a partire dal 1975, era un mainframe per applicazioni commerciali concepito per fare concorrenza ai sistemi IBM sfruttando una tecnologia più avanzata rispetto ad essi, sviluppata ed implementata da Fujitsu (infatti questi moduli circuitali sono stati utilizzati anche nel FACOM M-190 della stessa Fujitsu). Caratteristica del 470/V6 era quella di essere realizzato interamente con componenti LSI, in particolare gate array ECL Fujitsu MB11K che consentivano densità e velocità operative superiori a quelle del Sistema/370 di IBM (basato su tecnologia MST solo in parte a larga scala d'integrazione). Gli integrati che compongono la CPU del 470/V6 sono organizzati in particolari moduli circuitali detti Multi-Chip Carrier Board (MCC-B). Non si tratta in effetti di veri e propri moduli multichip nel senso comune bensì di schede a circuito stampato multistrato e connessioni punto-punto (vedi qui sotto) su ciascuna delle quali sono montati 42 integrati MB11K con la tecnica del montaggio superficiale. Ogni integrato è dotato di un proprio caratteristico dissipatore di calore che permette il raffreddamento ad aria forzata nonostante la produzione di calore sia superiore a quella di altri mainframe dell'epoca. Il circuito stampato dei moduli MCC è formato da 14 strati sovrapposti (4 di alimentazione e 10 di segnale). L'interconnessione tra i vari moduli avviene mediante appositi connettori, 8 per ogni modulo, ai quali sono collegati cavi micro-coassiali che trasportano i segnali da un modulo all'altro. Nella CPU infatti non viene impiegato un backplane nel vero senso della parola. All'interno della CPU i moduli sono organizzati in colonne che ne ospitano 2 o 3 su ciascun lato, come si può vedere qui: https://www.flickr.com/photos/44124348109@N01/5109451656. Qui è invece visibile un gate array MB11K, aperto, inserito in un fermacarte pubblicitario Amdahl. L'effetto visivo dello schieramento di 42 dissipatori di calore dorati è indubbiamente notevole ed infatti i moduli MCC, al di là della loro importanza per la storia dell'informatica, sono oggetti da collezione molto ricercati dai collezionisti di vecchie CPU.

Retro del modulo MCC raffigurato sopra, che mostra il gran numero di connessioni discrete punto-punto che si aggiungono a quelle nel circuito stampato.

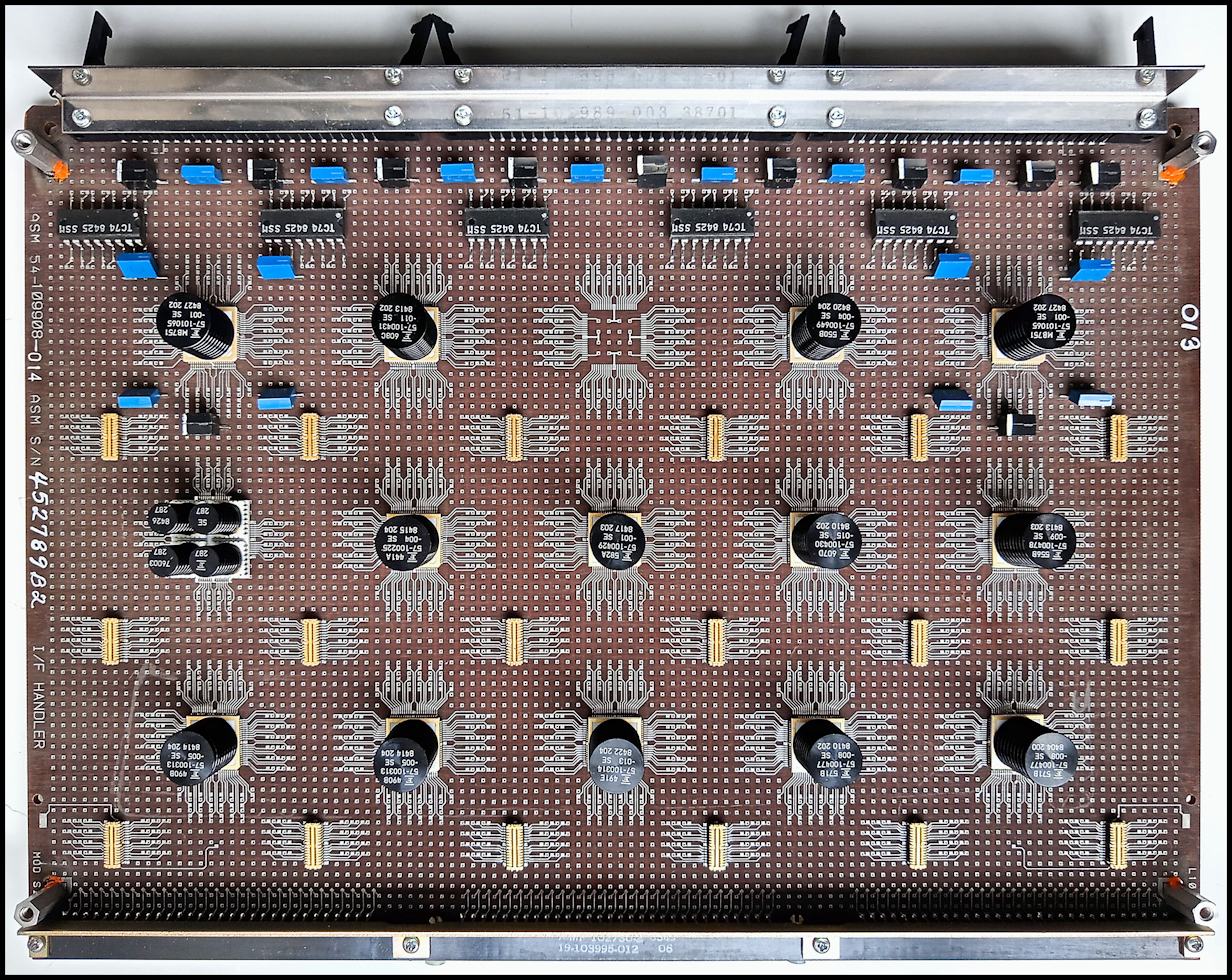

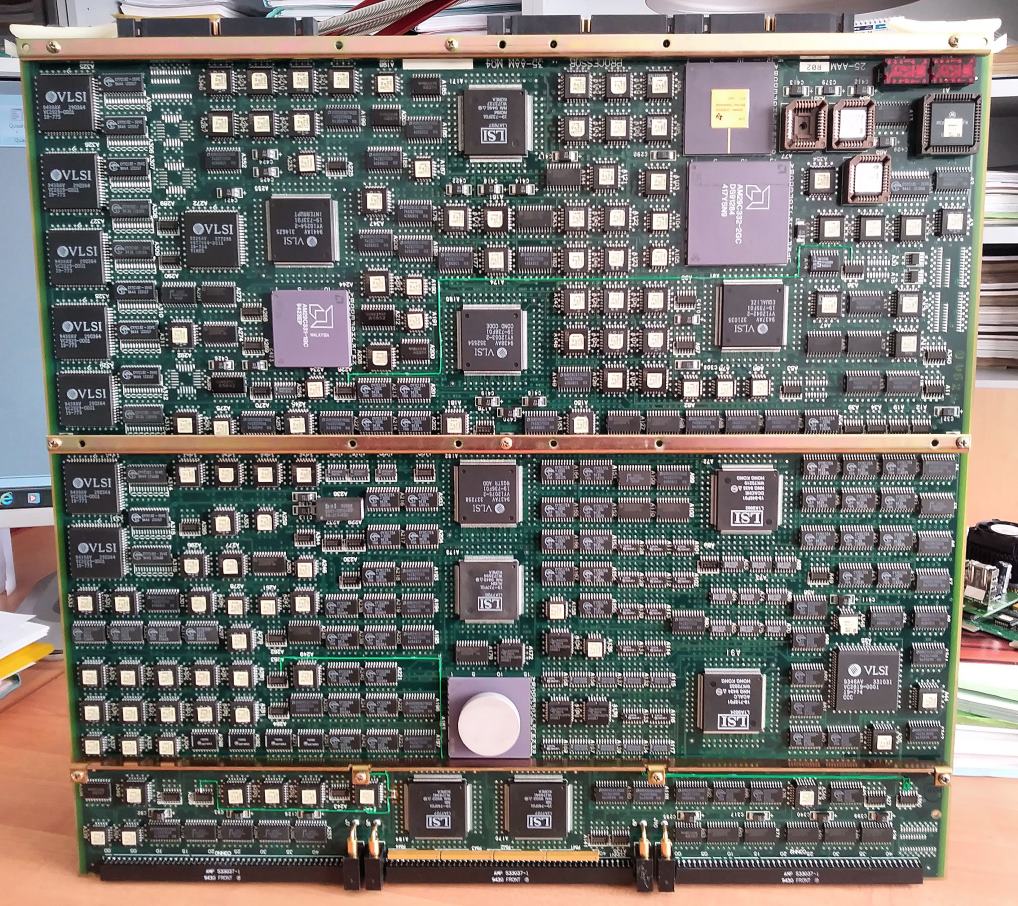

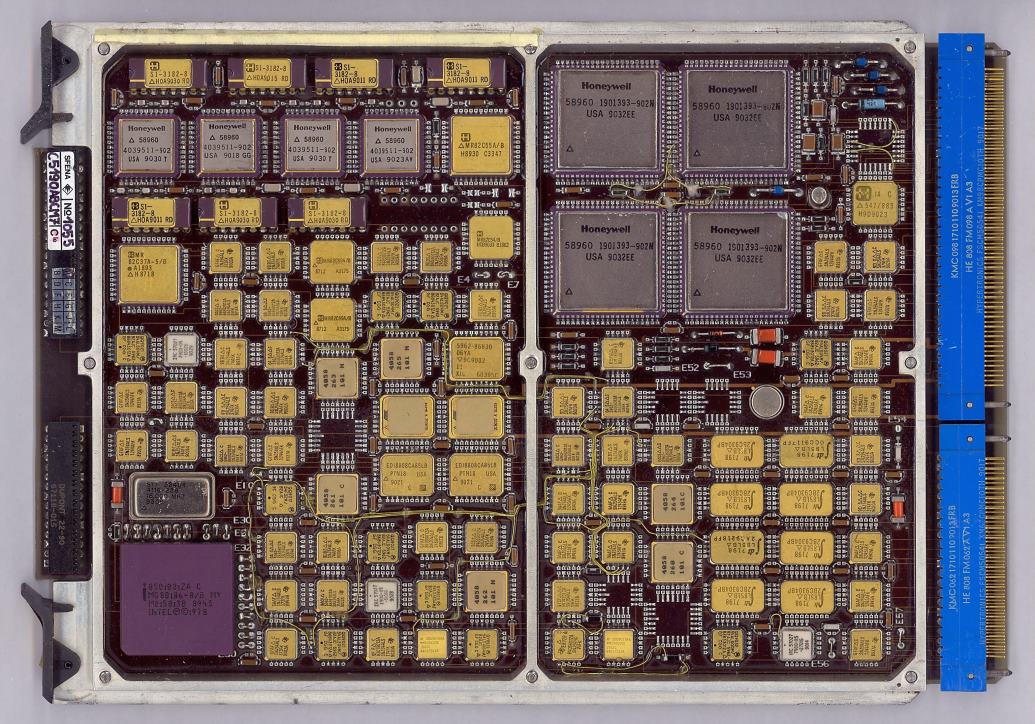

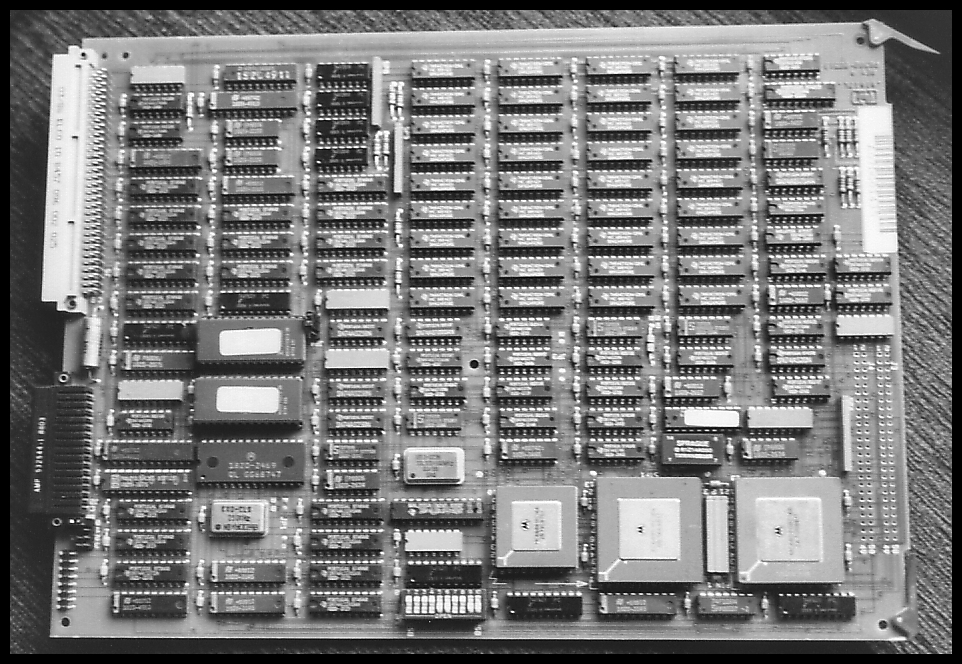

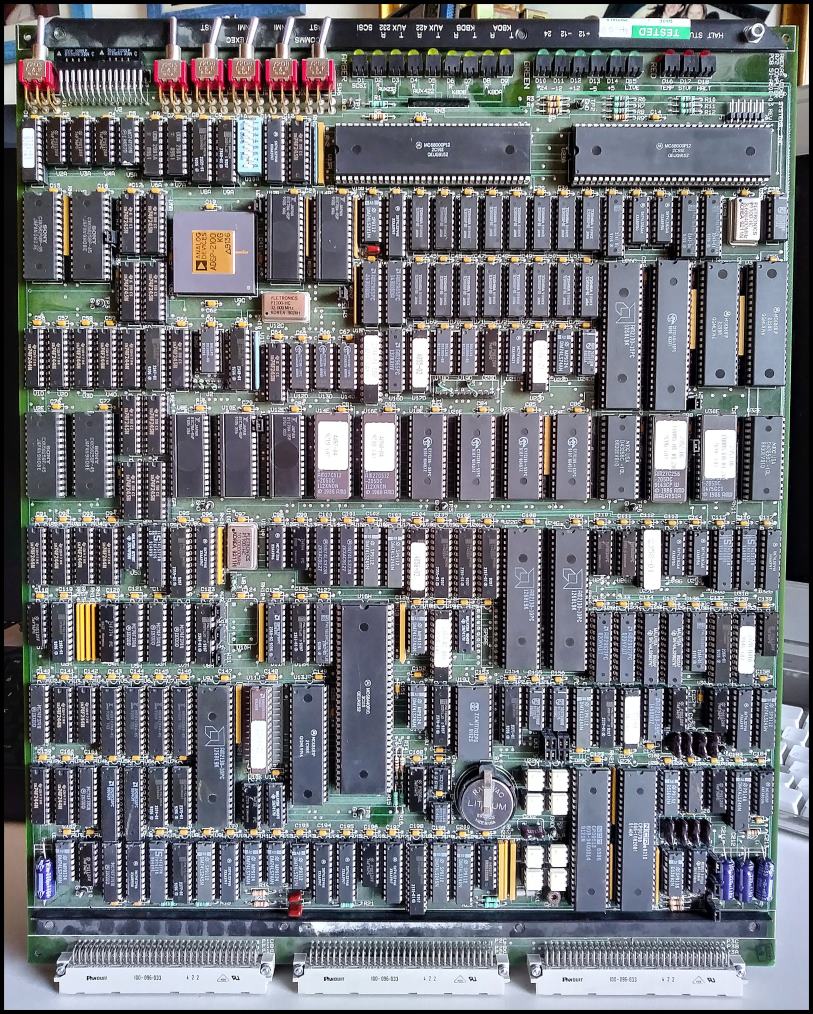

Scheda di mainframe Amdahl 5860 (1984), macchina uniprocessore appartenente alla famiglia 580, con gate array ECL Fujitsu ed un modulo SRAM (il componente a sinistra nella foto con 4 distinti dissipatori di calore). Si nota che tutti i componenti sono a montaggio superficiale. Anche in questi calcolatori, come nella precedente serie 470, le schede che formano la CPU sono realizzate con circuito stampato multistrato e connessioni punto a punto sul retro. Come le schede della serie 470 erano chiamate da Amdahl "Multi Chip Carrier" (MCC), evidenziando il fatto che si trattava di una tecnologia avanzata ed intermedia tra una "semplice" scheda a circuito stampato ed un modulo multichip vero e proprio. La Amdahl puntava molto, dal punto di vista commerciale, sulla superiorità tecnologica rispetto ai prodotti IBM. Quest'ultima all'epoca offriva, nella stessa fascia medio-alta dove si posizionavano le macchine Amdahl, la serie 4300 che era basata su integrati MST a minore densità. La somiglianza di questa scheda con i moduli IBM MST è solo apparente (il reticolo di punti di interconnessione nel circuito stampato) in quanto l'IBM, a differenza della Amdahl, non faceva uso nelle proprie macchine di componenti a montaggio superficiale.

Retro della scheda raffigurata sopra, protetto da una copertura in plastica trasparente.

Fermacarte Amdahl con engineering sample di gate array ECL Fujitsu del tipo impiegato nei mainframe della serie 580 (1984/5).

Fermacarte con gate array del tipo usato nel mainframe Amdahl 470 V6.

Spilletta con chip Fujitsu/Amdahl (circa 1986).

Modulo logico di calcolatore CDC 7600, circa 1969. Il 7600 è stato l'ultimo ed il più avanzato supercomputer a transistor, prima dell'avvento delle macchine di terza generazione a circuiti integrati. Come il predecessore 6600 è stato progettato da Seymour Cray ed è l'ultima macchina concepita da quest'ultimo prima della fondazione della Cray Corporation. L'obiettivo progettuale del 7600 era di ottenere un miglioramento di 10 volte delle prestazioni rispetto al 6600 ed è stato ottenuto con una serie di accorgimenti e soluzioni, sia a livello di componentistica (utilizzo di transistor al silicio con elevate velocità di commutazione, impacchettamento dei moduli per minimizzare la lunghezza delle interconnessioni ed i relativi tempi di latenza) che di architettura (organizzazione del processore, pipelining, numero di unità operanti in parallelo) che hanno rappresentato nel complesso una pietra miliare dello sviluppo dei calcolatori elettronici. Alcune di esse sono tuttora implementate nei moderni processori RISC. La CPU del CDC 7600 funzionava a 36,5 MHz con un ciclo di clock di 27,5 ns, valori di assoluto livello per l'epoca (fine anni Sessanta). La velocità di elaborazione raggiungeva i 10 MFLOPS, con picchi di ben 36 MFLOPS, che rendevano la macchina più veloce del diretto concorrente IBM 360/195 che a sua volta deve essere considerato un ibrido tra seconda e terza generazione in quanto già faceva utilizzo di alcuni moduli a circuiti integrati. Da un punto di vista dell'architettura di sistema il CDC 7600 era una macchina RISC con istruzioni a 16 bit; tutte le operazioni in virgola mobile venivano eseguite da apposite unità ausiliarie, concettualmente paragonabili alle FPU dei moderni processori. L'impiego del clock a 36 MHz comportava un'elevata produzione di calore, nonostante l'utilizzo di transistor di ridotte dimensioni; per questo motivo, i moduli (del tipo di quello qui visibile) erano formati da pacchetti di 6 schede sovrapposte ed interconnesse con tecnica "cordwood", a loro volta racchiuse in contenitori in lega di alluminio che servivano per il raffreddamento a Freon (caratteristico anche delle prime macchine Cray). Come la gran parte dei calcolatori di seconda generazione, anche il CDC 7600, per quanto avanzato, faceva uso di nuclei magnetici sia nelle memorie principali (più lente) che nella cache e nei vari buffer (più piccoli e veloci).

Vedi: https://en.wikipedia.org/wiki/CDC_7600, https://people.computing.clemson.edu/~mark/cdc7600.html

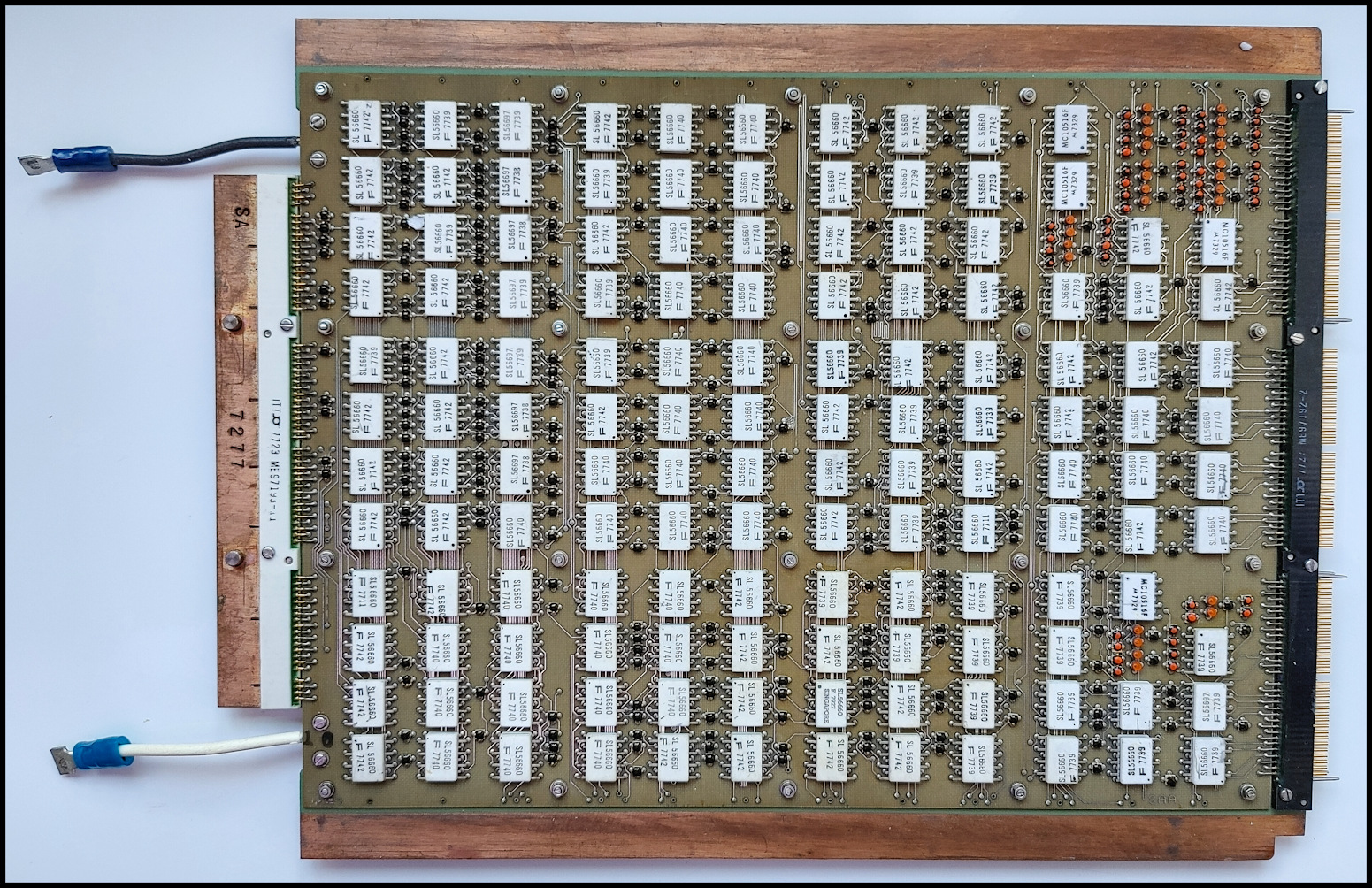

Scheda della CPU di un supercomputer Cray 1, 1977, popolata da logica ECL Fairchild a basso livello di integrazione.

Scheda di memoria proveniente da un Cray 1/S (1981).

Gate array CMOS (10.000 porte logiche equivalenti, 4,2 ns) utilizzato nella CPU del supercomputer Cray Y-MP C90 (1990).

Vedi: https://en.wikipedia.org/wiki/Cray_C90, http://www.chipsetc.com/cray-research.html.

Fermacarte pubblicitario con engineering sample di gate array ECL VLSI da 2.500 porte logiche NAND-equivalenti del tipo usato nel supercomputer Cray Y-MP (1988).

Vedi: https://en.wikipedia.org/wiki/Cray_Y-MP.

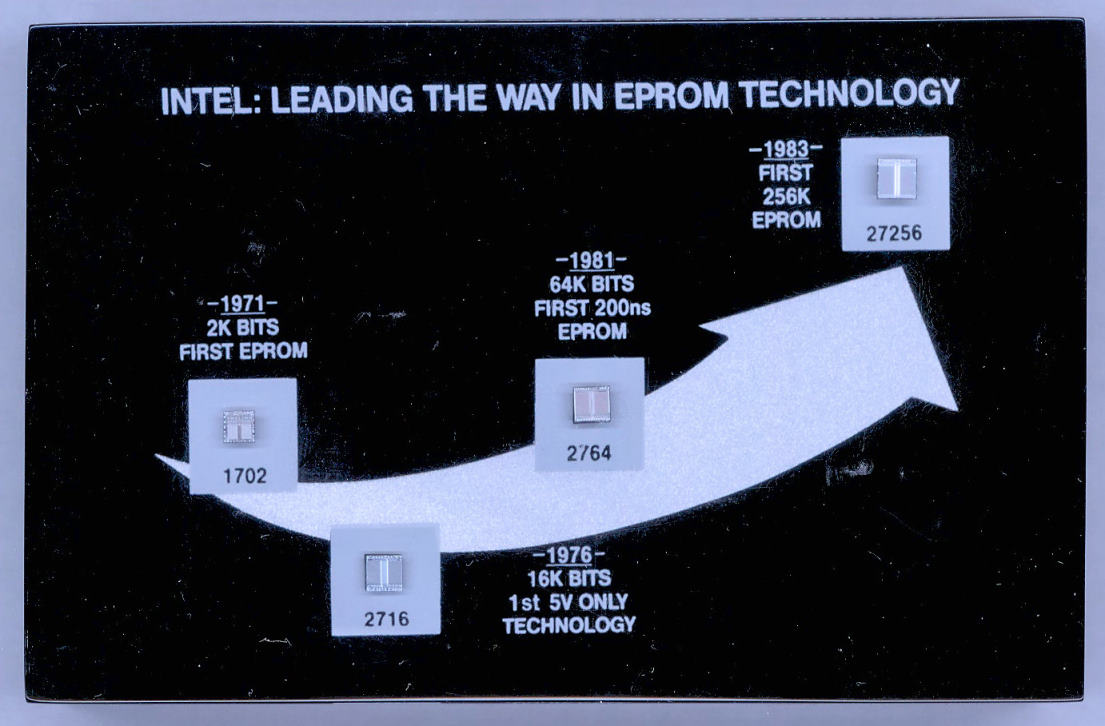

Fermacarte pubblicitario (1984) che mostra l'evoluzione delle EPROM Intel a partire dal primo modello commerciale del 1971, la 1702 da 2 kbit.

Modulo multichip della CPU di un mainframe Hitachi F7/MP5600 (1996).

"Hitachi announced the MP5800 processor as the successor to the M-88 in April 1995 and began shipping models in October 1995. Hitachi developed a new super-fast, highly integrated, low-power LSI topology called advanced CMOS-ECL (ACE), which united high-speed bipolar ECL and highly integrated CMOS circuitry. From this development, Hitachi built logic LSIs with 120,000 gates and 40 ps latency and internal logic RAM LSIs as large as 2.3 megabits with access times of 1 ns. By placing these circuits in high-density modules, Hitachi created the instruction processor in a module one-tenth the size of that on the M-880. This integration doubled the processing power of the previous model and allowed the new models to accept up to eight processors. [...] Hitachi announced the MP5600 processor as the successor to the M-860 in April 1996 and began shipping models in September 1996. With about double the performance of the M-860 and a multiprocessor architecture that could be expanded to as many as eight processors, the MP5600 processor series consisted of 12 models covering a range of about 18 times in performance capability. CMOS LSI technology was used exclusively, and CMOS LSI chips with up to 600,000 gates were used for main memory, extended memory, and I/O processors. The MP5600 processors were one-box systems that took up to 85 percent less space and used up to 90 percent less energy than the M-860. By adding the H-6710 high-speed coupling device, scalable systems could be created that supported parallel processing functions between as many as 32 central processing nodes (a CPU formed from multiple tightly-coupled processors).” (https://museum.ipsj.or.jp/en/computer/main/0093.html)

“The high-end models, the M-280H and M-260H, were based on technology developed for the M-200H, and they achieved higher levels of performance and functionality by using newly developed technology, such as world leading logic-in-memory, 4Kbit/7ns high-speed bipolar memory, 550/1500gate LSI and platters which increased the degree of integration to 18 levels. Due to their outstanding cost-performance, these models were exported in large numbers to Europe and the US, where they enjoyed an outstanding reputation. For scientific and engineering calculations, the M-280H was equipped with high-speed arithmetic mechanisms and a built-in array processor. […]The M-220X models, successors to the M-220H, were developed as computer systems to provide integrated office automation systems for the new media age. The four models — M-220DX, M-220HX, M-220KX, and M-220LX — were field upgradeable to more powerful machines at the installation site. This family offered improved reliability, a smaller footprint, and less power consumption due to the extensive use of LSI chips, including high-speed 1,500-gate LSI chips for the main logic circuits, CMOS gate-array LSI chips with 24,000-gates per chip that provided the peripheral control circuits with much faster speeds and dramatically less power consumption, and 256-kilobit DRAM chips for the main working memory. Space was also saved because a dedicated console was not needed.” (https://museum.ipsj.or.jp/en/computer/main/0054.html)

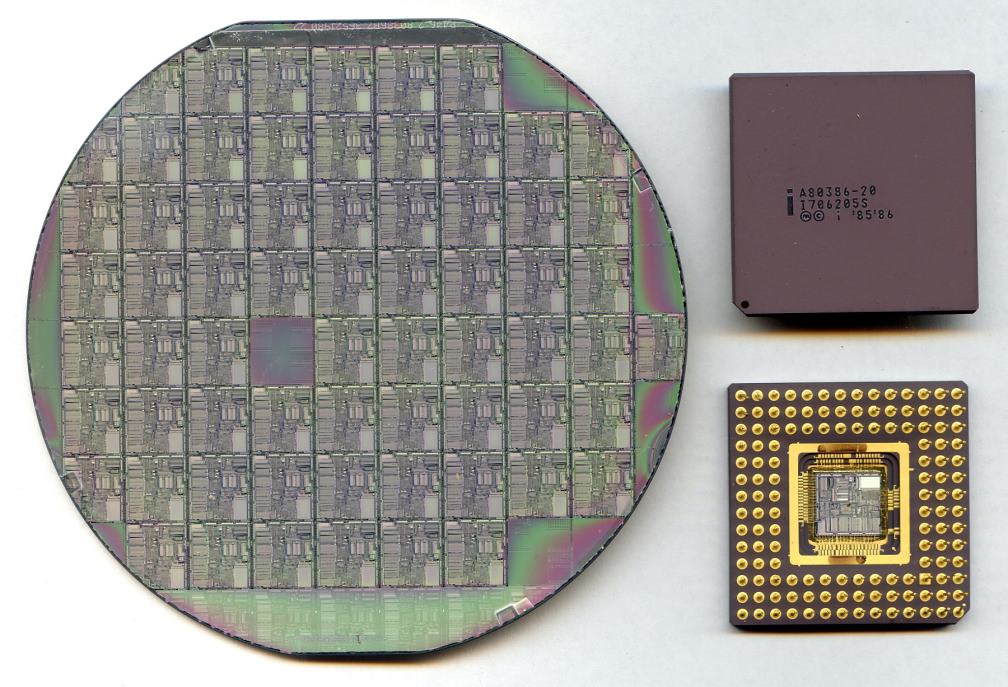

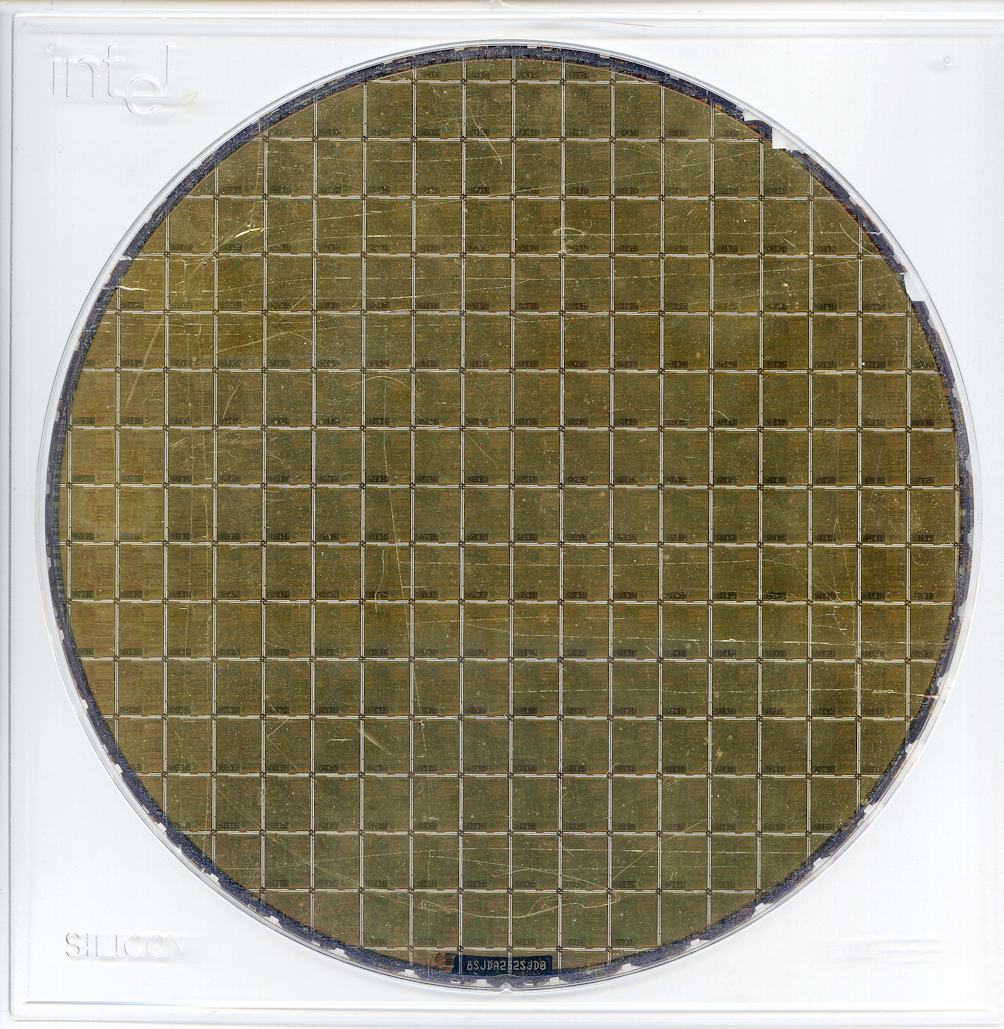

12.10.2015 - Wafer da 4 pollici del 1986 con CPU Intel 80386 a 20 MHz e, a destra, due processori sempre a 20 MHz assemblati, di cui uno con il "lid" (copertura del chip) rimosso e nessuna sigla sul package (presumibilmente un ES, Engineering Sample). Il tutto proviene dalla collezione di un ex dipendente IBM. La seconda riga della sigla, detta "FPO number", indica in sequenza il Paese di provenienza (in questo caso la I identifica un impianto di produzione Intel in Malesia, vedi), l'anno di produzione del quale è riportata l'ultima cifra (7 = 1987), la settimana (06, Febbraio) e l'identificazione del lotto al quale il pezzo appartiene. La lettera "A" prefissa alla sigla 80386 indica un componente in package PGA. Un oggetto simile è visibile qui: http://www.computerhistory.org/collections/catalog/102711298. Il wafer riprodotto qui è siglato "P446-2 80386BZ 36521980 22". Intel fabbricò inizialmente le CPU 386 su wafer da 4 pollici in quanto questi ultimi garantivano una più alta resa produttiva rispetto a quelli da 6 pollici, maggiormente affetti da imperfezioni. Il processore 80386 è storicamente importante per una serie di ragioni: 1) è stato la prima CPU a 32 bit ad essere prodotta e venduta in quantità dalla Intel (il precedente progetto iAPX432 non ha avuto una vera e propria diffusione commerciale); 2) è stato la prima CPU prodotta da Intel in single-sourcing, contribuendo così in modo fondamentale alle fortune dell'Intel stessa, nonché uno dei primi processori avanzati ad essere fabbricati secondo questa filosofia; 3) è stato la CPU del primo PC a 32 bit, il Compaq 386 PC. Le CPU dell'immagine potrebbero far parte di un lotto affetto dal bug della moltiplicazione a 32 bit (vedi: https://www.cs.earlham.edu/~dusko/cs63/prepentium.html). Come abbiamo detto, Compaq è stata il primo produttore a sviluppare e commercializzare un personal computer con processore Intel a 32 bit, introducendo così la prima grande innovazione tecnologica nel mondo PC dopo l'epoca dei 16 bit. E' significativo in particolare che questo avanzamento sia venuto da un fabbricante "terzo" rispetto ad IBM, il che ha di fatto legittimato l'industria dei cloni e nel contempo ridotto l'importanza dell'IBM stessa nel settore dei personal computer. IBM scelse di non introdurre subito, cioè nel 1985, un PC con CPU 386 in quanto era titolare del diritto di fabbricare nei propri impianti (sia pure con maschere Intel) i processori 80286 e desiderava quindi sfruttare per qualche anno ancora questa possibilità, ritenendo fra l'altro che un processore a 32 bit fosse sovradimensionato rispetto alle esigenze dell'utente medio dell'epoca e del software, ancora in massima parte a 16 bit. Il primo personal IBM con CPU 386 è stato invece il PS/2 Modello 80. Intel decise di fabbricare in esclusiva i processori 386, tuttavia concesse alla IBM -cui era legata da importanti accordi di collaborazione- di assemblare i chip in package proprietari.

Copertina della rivista PC Tech Journal, Febbraio 1987, dedicata alla CPU 80386. Il "PC Tech Journal" (vedi) era una pubblicazione (prima bimestrale, poi mensile) derivata dalla più nota rivista PC Magazine, con un taglio più tecnico e dedicata principalmente a sistemisti e programmatori. E' stata pubblicata dal Luglio 1983 all'Aprile 1989.

Vedi: http://www.os2museum.com/wp/pc-tech-journal/.

Numero del Dr. Dobb's Journal dedicato allo stesso argomento (Ottobre 1986).

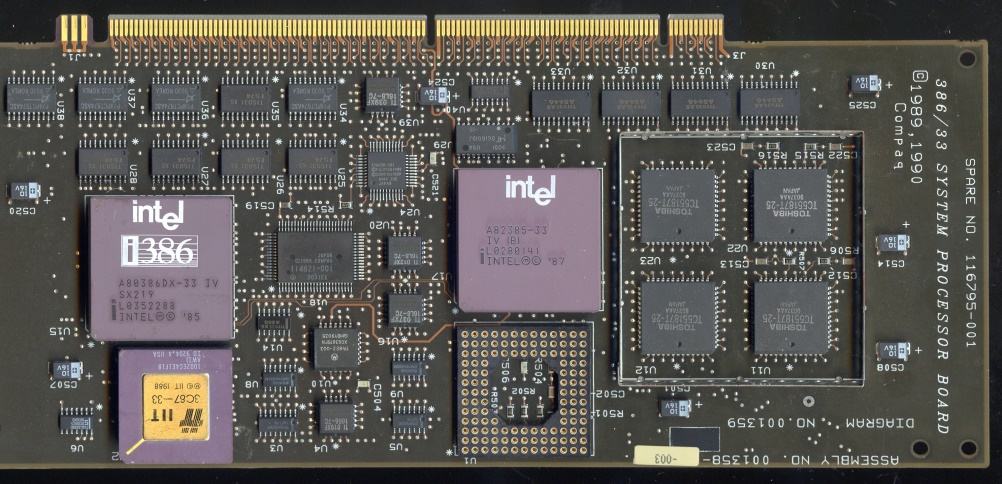

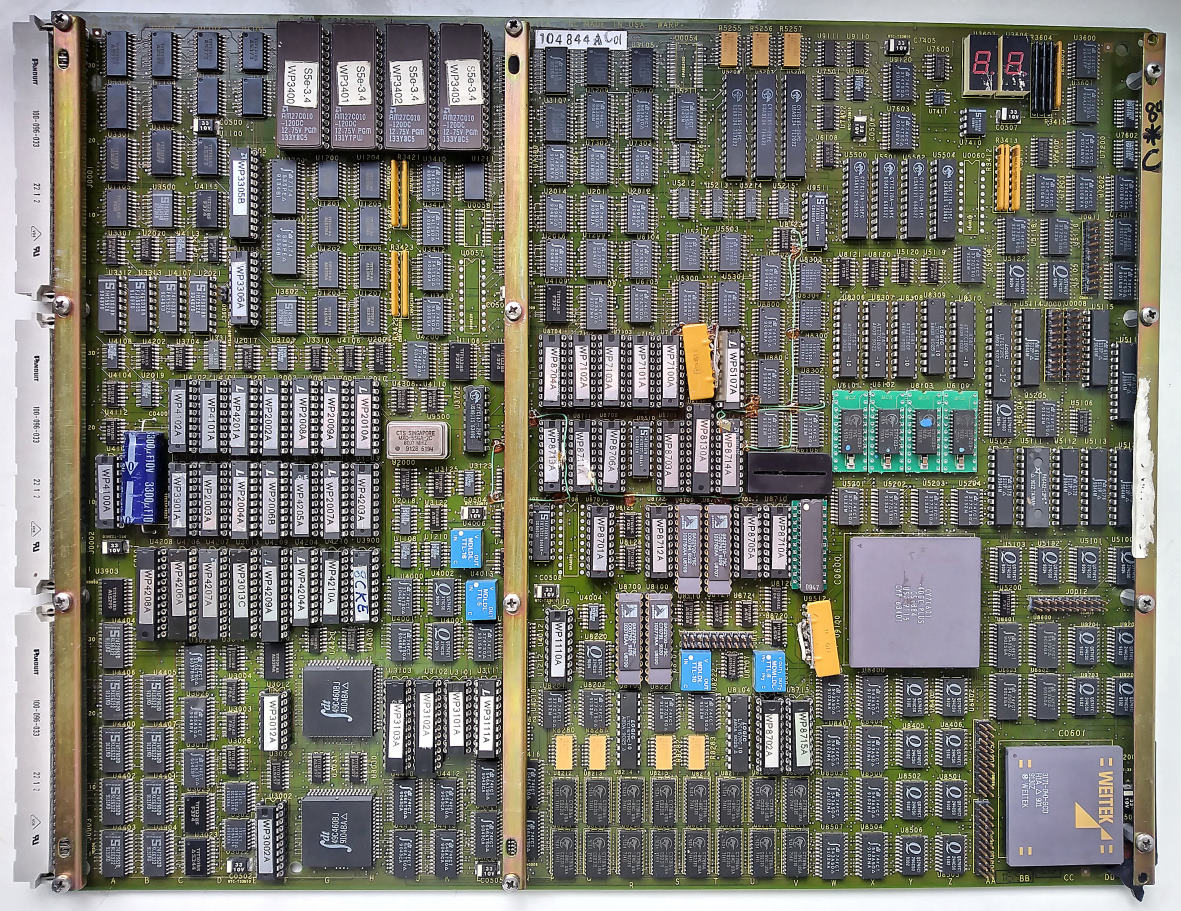

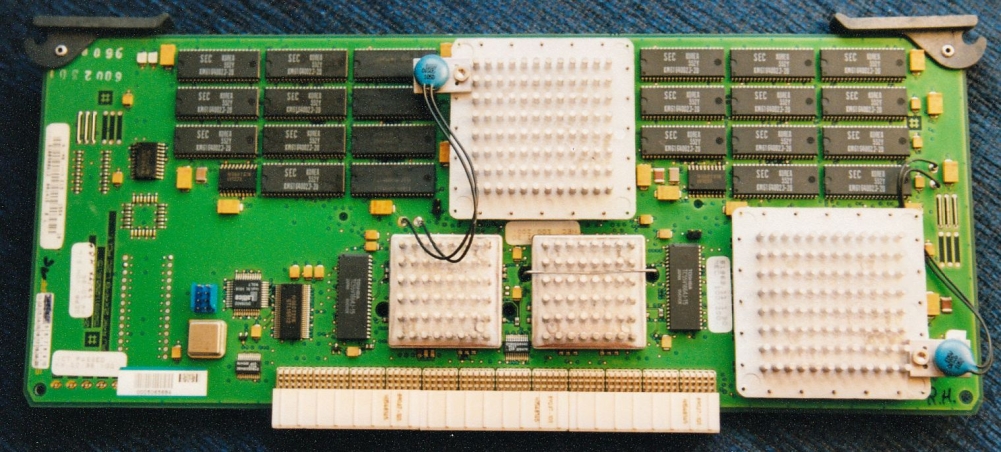

6.5.2015 - Scheda CPU per Compaq Deskpro 386/33M con processore Intel 386DX a 33 MHz, cache controller 82385-33, 64 KB di cache write-through (a destra, 4 chip di SRAM Toshiba) e FPU -anche nota come "coprocessore matematico"- IIT 3C87-33. In basso al centro lo zoccolo, vuoto, per la FPU Weitek (es. 1167, che poteva essere installata congiuntamente al 387). I 386 marchiati con la sigla aggiuntiva "IV" erano fabbricati da Intel con processo CMOS-IV, un miglioramento del precedente CMOS-III. La FPU IIT 3C87 venne introdotta nel 1989, più o meno assieme alla concorrente Cyrix 83D87. Al pari di quest'ultima era più veloce del corrispondente coprocessore Intel 80387DX funzionante alla stessa frequenza e, in più, offriva funzioni specifiche non implementate nella FPU Intel. Alcune di queste, in particolare quella di moltiplicazione diretta di una matrice 4x4 per un vettore 4x1, erano particolarmente utili ai programmi di CAD che potevano trarre da esse benefici in termini di velocità di esecuzione. La 3C87 era fabbricata con processo CMOS a 1,20 micron ed assorbiva solamente 600 mW. A differenza dell'Intel 80387 essa, come d'altra parte le FPU Cyrix, Chips & Technology ed ULSI, non poteva funzionare in modalità asincrona ma solamente alla medesima frequenza della CPU. E' stata commercializzata nelle versioni a 16, 20, 25, 33 e 40 MHz. La serie "Deskpro M" di Compaq era una famiglia di macchine x86 particolarmente avanzata per l'epoca in cui venne introdotta; era realizzata con gli obiettivi primari della modularità (sia il processore che la RAM erano contenuti in schede separate dalla motherboard) e dell'espandibilità: la medesima scheda madre poteva accogliere CPU 386DX e 486DX, a seconda del modello di macchina e della fascia di prezzo. I Deskpro M sono stati tra i primi sistemi EISA di successo, nonostante il costo mediamente elevato. Queste macchine facevano largo uso di ASIC VLSI per minimizzare il numero di componenti necessari. I modelli di fascia alta venivano spesso impiegati come server per reti Novell Netware.

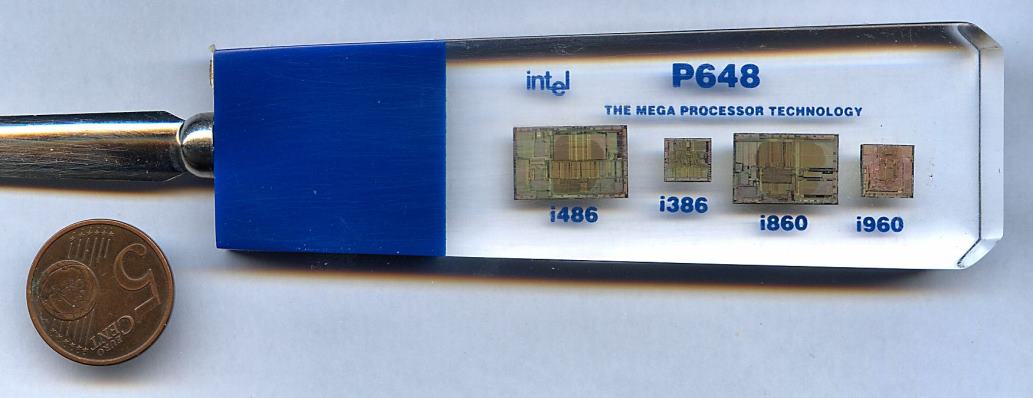

Dettaglio di un tagliacarte promozionale Intel contenente 4 diversi chip. Proviene dall' Intel Development Centre di Haifa (Israele).

Scheda CPU di server Siemens Nixdorf Primergy 350 (1993) con processore Pentium P54 a 60 MHz.

Pubblicazione Intel di grande formato commemorativa dei 25 anni dalla commercializzazione del primo microprocessore, il 4004 (1996).

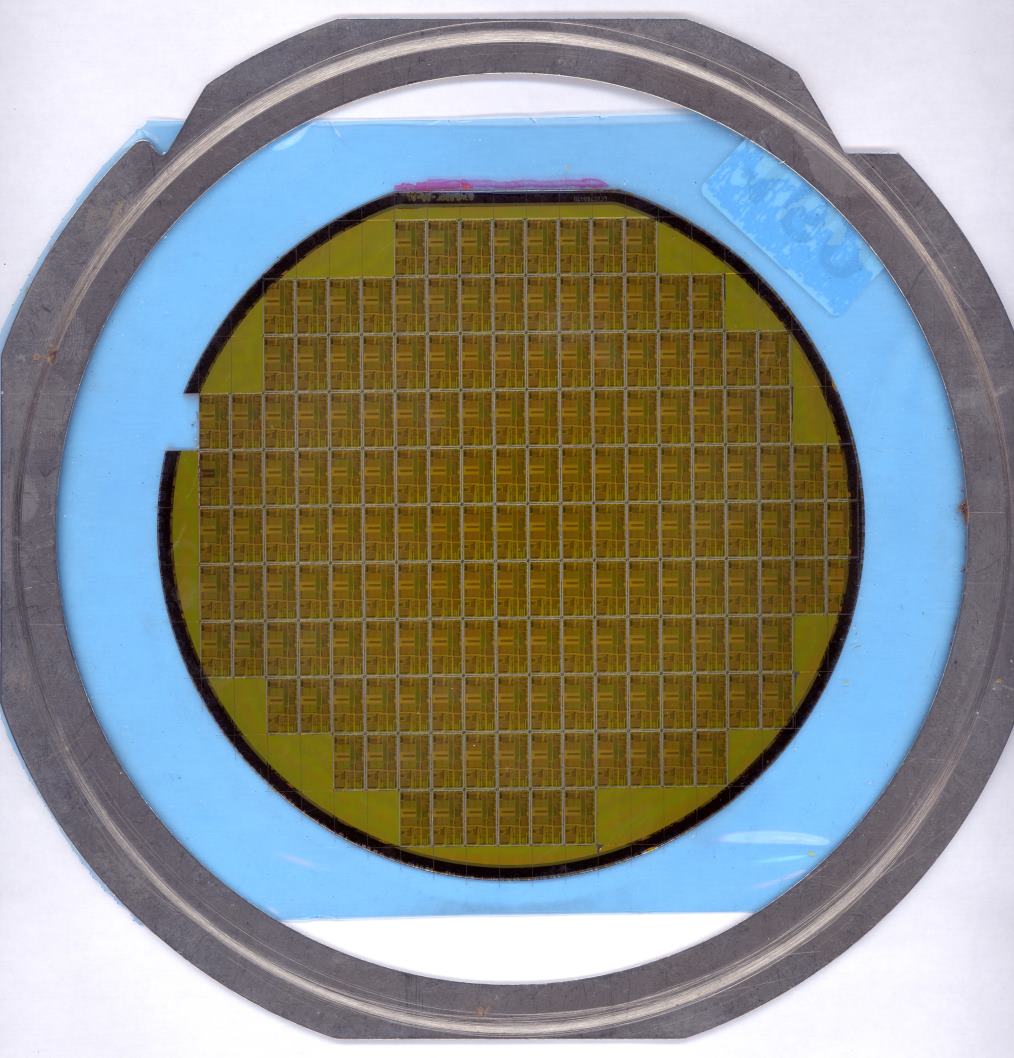

Wafer di CPU Intel 80486DX/2 "blue taped", cioè collocato su un fondo plastico adesivo di colore azzurro per la separazione dei singoli chip. In questo caso il taglio è già avvenuto. Il wafer proviene da una "fab" israeliana (Haifa, probabilmente).

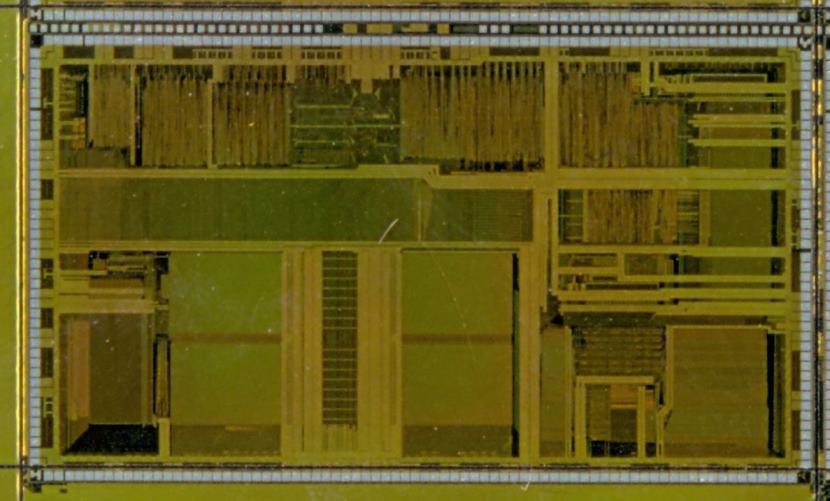

Dettaglio di un chip 486DX/2 proveniente dal wafer di cui sopra (scansione a 2.400 dpi).

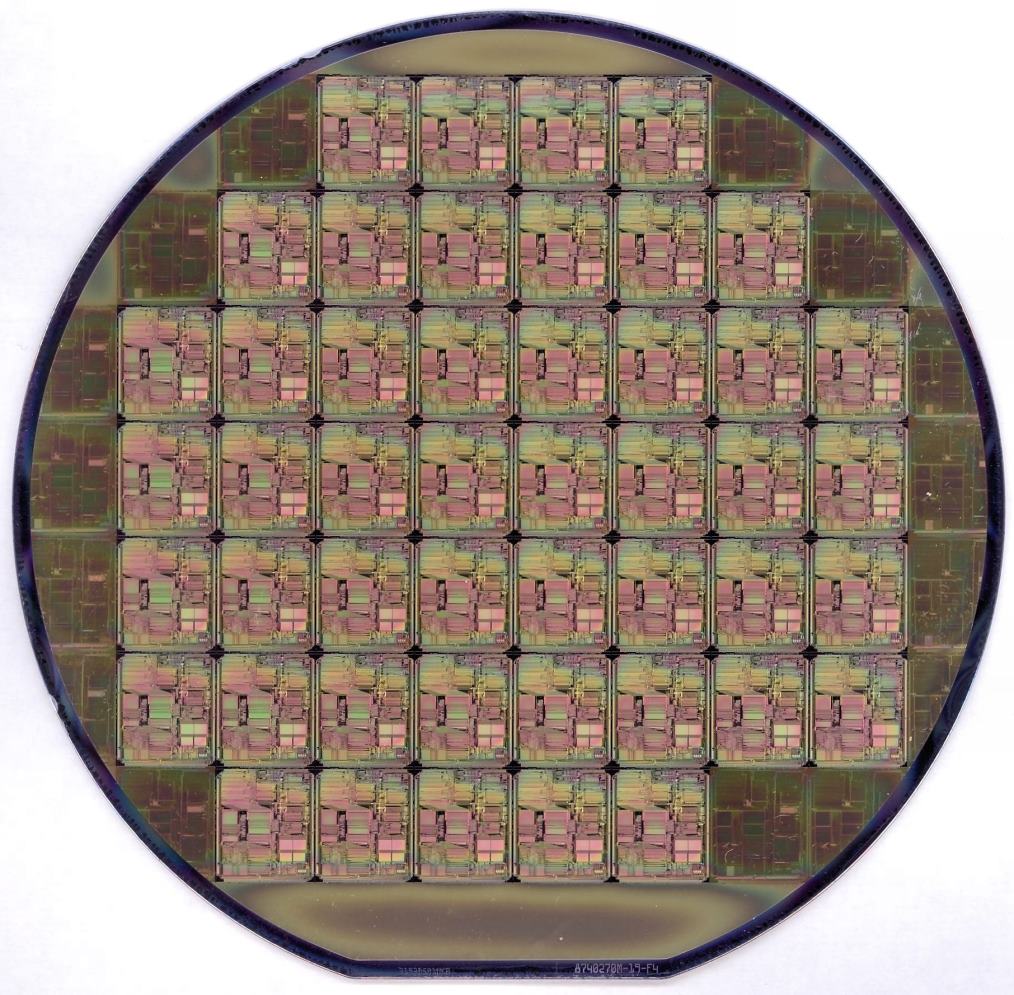

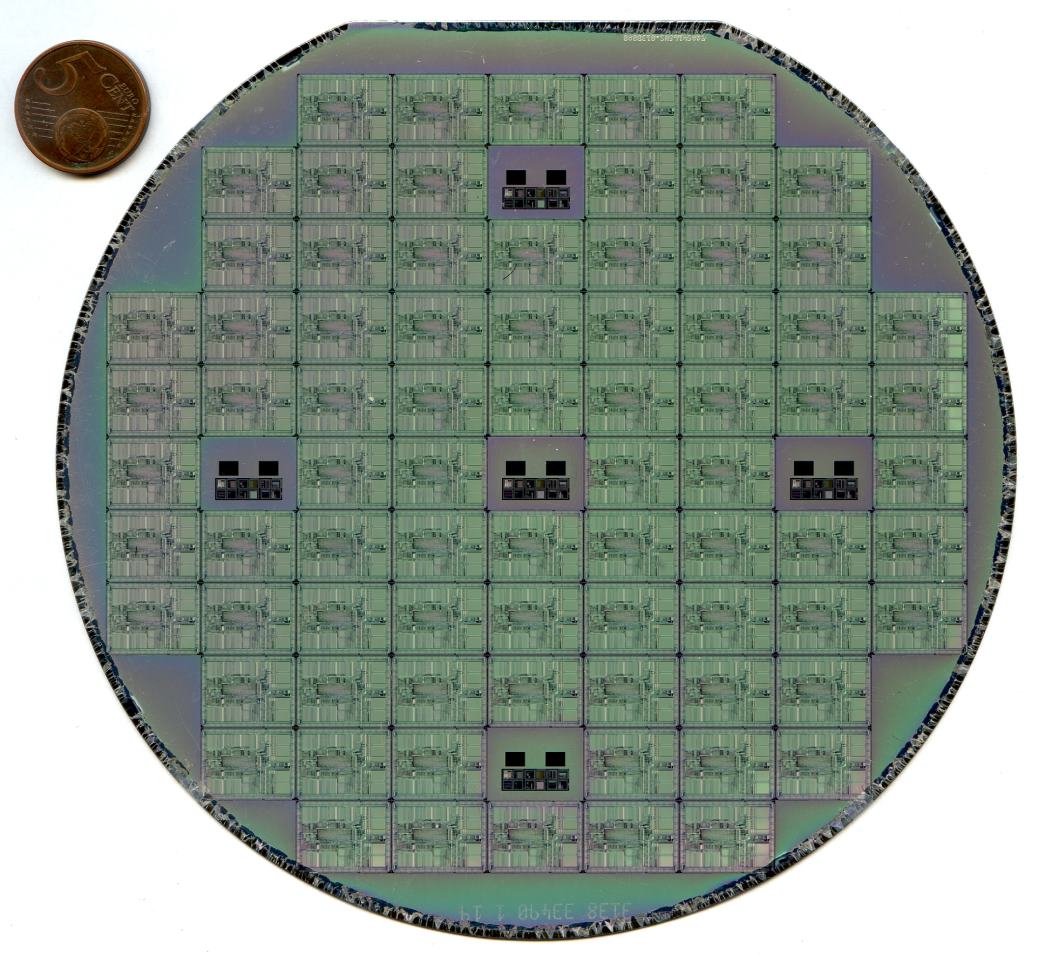

Wafer completo di CPU Intel i960MX, versione originale del processore 80960 prodotta soltanto per impieghi militari/aerospaziali con specifiche ambientali estese. La sua controparte commerciale, architetturalmente equivalente ma con molte funzioni non documentate nella manualistica ufficiale e diversi pin non connessi, è l'i960MC. Le versioni MX ed MC sono considerate le uniche ad aver implementato completamente, in tutti gli aspetti architetturali, l'originario progetto di processore BiiN dal quale è nato l'i960. Sono entrambe caratterizzate da elevate dimensioni del die rispetto a quelle dei processori 960 più comuni. La differenza di dimensioni è ben visibile confrontando questa foto con la precedente, tenuto conto che la scala è la medesima.

In 1984, Intel and Siemens started a joint project, ultimately called BiiN, to create a high-end, fault-tolerant, object-oriented computer system programmed entirely in Ada. Many of the original i432 team members joined this project, though a new lead architect, Glenford Myers, was brought in from IBM. The intended market for the BiiN systems were high-reliability computer users such as banks, industrial systems, and nuclear power plants. Intel's major contribution to the BiiN system was a new processor design, influenced by the protected-memory concepts from the i432. The new design was to include a number of features to improve performance and avoid problems that had led to the downfall of the i432. The first 960 processors (i960MX/MC) entered the final stages of design, known as taping-out, in October 1985 and were sent to manufacturing that month, with the first working chips arriving in late 1985 and early 1986. The BiiN effort eventually failed, due to market forces, and the 960MX was left without a use. Myers attempted to save the design by outlining several subsets of the full capability architecture created for the BiiN system. He tried to convince Intel management to market the i960 (then still known as the "P7") as a general-purpose processor, both in place of the Intel 80286 and i386 (which taped-out the same month as the first i960), as well as the emerging RISC market for Unix systems, including a pitch to Steve Jobs for use in the NeXT system. Competition within and outside of Intel came not only from the i386 camp but also from the i860 processor, yet another RISC processor design emerging within Intel at the time. Myers was unsuccessful at convincing Intel management to support the i960 as a general-purpose or Unix processor, but the chip found a ready market in early high-performance 32-bit embedded systems. The lead architect of i960 was superscalarity specialist Fred Pollack who was also the lead engineer of Intel iAPX 432 and the lead architect of the i686 chip Pentium Pro. […] To avoid the performance issues that plagued the i432, the central i960 instruction-set architecture was a RISC design, which was only implemented in full in the i960MX. […] The "full" i960MX was never released for the non-military market, but the otherwise identical i960MC was used in high-end embedded applications. The i960MC included all of the features of the original BiiN system, but these were simply not mentioned in the literature, leading many to wonder why the i960MC was so large and had so many pins labeled "no connect". (da: https://en.wikipedia.org/wiki/Intel_i960 con modifiche personali).

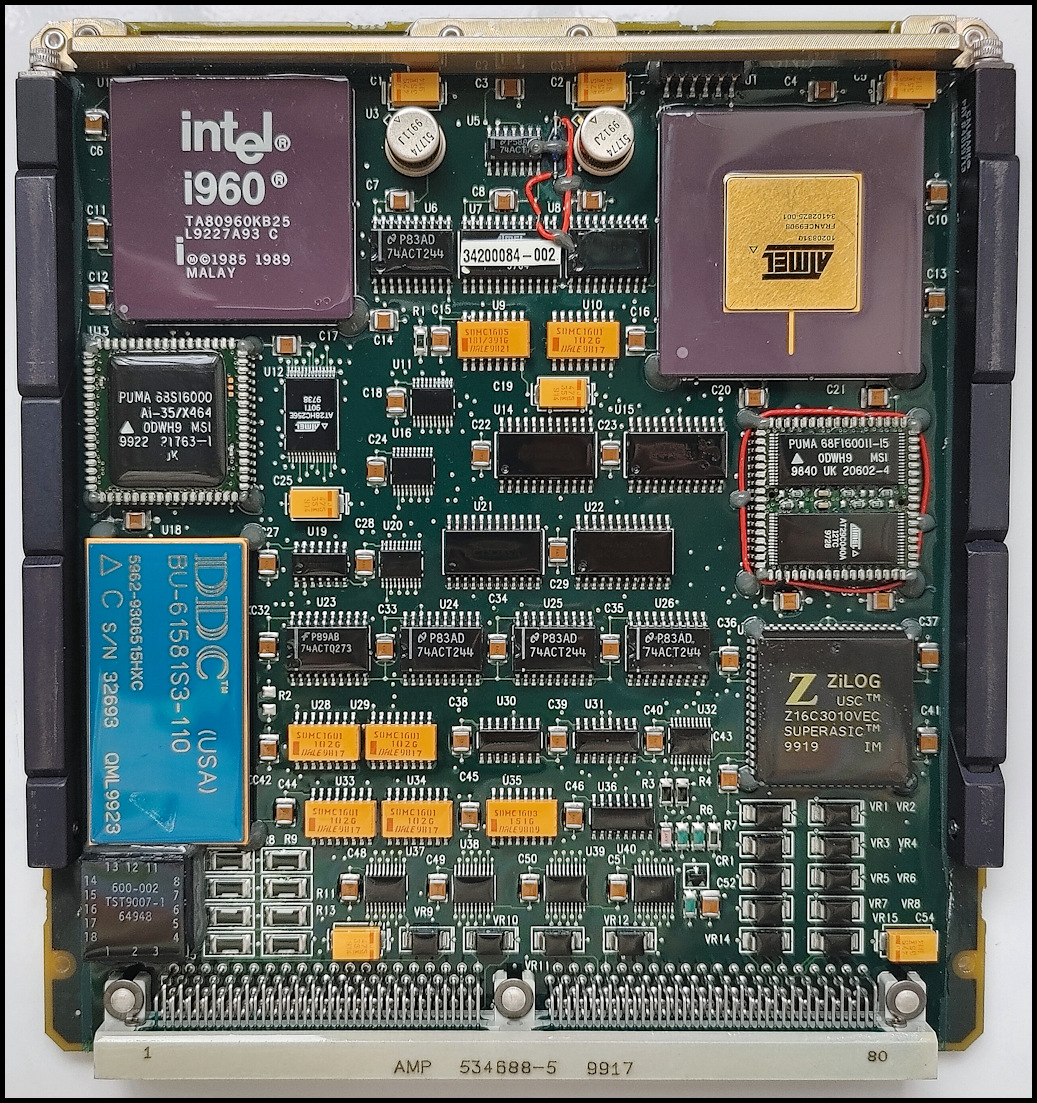

Scheda di avionica (processore di dati radar) con CPU RISC Intel i960KB -versione del KA con FPU- a 25 MHz e vari componenti di supporto (1999).

Engineering sample di CPU Intel i960HD-66 su ICE (In-Circuit Emulator) di Applied Microsystems (1996). L'i960HD è una CPU superscalare della famiglia Intel 960 che può eseguire 2 istruzioni per ciclo di clock, corrispondenti a 132 MIPS teorici a 66 MHz; è dotato di FPU ed MMU integrate.

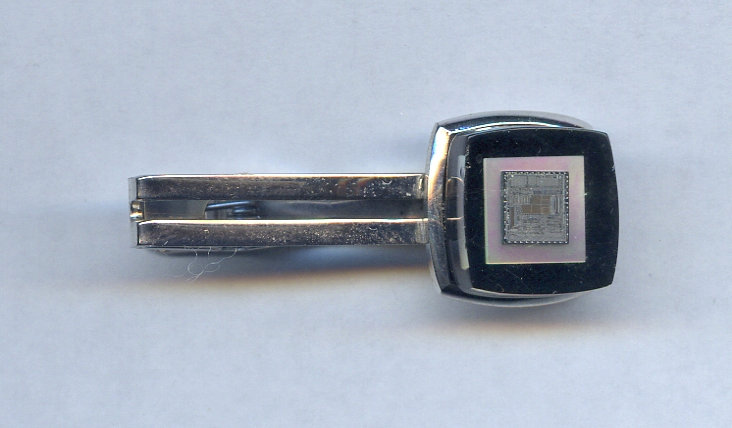

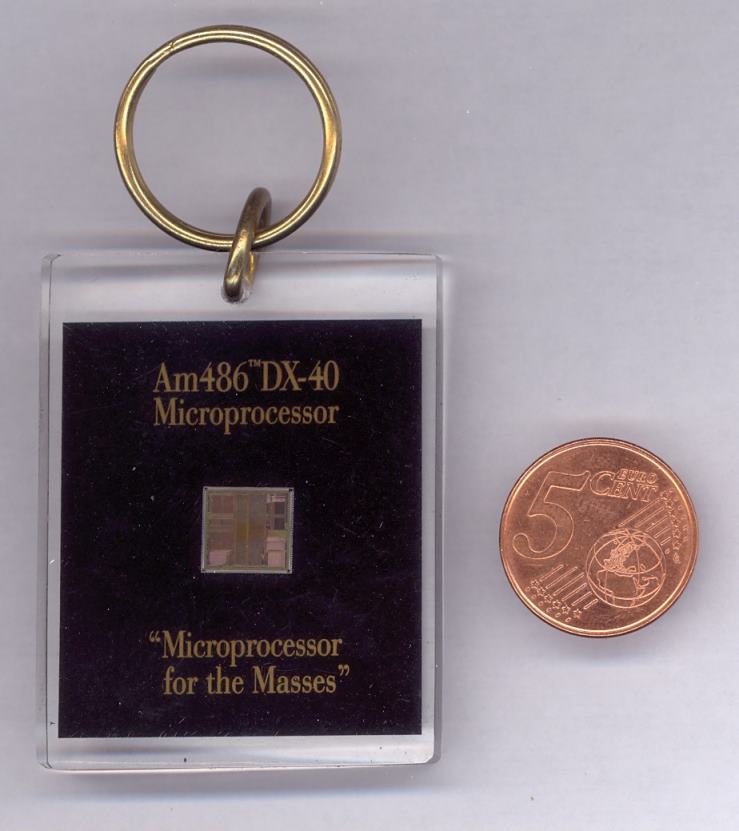

Portachiavi contenente il chip di un microprocessore AMD Am486DX-40. Questa CPU è stata introdotta nell'Aprile 1993 come concorrente a basso costo (da qui il motto "microprocessore per le masse") dell'Intel 486DX-33, all'epoca diffuso nei PC di fascia bassa in quanto più economico dei 486DX/2 a 50 e 66 MHz. E' dotata di 8 KB di cache write-through e la frequenza di bus (FSB) è la medesima del processore, 40 MHz.

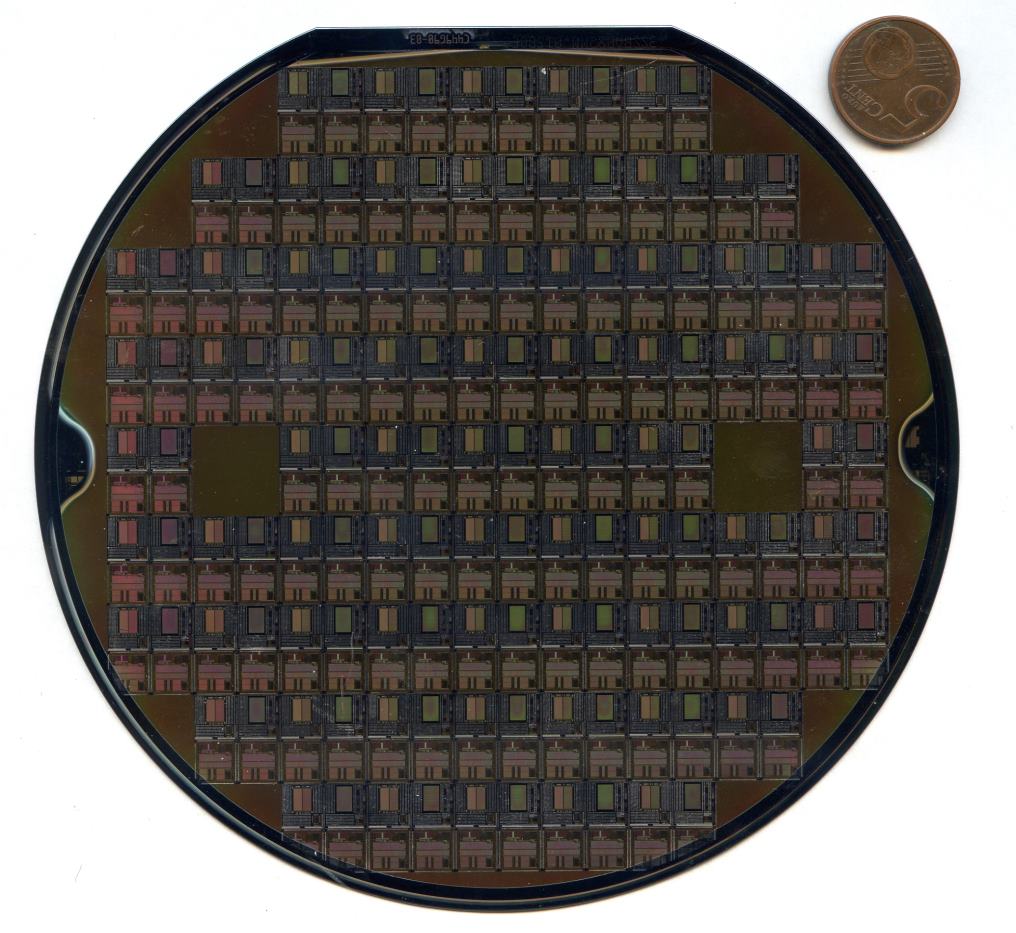

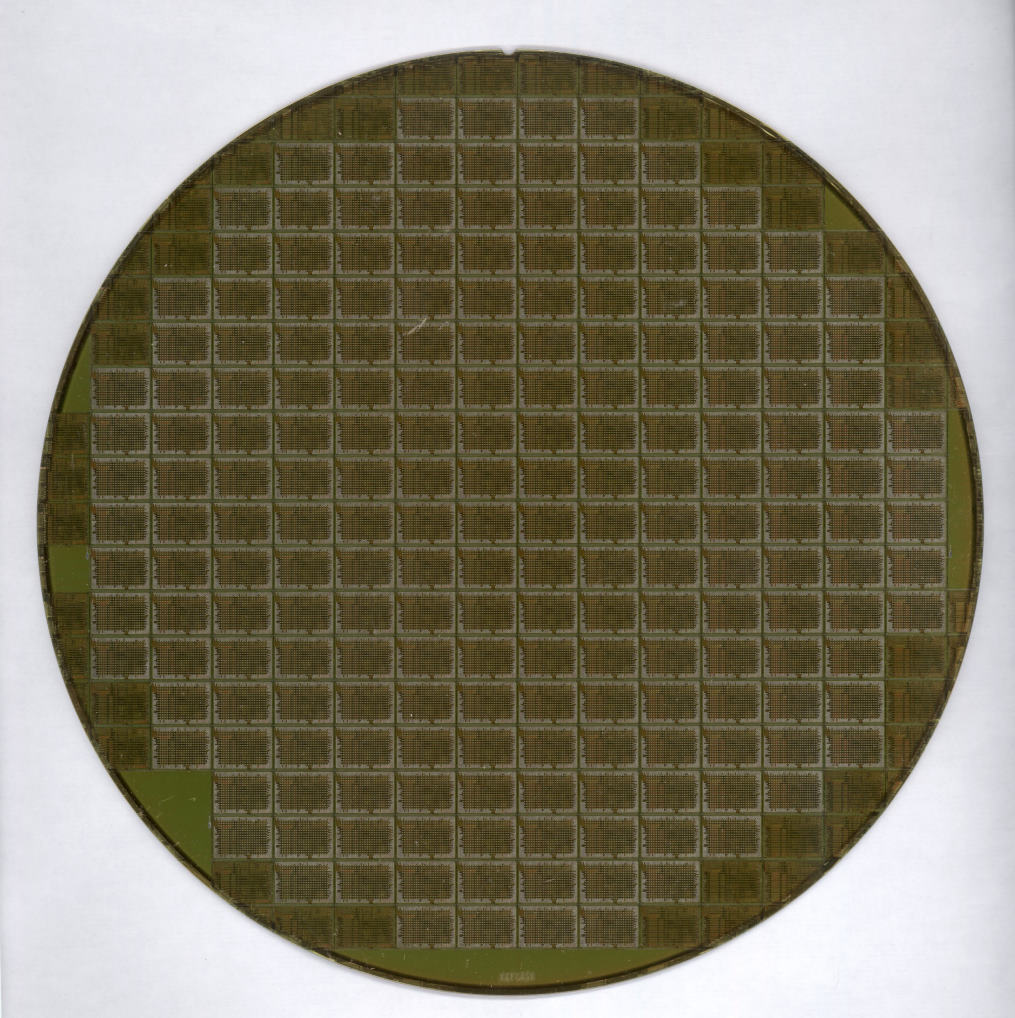

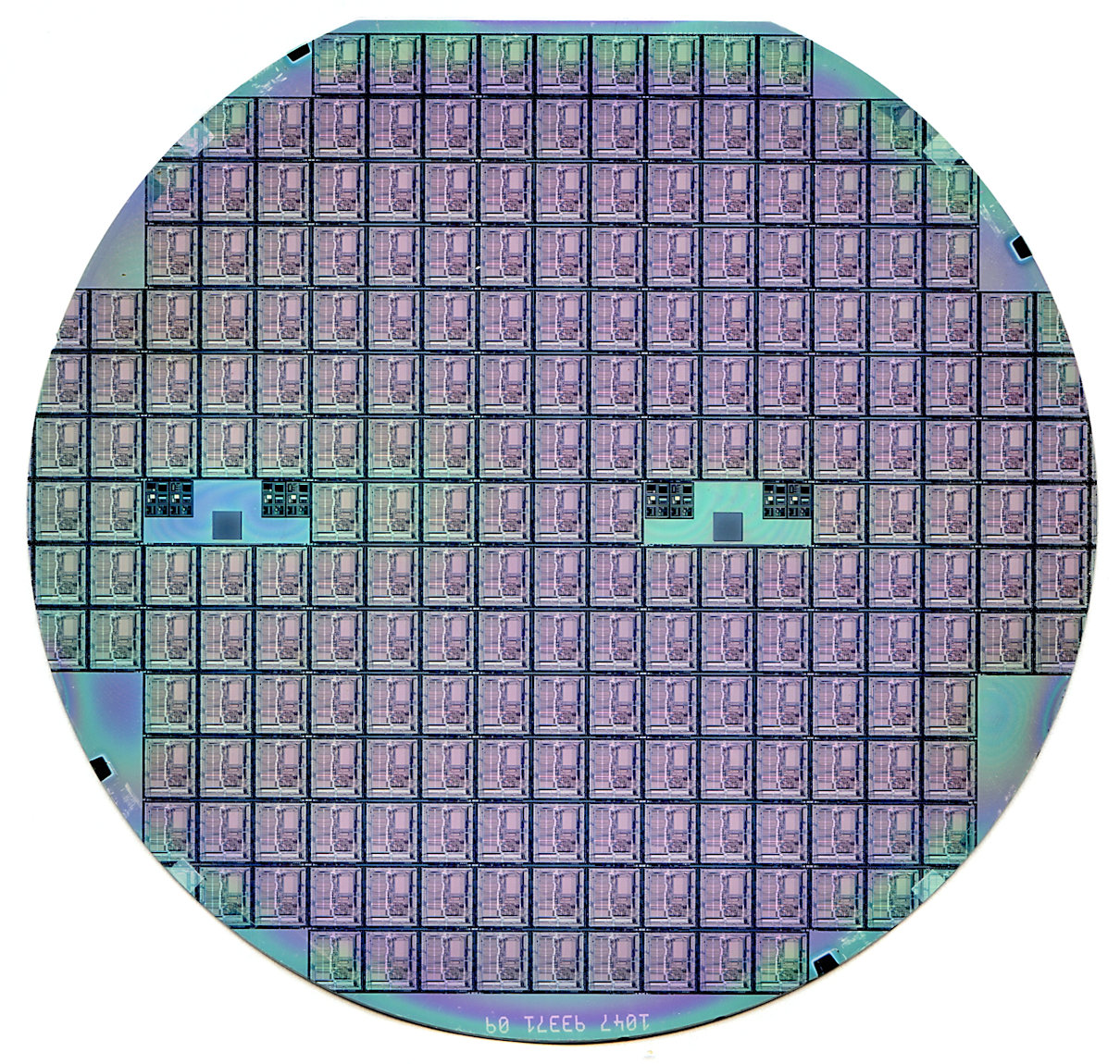

26.4.2016 - Wafer completo di processori AMD Am486DX4-100. I die sono identici a questo: https://commons.wikimedia.org/wiki/File:AMD_80486DX4_die.JPG. Alternate alle file delle CPU vere e proprie ci sono serie di componenti utilizzati per il test del processo produttivo. Il 486DX4-100 è stato introdotto da AMD nel 1995 per competere con i Pentium di fascia bassa; integra 8 KB di cache di primo livello unificata Write-Through ed ha un Front-Side Bus (FSB) a 33 MHz. L'alimentazione è a tensione singola ( 3 V). La frequenza di clock consentiva a queste CPU, in particolare ai modelli a 100 e 120 MHz (ne è stata prodotta anche una versione a 75 MHz) di raggiungere prestazioni superiori, nelle comuni applicazioni da ufficio a 16 e 32 bit, ai processori Pentium a 60 e 66 MHz. La velocità in virgola mobile rimaneva invece nettamente inferiore. Le CPU Intel 486DX4 offrivano prestazioni simili, sia pure con una cache doppia (16 KB), ma a parità di clock costavano sensibilmente più delle controparti AMD. Ad esempio un Am486DX4-100 veniva commercializzato nel 1995 allo stesso prezzo di un Intel DX2-66.

Chip di processore AMD K5 (1995/6), versione SSA/5 con clock interno a 100 MHz e Front Side Bus a 66 MHz. Il K5 è stato il primo processore x86 interamente sviluppato e prodotto internamente da AMD. E' stato commercializzato a partire dal 1996 come concorrente dell'Intel Pentium. Benché basato su un'architettura interna di derivazione RISC più avanzata di quella del rivale Pentium e più simile a quella di sesta generazione (P6) del Pentium Pro (esecuzione speculativa, superscalarità, esecuzione fuori ordine, maggior numero di unità di calcolo operanti in parallelo), il K5 soffriva la limitata frequenza di clock e le scarse prestazioni in virgola mobile. Per questo motivo, pur essendo sotto molti aspetti migliore del contemporaneo Cyrix 6x86, ha avuto poco successo commerciale a differenza di altre CPU prodotte da AMD (Am486, K6, Athlon). Il chip contiene 4,3 milioni di transistor ed è fabbricato con processo CMOS a 500 nm (350 nelle versioni più recenti, i cui chip sono sensibilmente più piccoli di questo).

Wafer di CPU Cyrix 6x86MX o M2 (1997). Questo processore è un'evoluzione del precedente modello 6x86/M1 rispetto al quale ha cache più ampie (64 KB contro 8), una migliore compatibilità con le CPU Pentium e Pentium Pro ed un set di istruzioni "multimediali" (EMMI) compatibili con le MMX di Intel. Come il predecessore, però, il 6x86MX ha sofferto particolarmente la debolezza dell'unità in virgola mobile nei confronti di quelle dei rivali Intel ed AMD. Cyrix preferì puntare sull'efficienza e la velocità di esecuzione delle istruzioni "intere", compiendo il grave errore strategico di sottovalutare l'importanza di avere una FPU veloce nel momento in cui cominciavano a diffondersi programmi multimediali e giochi che la richiedevano. Un ulteriore limite del M.II, come già del M.I, era la ridotta scalabilità del processo di fabbricazione che impediva di innalzare le frequenze operative oltre i 200 MHz. Per il resto le CPU 6x86/6x86MX reggevano tranquillamente il confronto con le rivali Intel ed AMD nelle comuni applicazioni da ufficio, e per questo motivo hanno avuto una certa diffusione alla fine degli anni Novanta nei PC economici di fascia bassa, anche per merito del loro basso consumo. Il 6x86MX integra circa 4,5 milioni di transistor ed è fabbricato con processo a 500 nanometri.

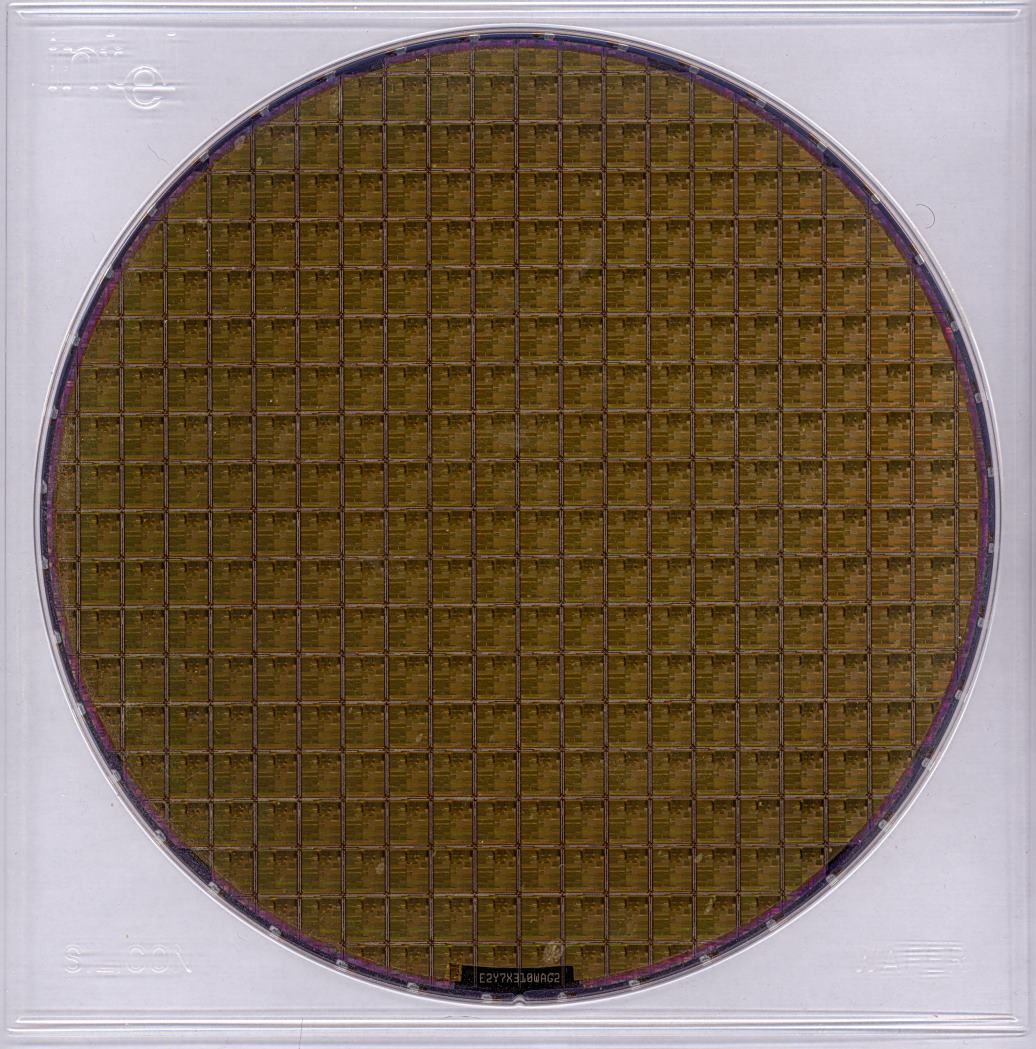

Wafer da 8 pollici con processori Intel Pentium P54CS (1995). La CPU P54CS è un'evoluzione della P54C (80502), talvolta chiamata anche "Pentium S". Al pari di quest'ultima lavora con alimentazione singola a 3,3 Volt contro i 5 V delle prime versioni del Pentium (P5 o 80501), il che consente un risparmio di energia nell'ordine del 50%. Le frequenze di lavoro vanno da 133 a 200 MHz (laddove i processori P54C operano nella fascia 75-100 MHz). Il processo di fabbricazione è BiCMOS a 0,35 micrometri con 4 livelli di interconnessione; la CPU contiene in totale circa 3,3 milioni di transistor ed ha una superficie di 90 millimetri quadrati.. La maggiore complessità dei Pentium P54C e P54CS rispetto agli 80502 originali (3,1 milioni) è dovuta alla presenza di alcune modifiche ed aggiunte rese necessarie dal fatto che il processore opera ad una frequenza interna multipla di quella di bus. Il Pentium P54CS a 133 MHz è stato il primo processore commerciale fabbricato con processo BiCMOS a 0,35 micron. L'organizzazione del chip è sostanzialmente identica a quella dei processori P54C, che hanno un'area maggiore (163 millimetri quadrati) in quanto fabbricati con procedimento a 0,50 micron. Una microfotografia dettagliata del chip P54C è visibile qui.Wafer come quello visibile qui venivano venduti da Intel ai visitatori degli impianti di produzione (in gergo "fab") negli Stati Uniti ed in Israele. Si tratta in genere di esemplari scartati perché difettosi. Una parte dei chip non utilizzabili (che possono essere dovuti a svariate cause, ad es. imperfetto allineamento delle maschere o impurità locali nel wafer) veniva "convertita" in gadget di vario tipo (spille, fermacarte, portachiavi, perfino orecchini). Il wafer della foto è incollato su di un supporto di plastica trasparente dal quale credo sia impossibile rimuoverlo senza romperlo.

Vedi: https://www.flickr.com/photos/97377381@N03/9163028156/in/album-72157634094135040/ (immagine ad alta risoluzione del chip).

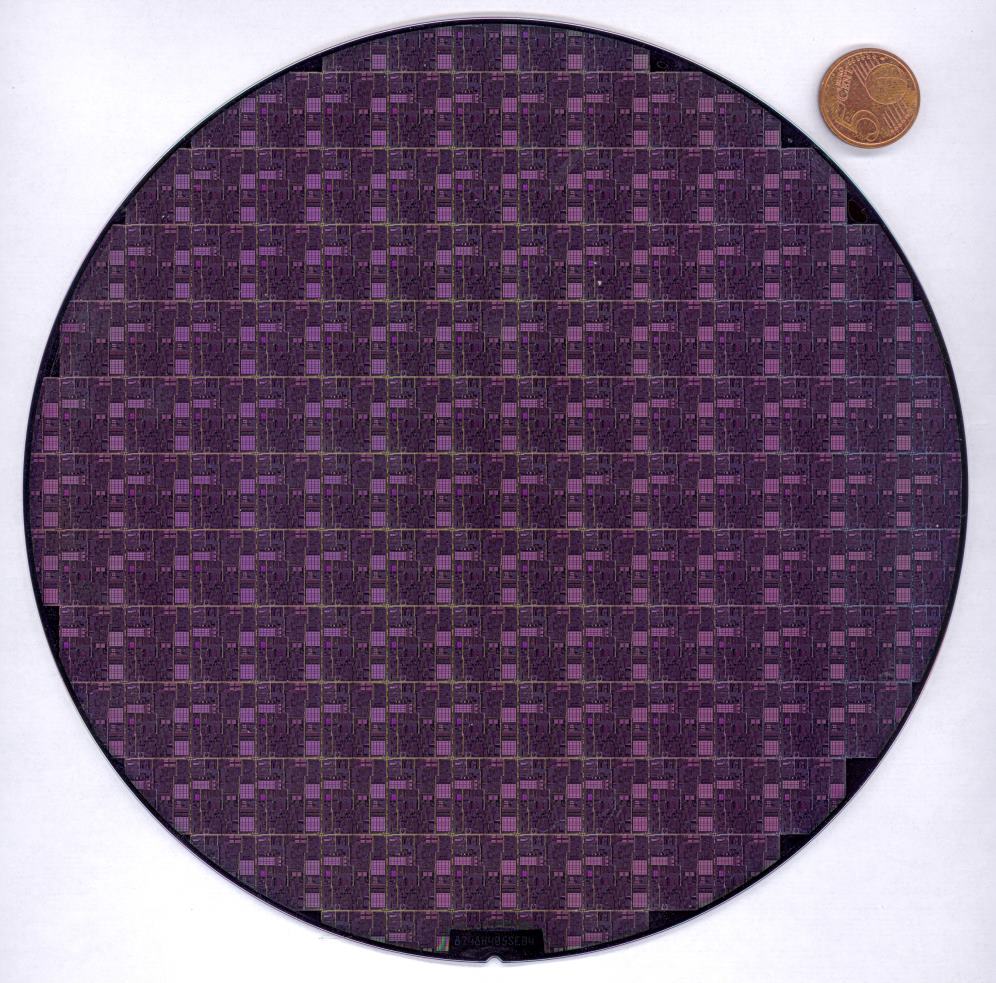

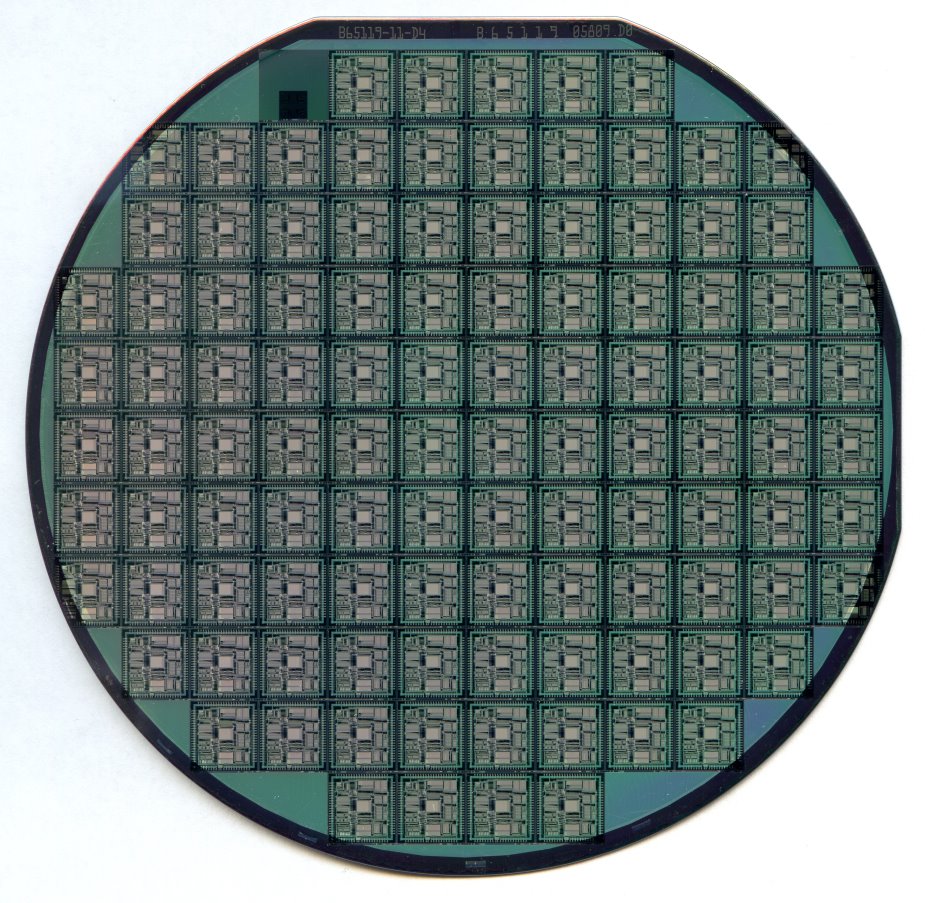

Wafer da 8 pollici con CPU Intel Pentium MMX (1997). Faceva parte, molto probabilmente, di un kit educativo "Journey Inside the Computer" (vedi: https://www.computerhistory.org/collections/catalog/102662439), del quale esistono più versioni con CPU diverse.

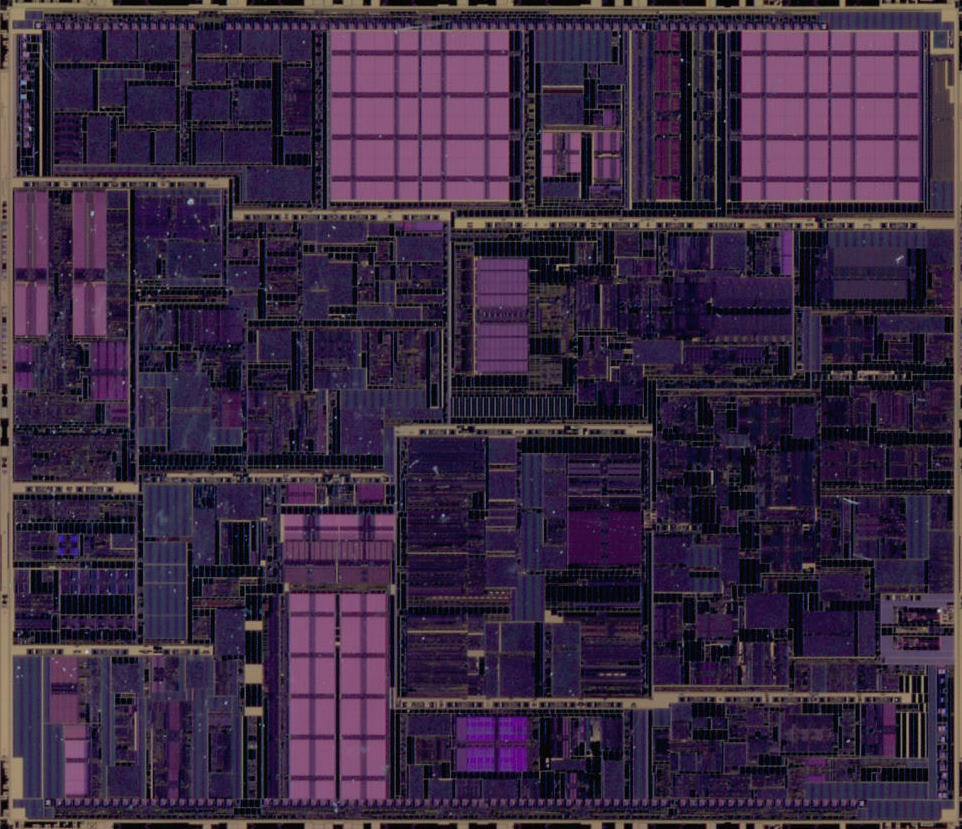

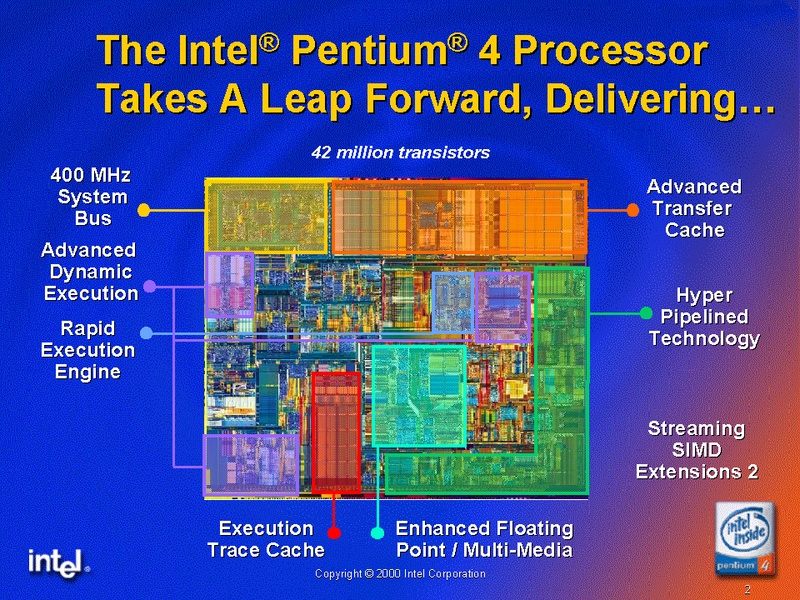

Wafer da 8 pollici contenente CPU Intel Pentium 4 a 1,5 GHz, core Willamette a 180 nm (2000). Credo manchi il livello di metallizzazione superiore. Questa è stata la prima CPU con architettura Netburst commercializzata da Intel. Già in questa immagine, e poi più chiaramente nella successiva, sono visibili le cache da 512 KB (i quadratini chiari sovrapposti) e la trace cache (il piccolo rettangolo chiaro). Inizialmente i Pentium 4 richiedevano costose memorie RDRAM a 400 MHz; successivamente, nel 2001, con l'introduzione del chipset i845 divenne possibile impiegare le più diffuse ed economiche SDRAM a 133 MHz. I core Willamette e Northwood hanno un Front-Side Bus (FSB) a 64 bit e 100 MHz che accoppiato al chipset i850 offre una banda di memoria di 3,2 GB/s. La possibilità di impiegare memorie SDRAM fece aumentare significativamente le vendite dei Pentium 4 nel settore dei PC di fascia media e medio/bassa. L'architettura Netburst venne sviluppata alla fine degli anni Novanta quando sembrava che la strada per incrementare le prestazioni dei processori fosse l'aumento della frequenza anziché del parallelismo. Intel prevedeva di "spingerla" fino a 10 GHz quando, in realtà, il limite tecnologico effettivo di frequenza è di circa 5 GHz (il Pentium 4 a maggiore frequenza mai prodotto funzionava a 3,8 GHz). Proprio per trarre vantaggio dalle elevate frequenze di lavoro le CPU Netburst sono caratterizzate da una pipeline molto lunga, inizialmente a 20 stadi diventati poi 31, che dà luogo a notevoli penalizzazioni in caso di errata predizione delle destinazioni delle istruzioni di salto.La trace cache, più precisamente Execution Trace Cache, memorizza le micro-operazioni già decodificate e serve proprio a ridurre il più possibile gli errori di predizione. Altra caratteristica dei processori con architettura Netburst è che la ALU opera ad una frequenza doppia rispetto al resto della CPU, il che consente di compensare lo svantaggio del minor numero di istruzioni eseguite per ciclo che si ha rispetto alle CPU di classe P6. Nel 2002 si aggiunse l'HyperThreading, denominazione data da Intel all'implementazione in questa classe di CPU del multithreading simultaneo (SMT). In rapporto alla frequenza di lavoro le prestazioni dei processori con architettura Netburst non sono molto elevate, tanto che a parità di frequenza esse risultano inferiori a quelle delle CPU P6 (ad esempio il Pentium III).

Dettaglio di una singola CPU presente nel wafer visibile sopra (scansione a 2.400 dpi). Il core Willamette, fabbricato con processo a 180 nm, contiene circa 42 milioni di transistor. L'area del chip è di 217 millimetri quadrati. In questa pagina è disponibile un'immagine più dettagliata ottenuta tramite microscopio e si può vedere un wafer di processori con core Northwood a 130 nm.

Descrizione annotata del core Willamette rilasciata da Intel all'Intel Developers Forum del 2000.

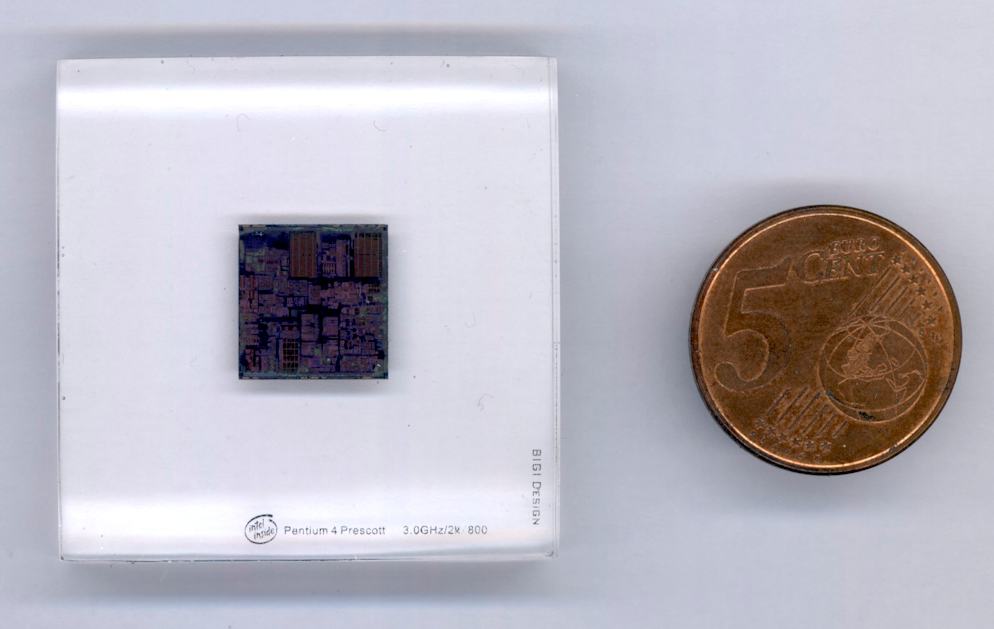

Piccolo fermacarte contenente una CPU Intel Pentium 4 con core Prescott a 3 GHz.

Engineering sample di Network Processor Intel IXP2350 (2004), a sinistra, e IXP2805 (2005), a destra.Si tratta di processori dedicati alle applicazioni di rete, che possono essere ad esempio utilizzati come "motori" di switch, router, firewall o crittografia. Il 2350 è basato su 4 core XScale a 32 bit/900 MHz, multithreaded, mentre il 2805 contiene 16 core MIPS-64 funzionanti a 1,4 GHz.

Vedi: https://www.datasheets.com/en/part-details/ixp2350-intel-19828039 (IXP2350), https://www.researchgate.net/figure/The-Intel-IXP-2805-From-34_fig5_224105799.

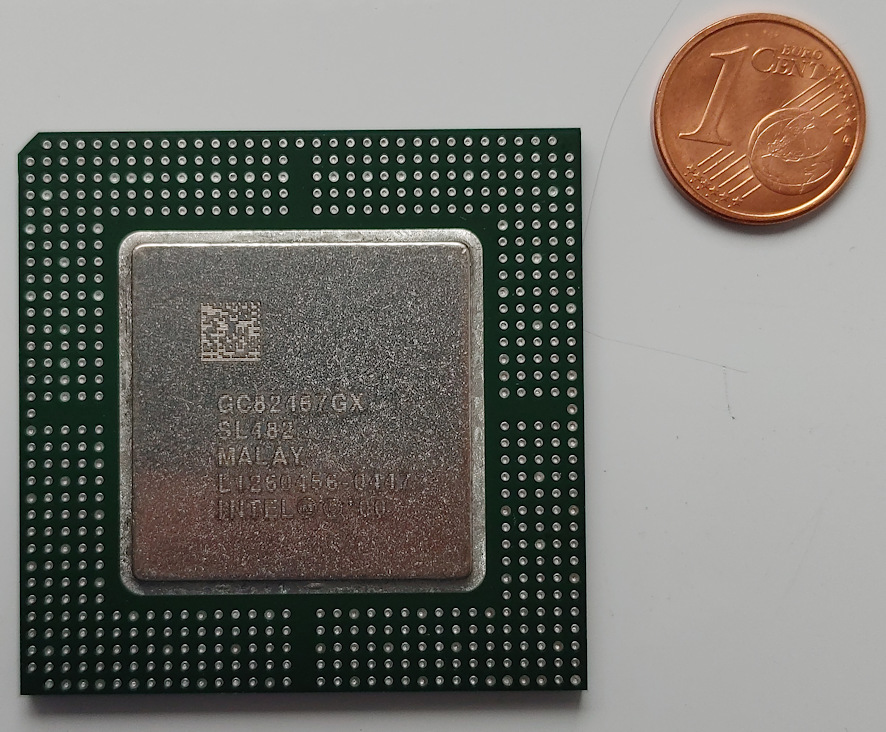

Engineering sample di Memory Controller Intel 82467GX (2000), parte del chipset 460GX per sistemi SMP basati su CPU Xeon.

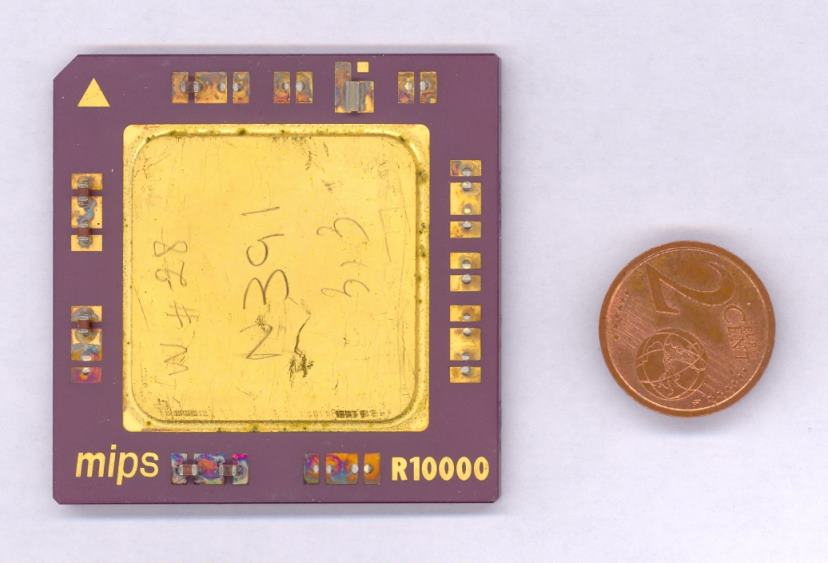

11.2.2016 - Wafer completo di microprocessori MIPS R4000 a 150 MHz. Questa CPU, annunciata nell'Ottobre 1991, è stato uno dei primi microprocessori commerciali a 64 bit. L'R4000 è un microprocessore scalare super-pipelined con pipeline a 8 stadi ed unità in virgola mobile (FPU) integrata. Contiene circa 1,2 milioni di transistor ed è fabbricato solitamente con processo CMOS a 2 livelli di metallizzazione. La sua complessità è quindi paragonabile a quella del 486DX. Alcuni produttori hanno realizzato versioni a 0,8 micron. E' stato commercializzato in tre distinte versioni: la PC per sistemi entry level, senza supporto per la cache esterna di secondo livello (package PGA-179), la SC con supporto per la cache L2 ma non per le configurazioni SMP e la MC che supporta anche queste ultime. Sia la versione SC che la MC sono contenute in package PGA-447; alcuni piedini sono tuttavia utilizzati solamente nella MC in quanto portano i segnali relativi al controllo di coerenza della cache. La CPU R4000 fa uso di indirizzi virtuali a 64 bit, dei quali in effetti ne sono però utilizzati solamente 40 per un'ampiezza dello spazio di indirizzamento virtuale di 1 TB; gli indirizzi fisici sono invece a 36 bit (possono essere indirizzati quindi 64 GB di memoria fisica). La cache di primo livello, integrata e separata tra dati ed istruzioni, è ampia 8+8 KB; quella di secondo livello (esterna) può avere invece una capacità compresa tra 128 KB e 2 MB complessivi. L'R4000 ha un bus di sistema a 64 bit, di tipo multiplexed (le medesime linee sono utilizzate sia per i dati che per gli indirizzi) per ridurre il numero di collegamenti necessari pur a costo di una minore banda utile. Questo bus è denominato SysAD e può funzionare a metà, un terzo oppure un quarto della frequenza di clock della CPU. Storicamente il MIPS R4000 è importante perché era stato scelto, all'inizio degli anni Novanta, come CPU-modello dell'ACE (Advanced Computing Environment), lo standard industriale che nelle intenzioni dei proponenti avrebbe dovuto costituire una piattaforma RISC unificata capace di rimpiazzare nel medio termine le architetture CISC dominanti quali la x86/IA-32 (rappresentata all'epoca dal 386 e dal 486) e la Motorola 68K (68030/040). Le specifiche tecniche dell'ACE vennero sviluppate da un variegato consorzio di produttori (Compaq, Microsoft, DEC, SCO, MIPS) formatosi nel 1991. All'epoca era diffusa la convinzione che entro la metà degli anni Novanta le CPU RISC avrebbero soppiantato le x86 nei PC e nelle workstation tecniche di fascia medio/alta; si pensava anche che Windows NT (originariamente noto come OS/2 3.0) e la versione SCO di Unix, equipaggiata con Open Desktop, sarebbero presto diventati i due sistemi operativi di riferimento per tale classe di macchine. Il consorzio fu costituito proprio con l'intento di diffondere queste tecnologie, offrendo così un'alternativa praticabile ed economicamente conveniente alla piattaforma "Wintel" a 32 bit, ma ebbe vita breve a causa sia di contrasti tecnici e commerciali tra i fondatori sia dell'arrivo sul mercato tra il 1992 ed il 1993 di CPU x86 più potenti quali il Pentium ed il 486DX-2, che ridussero il vantaggio competitivo dei RISC funzionanti a frequenze comprese tra 120 e 150 MHz. Il principale prodotto dell'iniziativa ACE furono le specifiche ARC (Advanced RISC Computing), inizialmente pensate per un'architettura standard basata su CPU MIPS R4000. Benché non sia mai stato sviluppato e commercializzato nessun sistema pienamente rispondente a queste specifiche, la loro eredità è stata lunga ed influente dal momento che, ad esempio, tutti i sistemi operativi di classe NT fino all'avvento di Windows Vista nel 2006 hanno impiegato proprio le convenzioni definite in ambito ARC per l'identificazione delle unità disco di avvio e di altri elementi hardware. Queste stesse convenzioni furono adottate anche sui sistemi SGI con CPU MIPS e sistema operativo IRIX 6.1 o più recente (Indigo2, Indy...) nonché su workstation di altri produttori basate sempre su processori MIPS e, successivamente, anche PowerPC ed Alpha. Ricordiamo con l'occasione che Windows NT è stato sviluppato non solo per la piattaforma IA-32 ma anche per MIPS, Alpha e PowerPC. Nelle intenzioni iniziali anche Windows 2000 (NT 5.0) avrebbe dovuto supportare l'architettura Alpha. Il consorzio ACE ha rappresentato una delle "alleanze" cooperative tra produttori di hardware sorte con l'intento di contrastare lo strapotere dell'accoppiata Microsoft Windows + processori Intel x86 (Wintel); un'altra, più nota, è stata la "AIM Alliance" alla quale hanno partecipato Motorola, IBM ed Apple.

Wafer di CPU MIPS R3000A, utilizzate fra l'altro nella PlayStation originale di Sony.

CPU MIPS R4400-SC, evoluzione della R4000, fabbricata da IDT (1993).

Wafer da 3,5 pollici di integrati MOS risalente ai primi anni Ottanta.

Espositore didattico in plexiglass, di provenienza sconosciuta, contenente diversi tipi di integrati (principalmente Fairchild e Ferranti), 4 wafer di diverso diametro ed una maschera fotolitografica (in alto a destra). Tutti i componenti risalgono ai primi anni Ottanta. I due integrati in basso a destra, in package CLCC di colore bianco, sembrano essere gate array. Quello più a sinistra è fabbricato da Fairchild. Immediatamente sopra, alcuni esempi di ULA (gate array) Ferranti datati 1981 e 1982.

Dettaglio dei 4 wafer e di parte della maschera fotolitografica visibili nell'immagine precedente.

Un altro espositore didattico in plexiglass che contiene a sinistra un substrato ceramico per modulo multichip (non è riconoscibile il fabbricante) e, a destra, un contenitore di die cioè di integrati finiti e separati l'uno dall'altro mediante il taglio del wafer ma ancora da inserire nei rispettivi package.

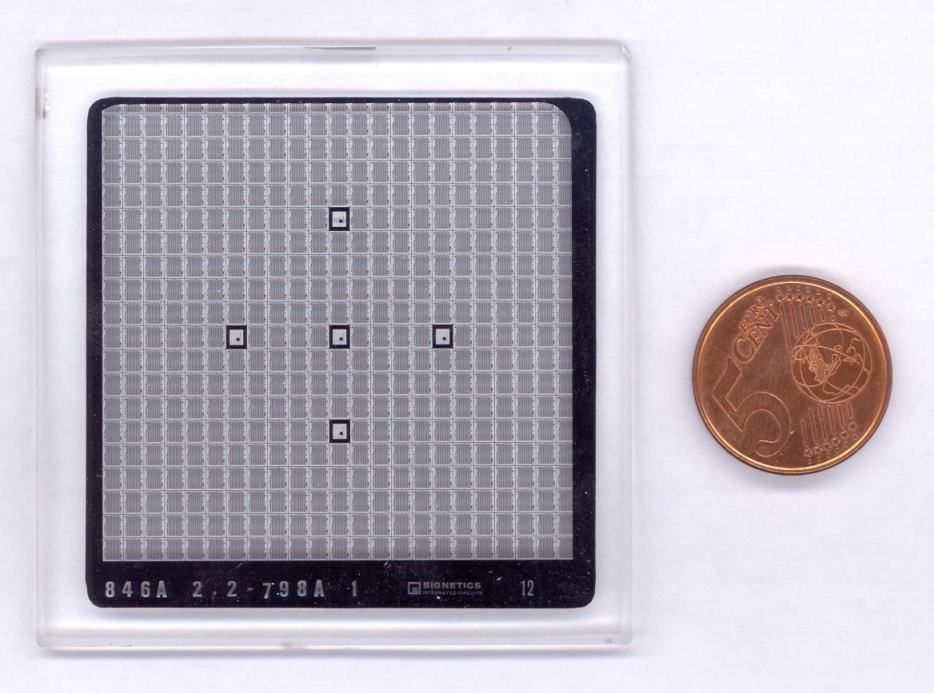

Maschera fotolitografica Signetics (inizio anni Ottanta) per la fabbricazione di memorie ROM.

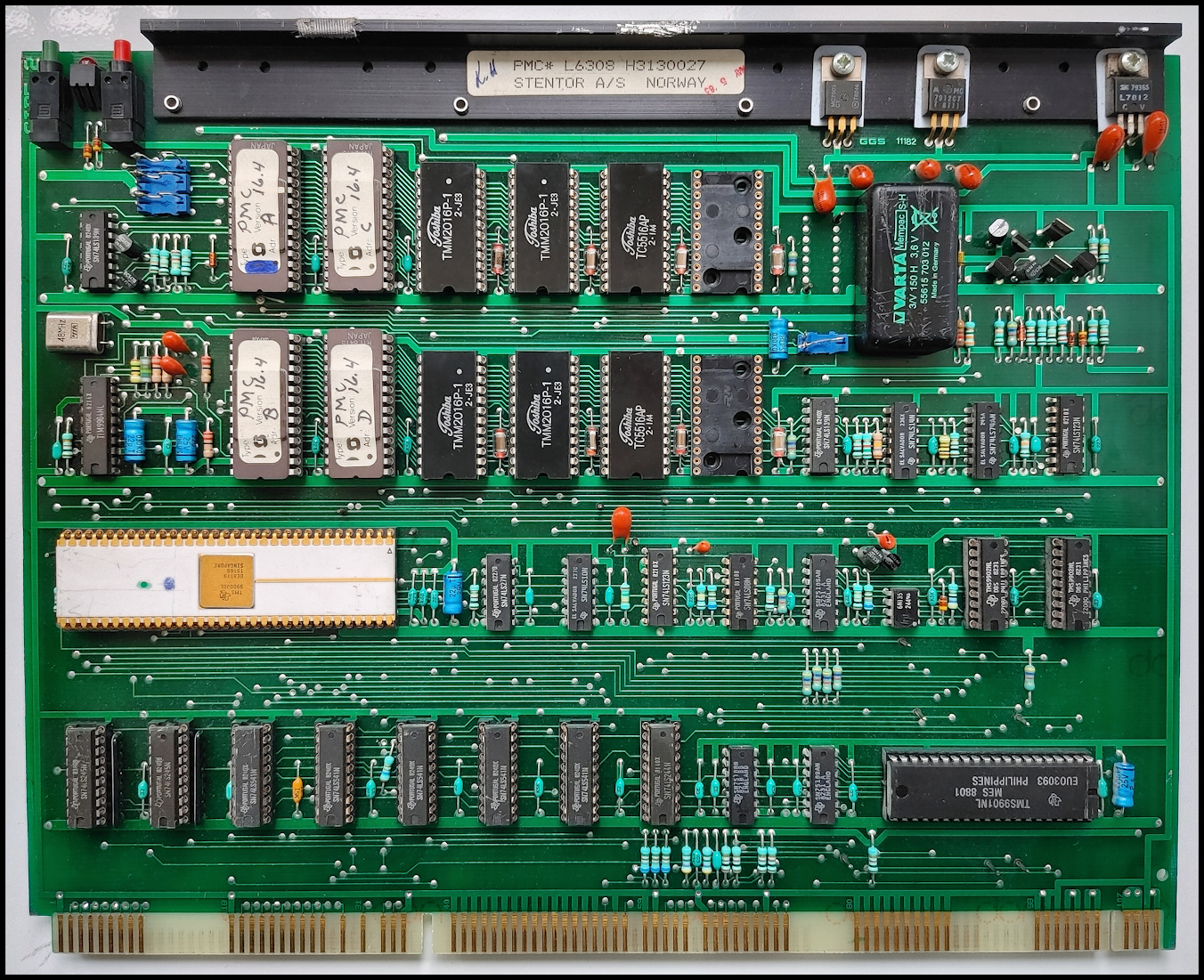

Scheda con CPU Texas Instruments TMS9900JDL a 3 MHz (vedi: https://en.wikipedia.org/wiki/Texas_Instruments_TMS9900). La configurazione di sistema è tipica, con quarzo a 48 MHz, generatore di clock TIM9904 e Programmable System Interface TMS9901NL (a sinistra).

Altro esempio di scheda con microprocessore Texas Instruments TMS9900 (1983).

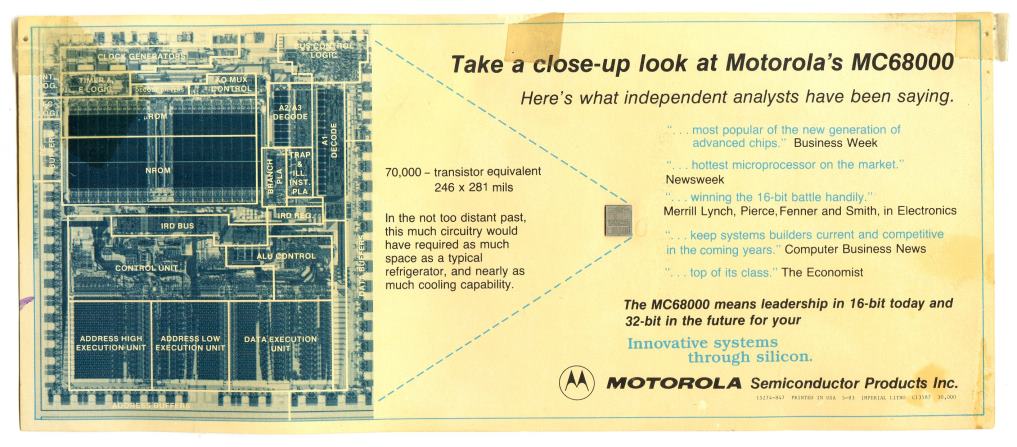

26.4.2016 - Cartolina promozionale Motorola contenente il die di un processore MC68000 accanto a una microfotografia dello stesso. Questa CPU a 16/32 bit, introdotta nel 1979, è stata tra i processori in assoluto più popolari. E' la capostipite della famiglia m68K che a distanza di circa 36 anni dalla sua introduzione viene ancora utilizzata in molte applicazioni. Il 68000 è stato utilizzato in molte macchine diffusissime come ad esempio l'Apple Macintosh, la workstation Sun-1 ed i Commodore Amiga 2000, 1000, 600 e 500.

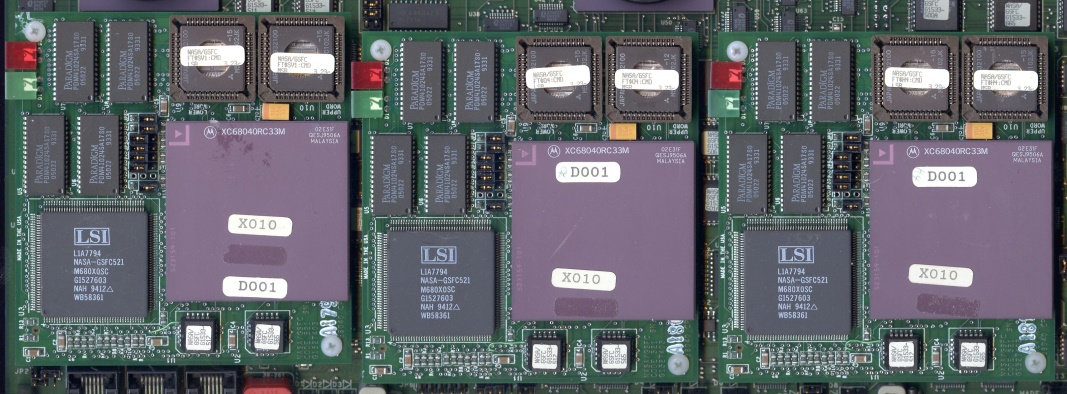

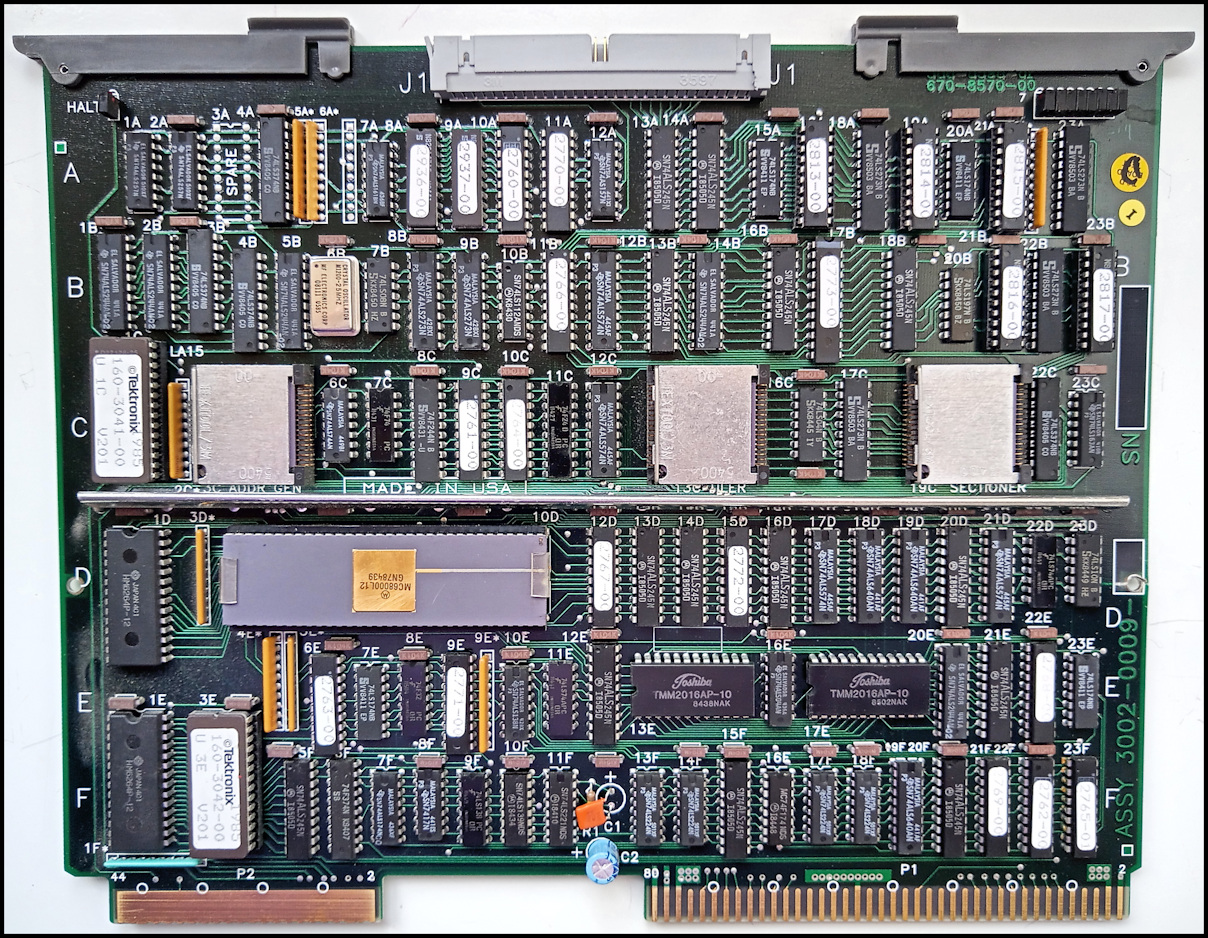

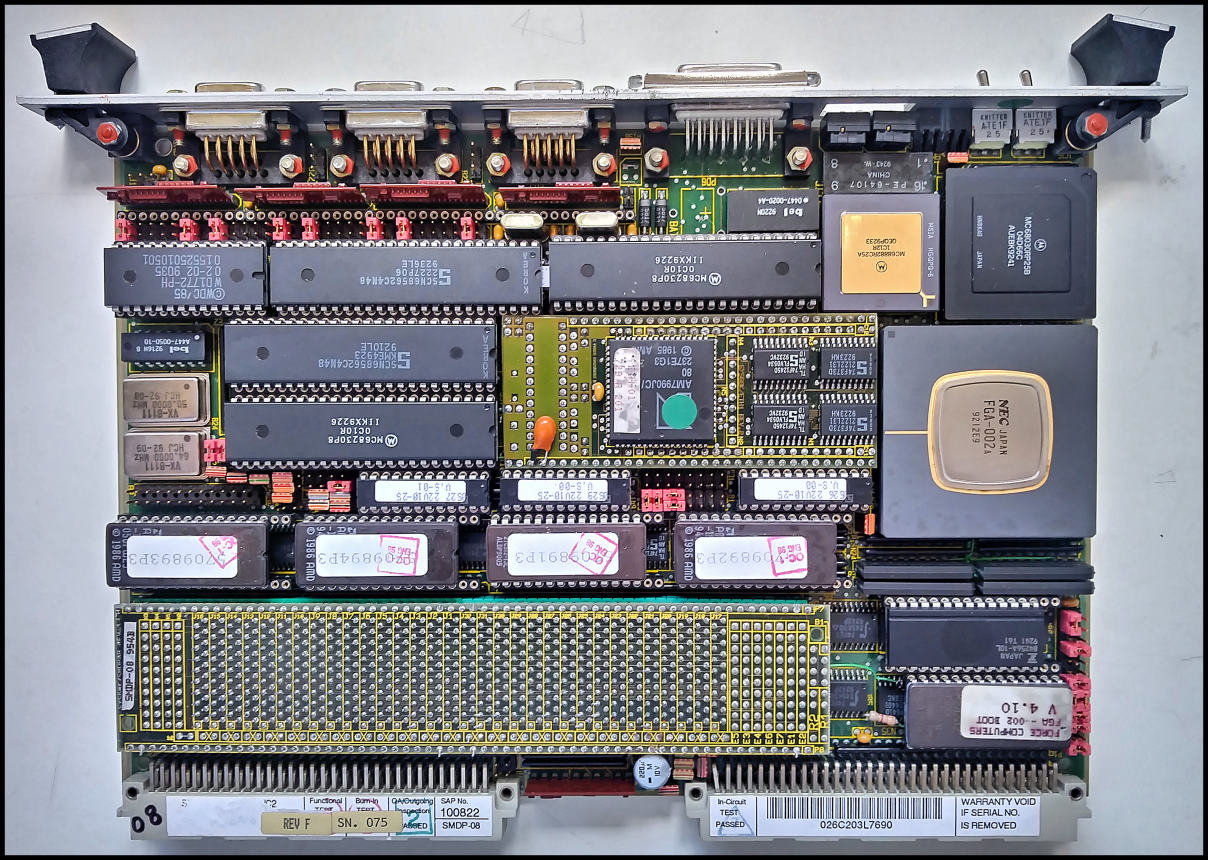

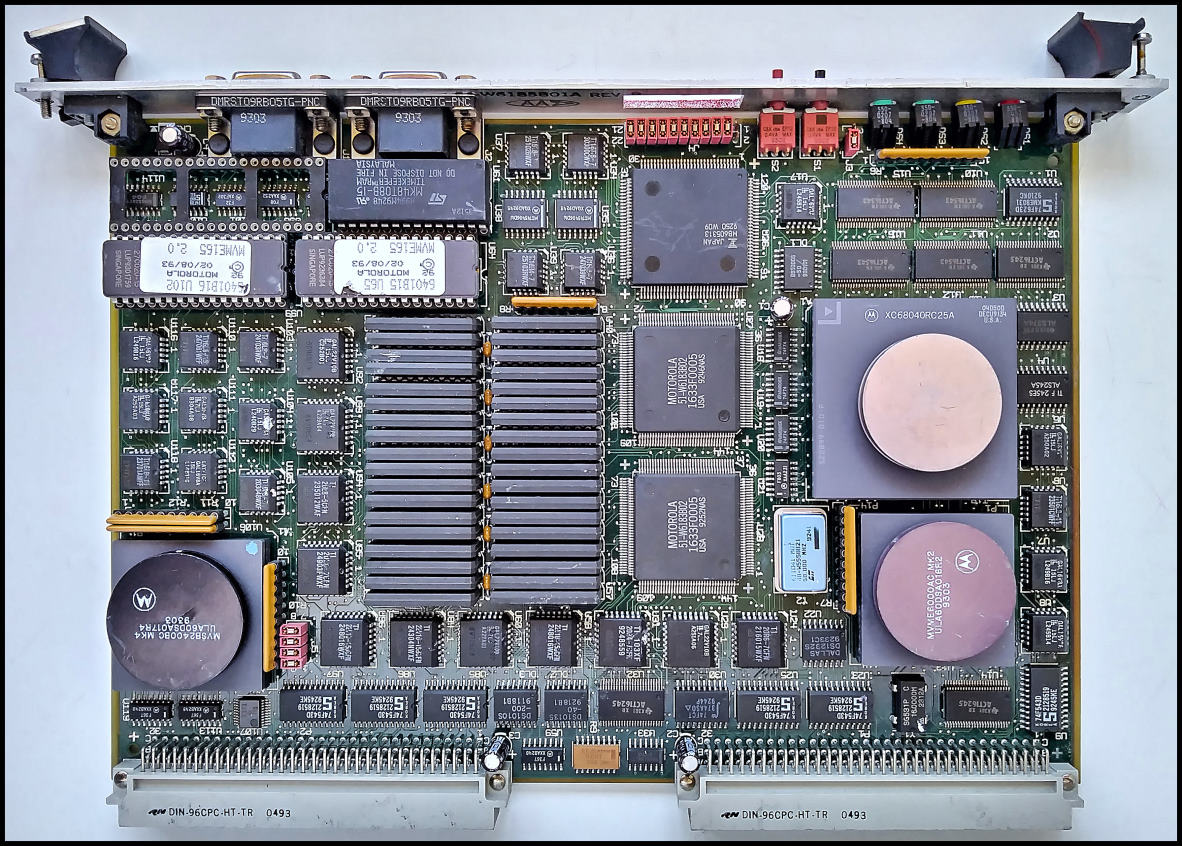

Dettaglio di una scheda VME proveniente da un computer di controllo del Goddard Space Flight Center (GSFC) della NASA, 1994, con 3 daughterboard ciascuna equipaggiata con una CPU a 32 bit Motorola 68040RC a 33 MHz, 2 MB di DRAM locale ed un ASIC di supporto ed interfaccia. La scheda è siglata "Command Processor" ed è probabilmente un processore fault-tolerant ridondante. Il 68040, o semplicemente "040" come è spesso chiamato, è stato un fortunato e diffusissimo membro della famiglia Motorola 68K; introdotto nel 1990, rappresenta l'evoluzione del 68030 ed è stato a sua volta seguito dal meno popolare 68060. Il 68040 rappresenta storicamente la prima CPU 68K con FPU ed MMU integrate; in questo era concettualmente simile al concorrente diretto Intel 80486DX rispetto al quale integrava circa il medesimo numero di transistor (1,2 milioni) pur essendo significativamente più veloce a parità di frequenza di clock. E' stato utilizzato come CPU in molti diversi modelli di personal computer (Apple Macintosh Quadra, Centris, Performa, PowerBook, Commore Amiga 4000), workstation (Apollo 3500, HP 9000/400, NeXTcube, NeXTstation), server ed apparati di rete (Cisco Supervisor Engine I). Il GSFC, fondato nel 1959, è uno dei più importanti centri di ricerca e sviluppo della NASA nonché uno tra i maggiori laboratori degli Stati Uniti (vi lavorano circa 10.000 persone tra scienziati, tecnici, impiegati e dirigenti).

Scheda CPU di server Unix SMP Bull Escala con processore IBM PowePC 604e a 225 MHz.

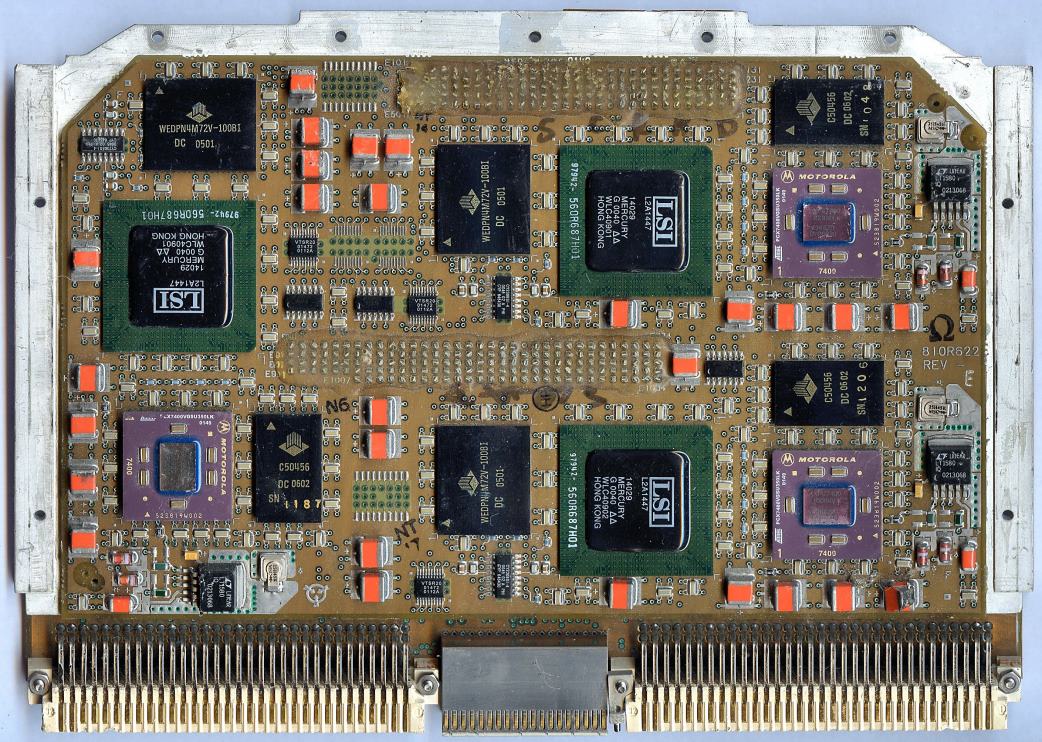

Questa scheda è la versione militare della Mercury MCV6 e monta 4 CPU Motorola PowerPC G4 (Motorola 7400).

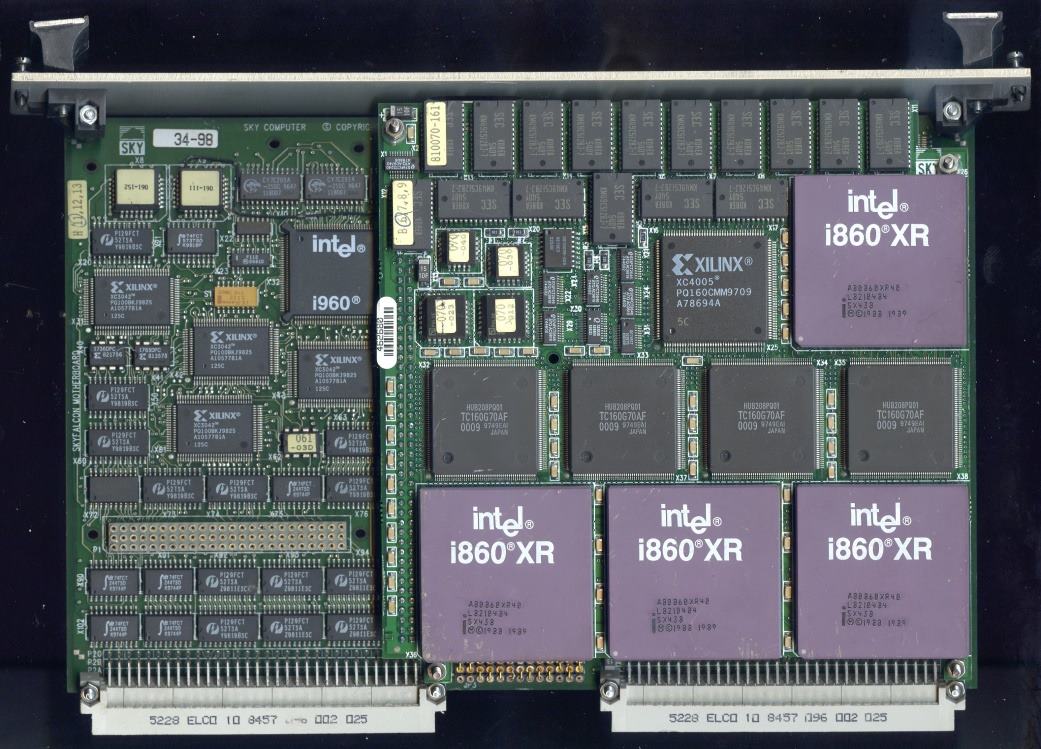

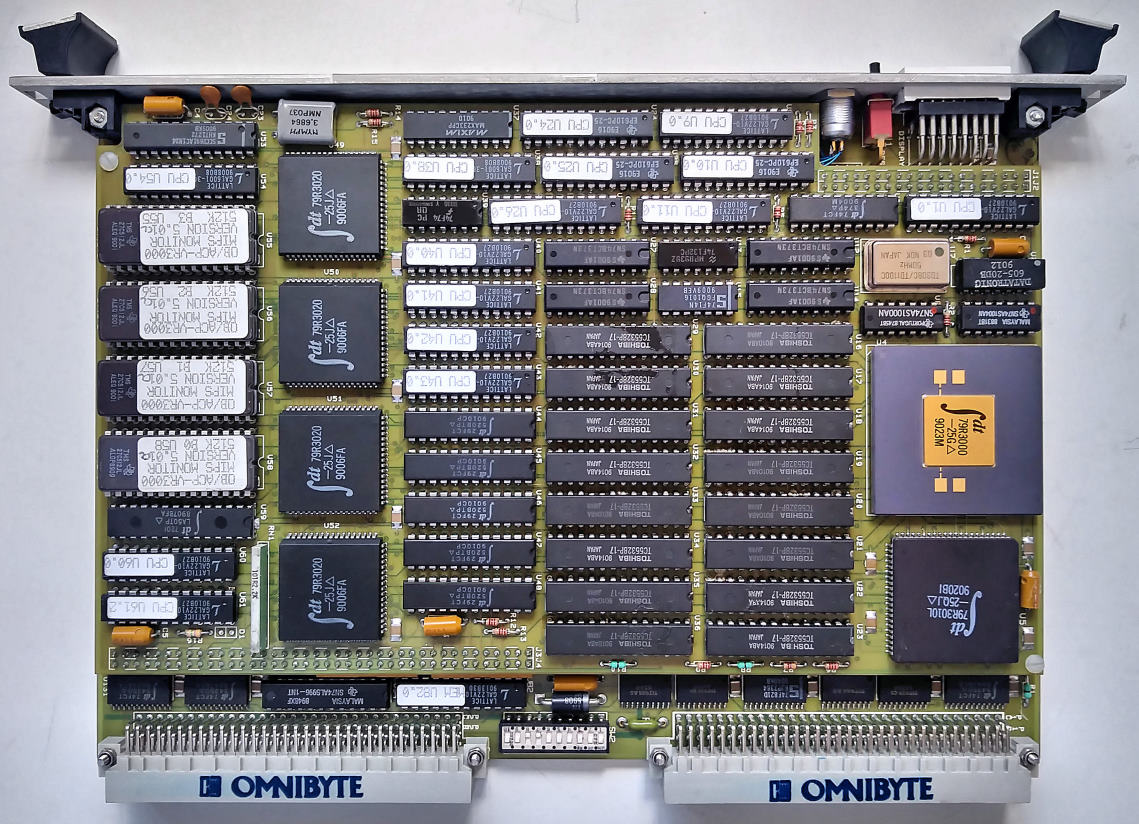

1.9.2015 - Scheda VME SkyFalcon di Sky Computer (1997) con 4 CPU Intel i860XR a 40 MHz.Il processore di controllo è invece un i960CA a 25 MHz. Questa scheda è un esempio di "processing platform" ("piattaforma di calcolo") in virgola mobile per applicazioni di elaborazione digitale dei segnali (DSP), elaborazione di immagini, grafica computerizzata. La schiera di 4 CPU potrebbe fornire una capacità di calcolo teorica di circa 160 MFLOPS (40 per processore); in realtà, le prestazioni effettive dei sistemi basati su i860 sono state seriamente limitate dalla forte dipendenza dalla qualità del compilatore, dalla difficile ottimizzazione del codice macchina e da alcuni pesanti limiti architetturali (in particolare la lentezza nel context switching e nella gestione delle interruzioni, entrambi aspetti fondamentali per una moderna CPU di uso generale). La versione XR (N10) fabbricata con processo CMOS a 1 micron è stata la prima ad essere commercializzata nel Novembre 1989, seguita dalla più performante XP (N11) alla metà del 1990, che era invece prodotta con un più avanzato processo CHMOS a 0,8 micron ed implementava un certo numero miglioramenti (cache più ampie, supporto per la cache esterna di secondo livello, bus di sistema più veloce, supporto per il controllo di coerenza della cache nei sistemi multiprocessore) potendo fra l'altro operare a maggiori frequenze di clock, fino a 50 MHz. Come descritto più in dettaglio in questa pagina del sito, la CPU 80860 -presentata più o meno in corrispondenza con l'80486DX, rispetto al quale contiene all'incirca lo stesso numero di transistor, 1,2 milioni- era contraddistinta da alcuni aspetti esclusivi presenti in nessun altro microprocessore commerciale dell'epoca: primi tra tutti la possibilità di eseguire fino a tre istruzioni per ciclo di clock e una micro-architettura di tipo VLIW (Very Long Instruction Word). Storicamente inoltre l'i860 è importante perché, pur non essendo stato la prima CPU RISC messa in commercio da Intel (titolo che per pochi mesi spetta all'i960, all'epoca passato in secondo piano), rappresenta il primo vero progetto di un'ISA alternativa alla x86 sviluppato dalla stessa Intel dopo lo sfortunato tentativo fatto nel 1982 con l'i432. L'i860, che in effetti è un processore a 32 bit con FPU a 64 bit, ha conosciuto un successo commerciale modesto e comunque molto inferiore alle aspettative del produttore: a causa dei difetti di cui si è accennato sopra non si è mai affermato né come CPU per workstation né come processore embedded, ruolo quest'ultimo nel quale ha largamente prevalso il fortunatissimo Intel i960. A parte i supercomputer a parallelismo massiccio iPSC/860 ed Intel Paragon XP/S l'i860 ha trovato applicazione soprattutto nel campo dei processori per elaborazioni numeriche intensive (grafica, DSP, telecomunicazioni), oltre che in un certo numero di schede acceleratrici per varie piattaforme hardware diffusesi soprattutto negli Stati Uniti all'inizio degli anni Novanta. Tra le schede più conosciute basate su Intel i860 ricordiamo la Geometry Engine GE10 per le workstation Silicon Graphics Onyx e le schede VME Mercury e Sky Computer. Ricordiamo anche due particolari schede madri per PC che montano fianco a fianco un 486DX ed un 80860, ovvero la Hauppauge 4860 (vedi questa pagina del mio sito, oppure qui) e l'Olivetti CP486.

Gate array CMOS di LSI Logic appartenente alla famiglia EPIC-90 da 9.000 gate, 1994.

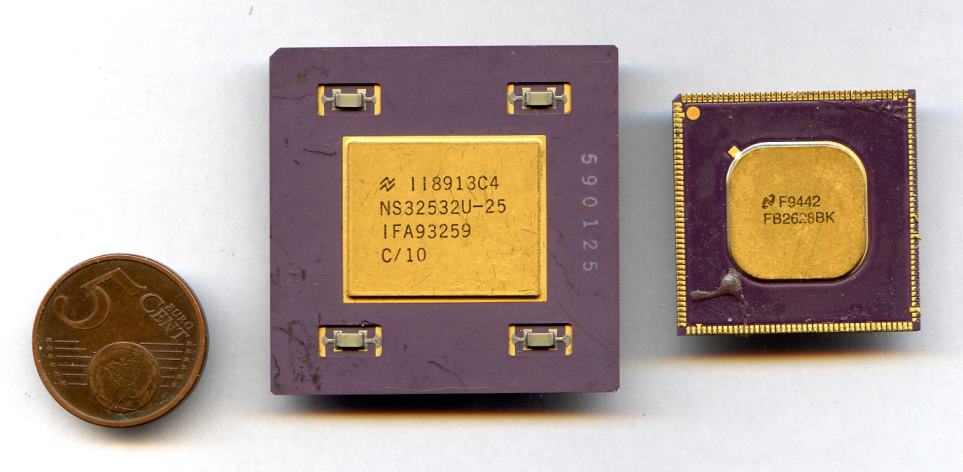

27.5.2016 - A sinistra una CPU National Semiconductor NS32532 a 25 MHz (al suo fianco un ASIC di supporto per la stessa). Si tratta di uno dei membri più recenti della famiglia National NS32000, introdotta nel 1982 e generalmente considerata come la prima serie commerciale di microprocessori a 32 bit apparsa sul mercato. Il 32532 venne presentato all'inizio del 1987; funzionava alle frequenze di 20, 25 e 30 MHz e rappresentava una radicale revisione della microarchitettura dei predecessori, con una pipeline a 5 stadi e cache di primo livello ed MMU integrate. A parità di frequenza di clock le prestazioni risultavano nettamente superiori a quelle dei concorrenti CISC (Intel i386, Motorola 68030) e paragonabili a quelle delle prime CPU RISC commerciali (AMD 29000, Motorola 88000). Questa CPU esiste anche in una versione "ridotta" (32GX532) usata come microcontroller in alcuni modelli di stampanti laser ed apparati di rete. E' storicamente interessante in quanto venne scelta nel 1989 come processore del progetto PC532, uno dei pochi progetti di pubblico dominio di hardware per pesonal computer giunti fino alla realizzazione di macchine (sia pure in numero limitato) effettivamente funzionanti, in questo caso con sistema operativo Minix o NetBSD. Il 32532 rappresenta l'ultimo membro della famiglia NS32000 in quanto il successore designato (32732) non è mai entrato in produzione. E' stato impiegato in alcuni server paralleli fault-tolerant come i Siemens MX300 ed MX500 basati su un'architettura sviluppata da Sequent ed equipaggiati con un massimo di 8 processori. Le versioni più recenti di entrambe le macchine utilizzavano invece processori Intel 486. Il chip visibile qui proviene da una macchina MX300.

Vedi: https://stuff.mit.edu/afs/sipb/contrib/doc/specs/ic/cpu/ns32532.pdf.

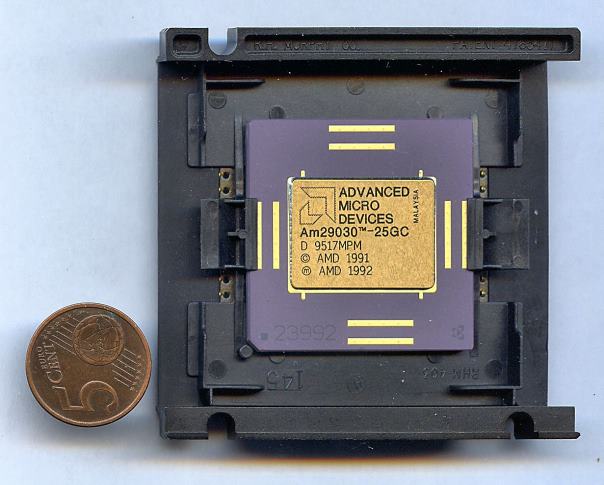

5.9.2016 - CPU AMD Am29030 a 25 MHz (1995). Il 29030 era processore RISC a 32 bit facente facente parte della famiglia AMD 29K; rispetto al 29000 aveva solo due bus anziché tre (per indirizzi, dati ed istruzioni) ed includeva 8 KB di cache dati.

Engineering Sample di microcontroller RISC a 32 bit ad elevata integrazione AMD Am29240 in package PQFP-196, basato sulla microarchitettura della famiglia 29K e derivato dalla CPU 29040.

Integrati Intel in package non finiti (scartati).

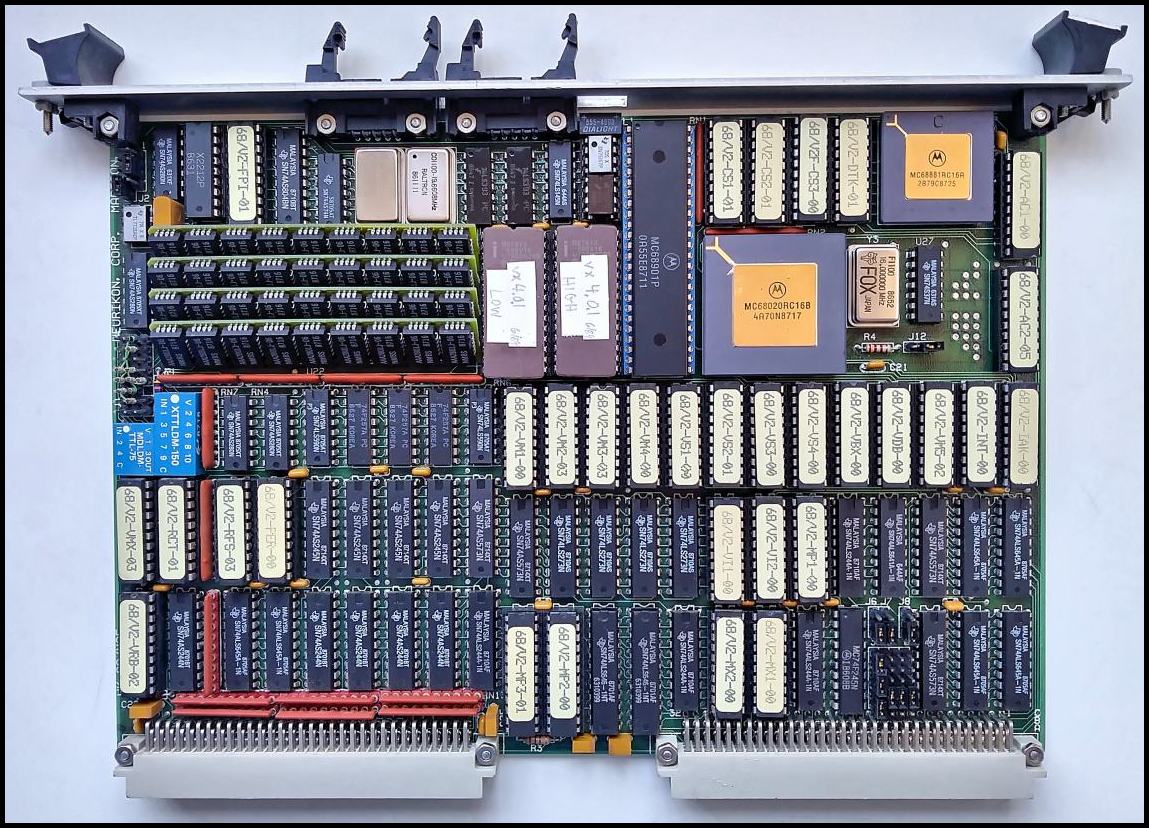

Scheda con CPU RISC Motorola MC88100 a 25 MHz, appartenente alla famiglia 88K (vedi: https://en.wikipedia.org/wiki/Motorola_88100), evoluzione dell'originario 88000, e 2 MMU/controller di cache MC88200.

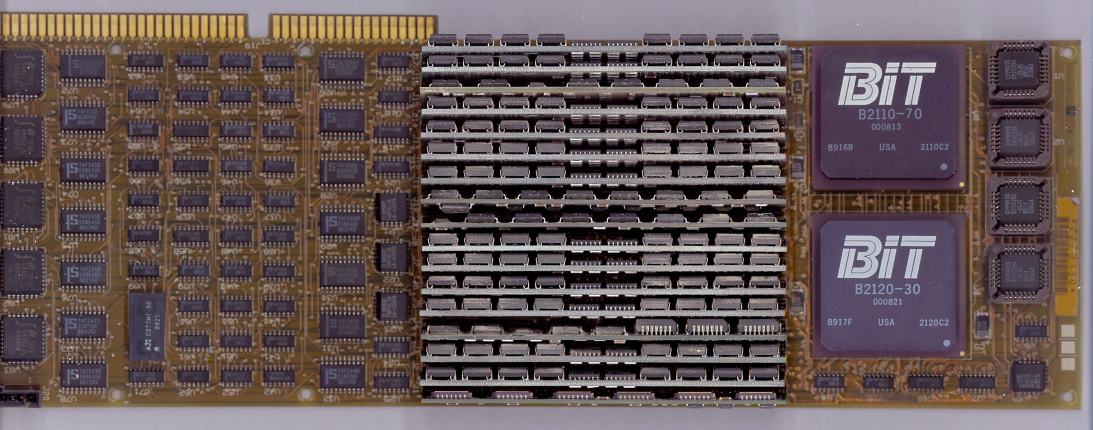

Scheda SAIC Delta-2 (1990, "SAIC" è l'acronimo di Science Applications International Corp.) sulla quale sono montati un moltiplicatore hardware in virgola mobile BIT (Bipolar Integrated Technologies) B2110 ed una ALU in virgola mobile B2120, entrambi fabbricati con tecnologia bipolare ed in grado di operare con un ciclo macchina di 100 ns. I due integrati formano un'architettura di processore di tipo Harvard con pipeline a tre stadi, che offre una prestazione di picco pari a circa 22 MFLOPS. Sulla scheda trovano posto anche 12 MB di memoria RAM locale. La Delta-2 (una scheda ISA che può essere montata su ordinari personal computer con processore 386 o 486 a 20/25 MHz) appartiene alla categoria dei cosiddetti "Neural Network Accelerators" e veniva utilizzata principalmente nella simulazione di reti neurali, come descritto ad esempio qui, facendo uso di software e linguaggi specializzati quali ANSIM ed ANSPEC (vedi). Questo esemplare proviene dall'Università di Lubiana. La coppia moltiplicatore/ALU B2110/B2120 è stata impiegata anche per realizzare l'unità in virgola mobile in alcune delle prime CPU HP PA-RISC (ad esempio la NS-2).

The SAIC Delta Neurocomputer was designed to provide the fastest possible neural network simulation speeds coupled with a general purpose architecture that could be applied to a wide range of applications. This required several architectural innovations in addition to the use of state of the art digital design and board layout and packaging techniques. The design incorporated an ultra-high-speed floating point chip set capable of both 32- and 64-bit floating-point and integer calculations. The chip set was embedded in a multistage pipeline architecture with many parallel data paths to minimize operand fetch and store times. Delta memory was designed to make use of 1 megabit DRAMs operating in static column mode for a very large (12 megabyte) and very fast (55 ns) memory for weights, activations, and programs. With this architecture the Delta can simultaneously fetch 2 floating point operands, multiply the last pair fetched, and accumulate the previous product for bursts of 1024 operands at 91 ns each. The Delta was targeted for the desktop simulation market with optional expansion into the multiprocessing arena. (https://www.researchgate.net/publication/255063399_The_SAIC_delta_neurocomputer_architecture)

Vedi: https://commons.wikimedia.org/wiki/File:BIT_B2110_die.jpg.

La ALU B2120 è descritta brevemente qui: http://www.cpushack.com/tag/alu/.

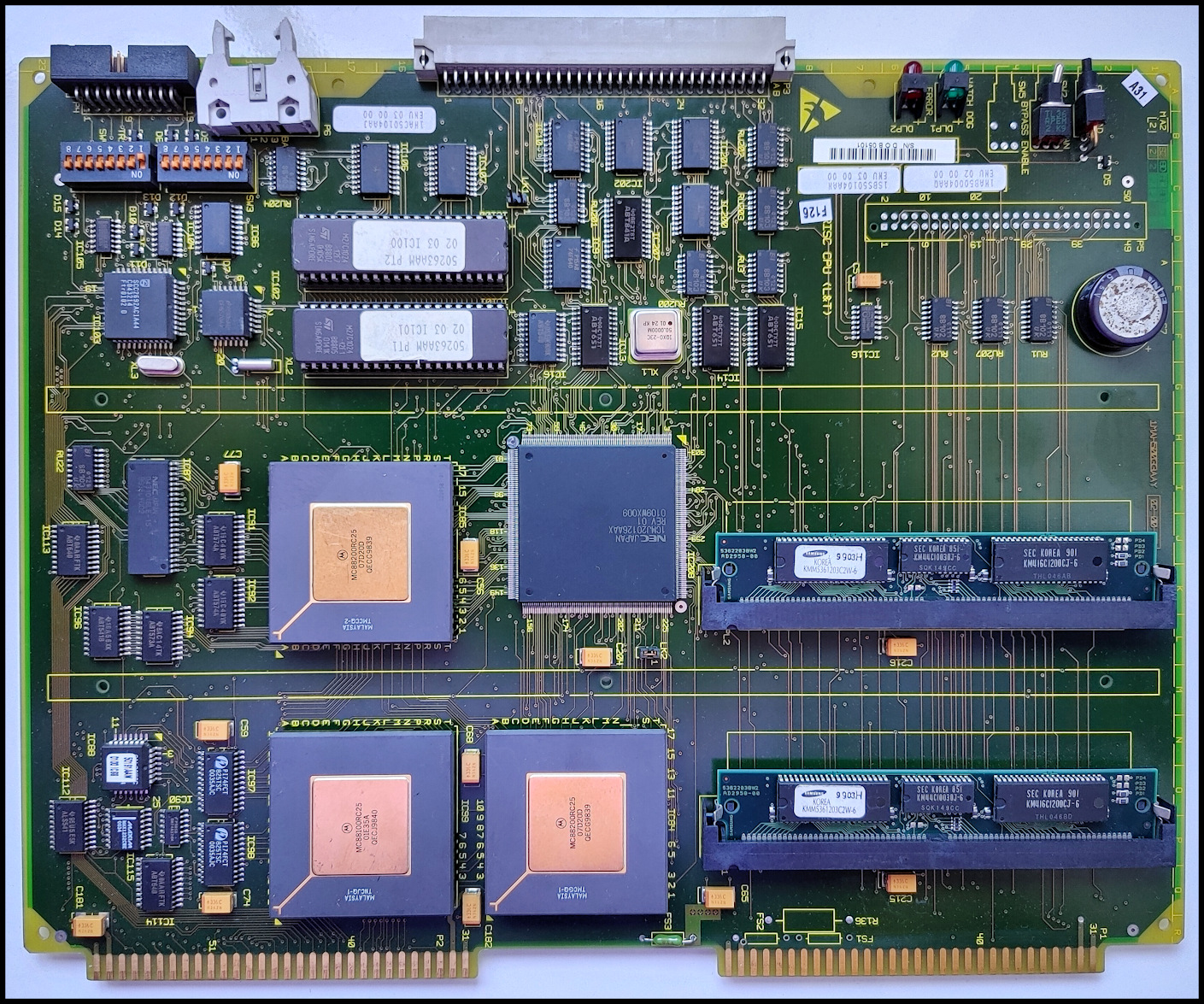

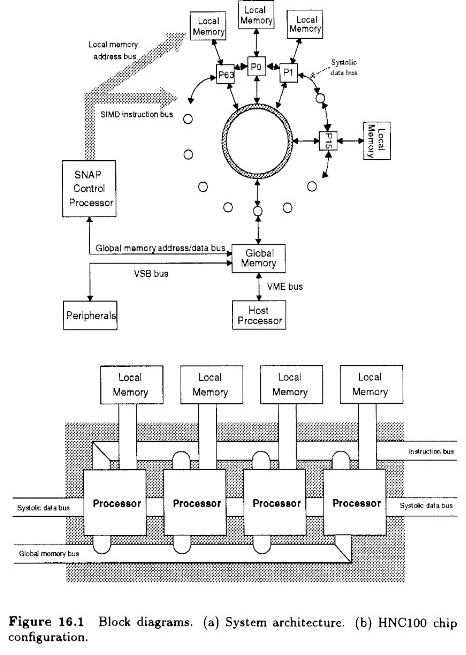

Scheda VME HNC SNAP (SIMD Numerical Array Processor), 1993, un processore SIMD per la simulazione di reti neurali scalabile fino a 256 elementi di calcolo ed adattabile anche ad altre applicazioni di calcolo parallelo (calcoli matriciali, elaborazione di immagini, FFT...). HNC è la sigla di Hecht-Nielsen Neurocomputers. La massima velocità di calcolo era di circa 2,56 GFLOPS. Gli ASIC sono gate array LSI Logic siglati "HNC100 SIMD Neuro Array Proc" (L1A6463), fabbricati con tecnologia CMOS da 1 micron. La HNC SNAP venne presentata nel 1993 e in quello stesso anno vinse il premio Gordon Bell della IEEE per la piattaforma di calcolo parallelo e simulazione di reti neurali col miglior rapporto prezzo/prestazioni. L'unità di elaborazione, formata da una o più schede come questa, era controllata da una workstation Unix (Sun SPARCstation). Ciascun chip HNC100 contiene 4 elementi di calcolo, ognuno formato da una ALU a 32 bit accoppiata ad un moltiplicatore in virgola mobile in standard IEEE-754-1985. La ALU ed il moltiplicatore operano in parallelo e possono accedere alla memoria locale, a quella globale e comunicare con le unità di calcolo poste sullo stesso chip così come con quelle nei chip contigui. Il controllo delle schede che contengono gli elementi di calcolo è affidato ad una scheda VME separata che genera e coordina le microistruzioni da inviare alle singole unità. La comunicazione bidirezionale tra unità di controllo e schede di calcolo avviene tramite un bus locale che utilizza il connettore bianco visibile nella parte superiore centrale della scheda. Il bus VME viene invece utilizzato per la comunicazione con la workstation host. Un'installazione HNC SNAP con 4 schede implementava 256 elementi di calcolo (dunque con 64 chip HNC100) ed occupava lo spazio di un normale PC dei primi anni Novanta (vedi). Le prestazioni erano simili a quelle del supercomputer Cray Y-MP 8, ad una frazione però del costo di quest'ultimo. Ad esempio una piattaforma HNC SNAP con 256 elementi poteva eseguire una trasformata di Fourier 512x512 in due dimensioni in circa 23 millisecondi. Una tipica configurazione della piattaforma SNAP per la simulazione di reti neurali (SNAP Neurocomputer) comprendeva 2 schede per un totale di 8 chip HNC100 e 64 unità di elaborazione, ed era controllata da un normale PC nel quale era installata la scheda di interfaccia HNC Balboa (vedi). Qui si può trovare una comparazione di varie piattaforme di simulazione di reti neurali dei primi anni Novanta, con le relative prestazioni (vedi anche questo link).

Architettura della piattaforma SIMD HNC SNAP e, in basso, di un chip HNC100.

Vedi: ftp://ess.r-project.org/Doc/Neural/FAQ7.html.

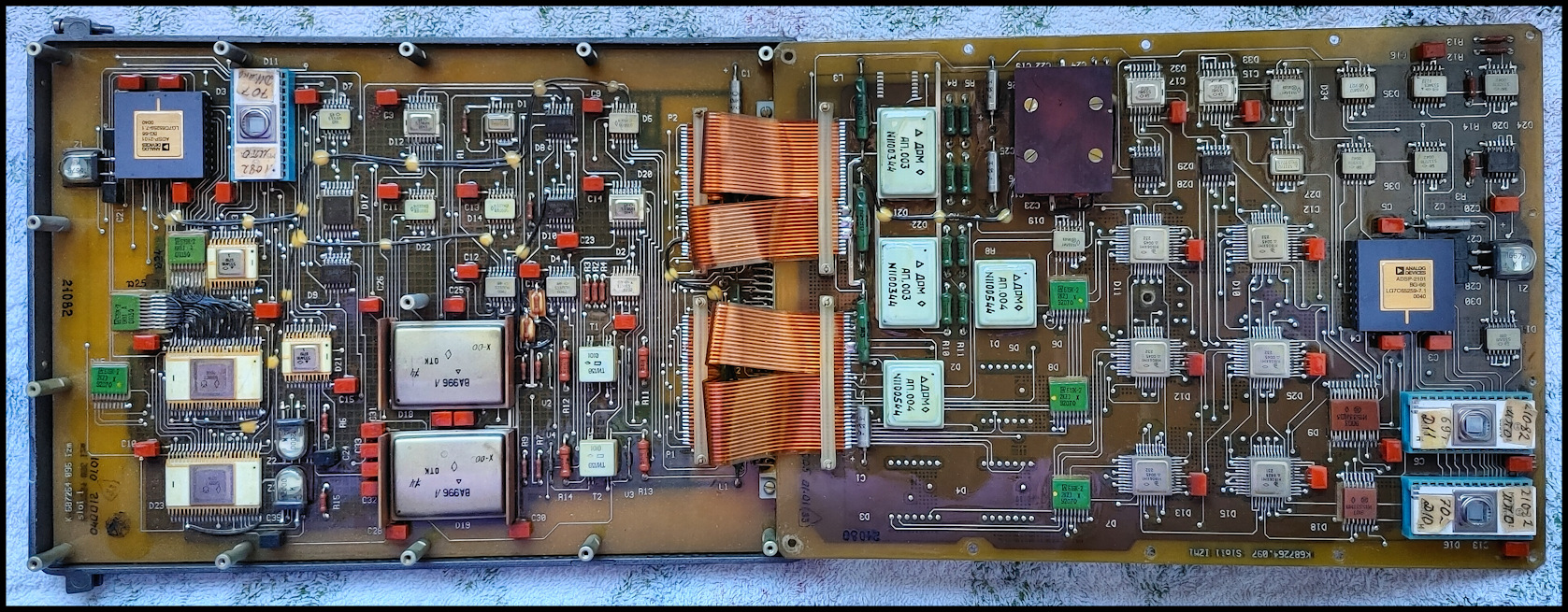

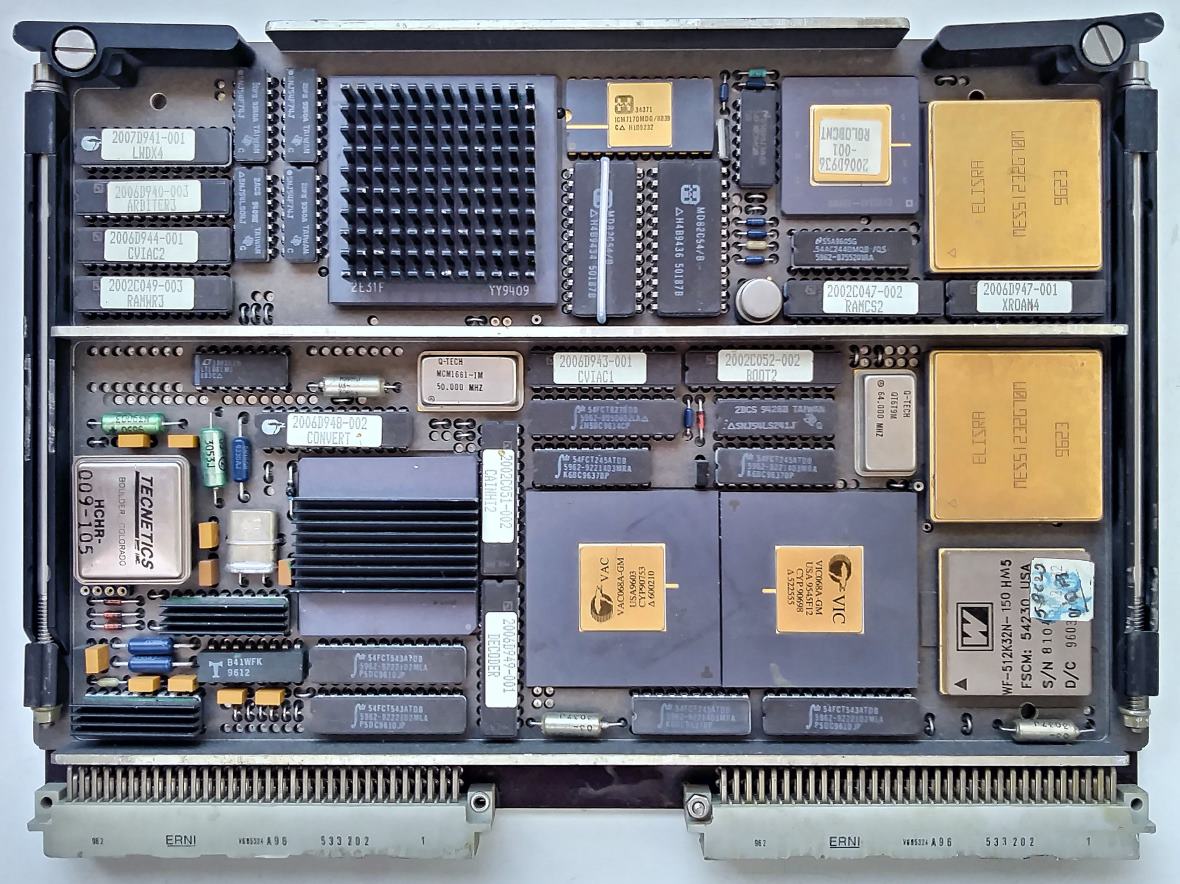

Modulo proveniente da avionica russa, probabilmente dal computer di bordo o dal processore radar d'attacco di un cacciabombardiere MIG-35, fine anni Novanta/circa 2000. Contiene 2 DSP Analog Devices 2101 (a 16 bit, fixed-point: vedi) e vari componenti in package "sovietici", rimasti in uso ben oltre il 2000, tra cui EPROM e circuiti ibridi di diverso tipo. Dimensioni circa 25×16 centimetri (circa 50 cm le due schede affiancate). E' una interessante mescolanza di componenti "occidentali" e di "oltrecortina".

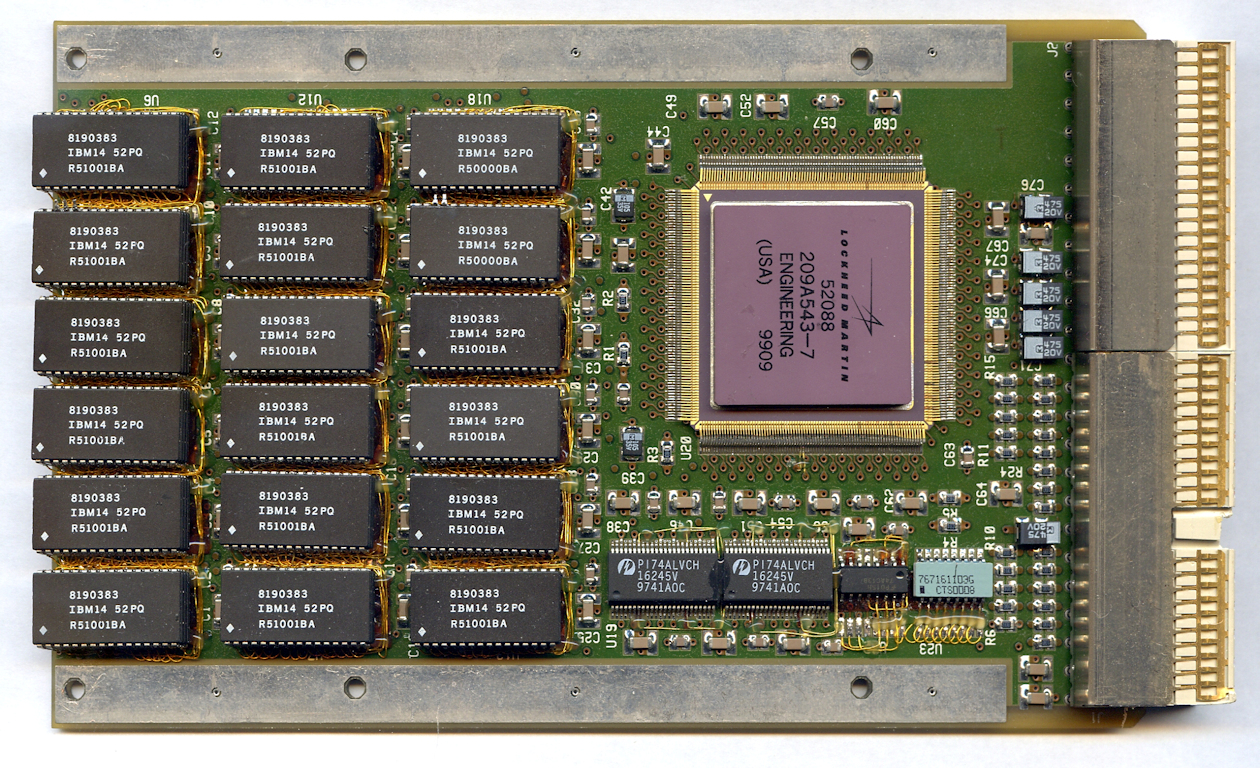

Scheda prototipo di avionica (militare?) con memorie IBM e, a destra, engineering sample di ASIC radiation-hardened per applicazioni aerospaziali fabbricato probabilmente da IBM per Lockheed Martin (1999).

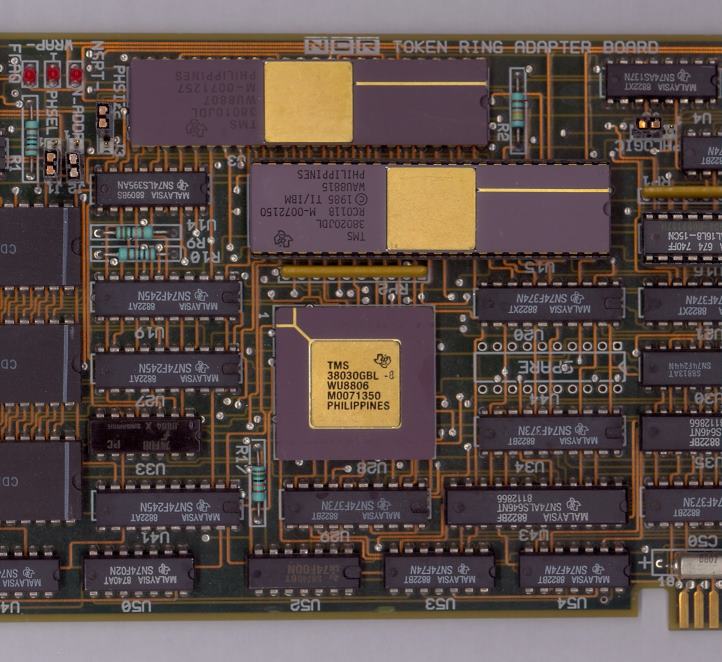

Dettaglio di scheda Token Ring 4 Mbps NCR con chipset Texas Instruments TMS380. Quest'ultimo risulta composto da cinque chip e riproduce le funzionalità dei chip sviluppati da IBM per i propri adattatori Token Ring: il Communication Processor (CP) TMS38010 (in effetti un microprocessore CMOS a 16 bit), il Protocol Handler (PH) TMS38020, il controller di DMA TMS38030 e, non visibili qui, i chip di interfaccia (Ring Interface) TMS38051/38052.

Scheda Nubus Apple TokenTalk con chipset IBM/Texas Instruments TMS380.

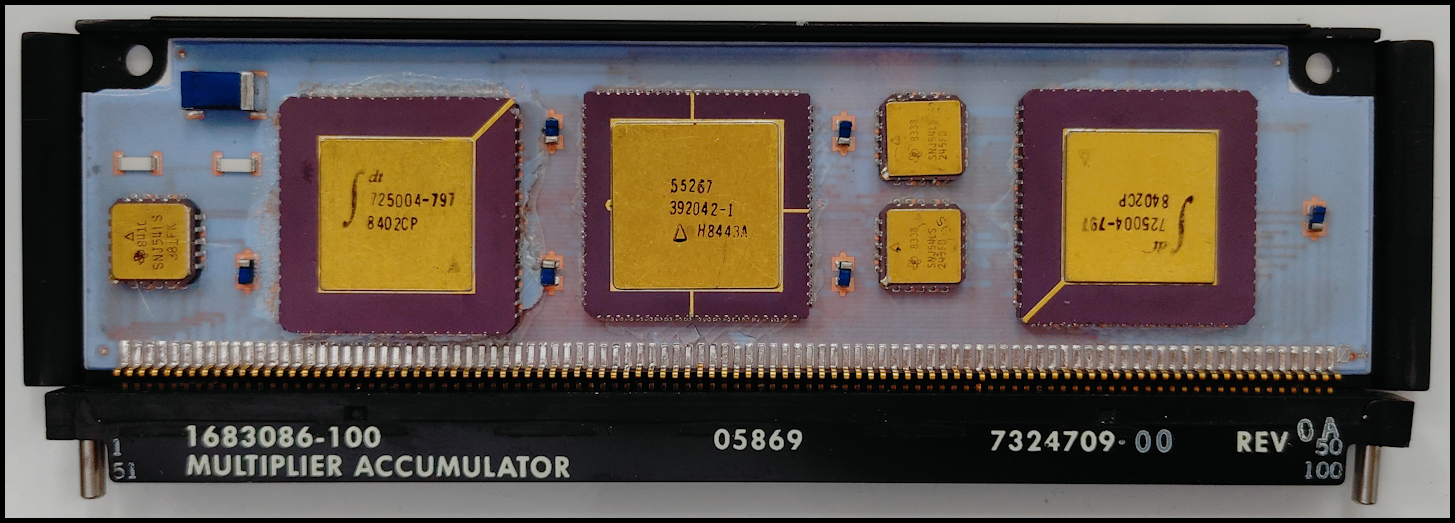

6.5.2015 - Scheda Evans & Sutherland, proveniente da un Image Generator ESIG-1000 del 1990, con coppia di moltiplicatori hardware a 32 bit Texas Instruments SN74ACT8836GB e vari ASIC LSI Logic. L'8836 è un moltiplicatore/accumulatore (MAC) veloce per numeri interi (integer) a 32 bit che fornisce risultati a 64 bit; può essere utilizzato sia in supporto ad un ordinario microprocessore a 16/32 bit con una limitata quantità di logica addizionale (glue-logic), sia come unità indipendente, soprattutto nelle applicazioni di elaborazione digitale dei segnali, brevemente DSP. Più 8836 possono essere collegati in cascata per formare moltiplicatori in grado di trattare dati a 64 o più bit. Fabbricato da Texas Instruments con processo CMOS EPIC a 1 micron, l'8836 è in grado di effettuare una moltiplicazione completa di due interi a 32 bit in un tempo massimo di 60 ns; due interi a 64 bit possono essere a loro volta moltiplicati con un impegno massimo di 5 cicli-macchina. Questo integrato può anche effettuare la divisione in hardware di interi a 32 o 64 bit utilizzando il metodo di approssimazione di Newton-Raphson. Contiene un registro accumulatore a 64 bit ed è dotato di 3 bus separati, uno per il moltiplicando, uno per il moltiplicatore ed il terzo per il prodotto.

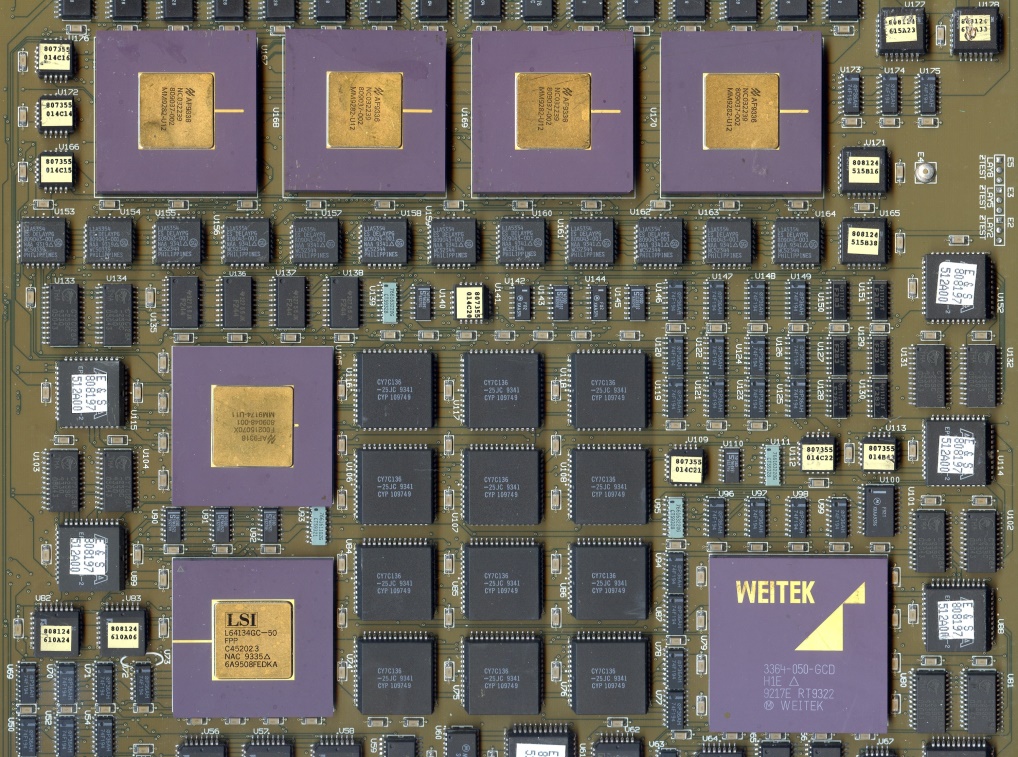

Scheda Evans & Sutherland proveniente dalla medesima macchina cui apparteneva la scheda precedente, contenente un processore in virgola mobile implementato con ASIC CMOS National Semiconductors, una FPU a 32/64 bit LSI Logic L64134GC-50 in basso a sinistra ed una FPU Weitek 3364-050-GCD (in basso a destra). Il 3364 "Floating Data Path" (FDP), in sostanza un'ALU single-chip in virgola mobile, era per l'epoca in cui venne introdotto (1988) un chip molto veloce: alla frequenza massima di 60 MHz era capace di eseguire operazioni di addizione/moltiplicazione tra numeri a 64 bit alla velocità di circa 32 MFLOPS, e raggiungeva i 50 MFLOPS di picco nelle operazioni con dati a 32 bit. Ciononostante era caratterizzato da un rapporto qualità/prezzo favorevole, che ne ha fatto un componente molto diffuso nelle applicazioni DSP, di elaborazione di immagini ed in generale scientifiche e nel campo della ricerca applicata fino alla metà degli anni Novanta. Questo chip è descritto in dettaglio nel classico libro di Hennessy e Patterson Computer Architecture: A Quantitative Approach. Il 3364 è stato una delle prime FP-ALU commerciali completamente compatibili con lo standard IEEE-754. Disponibile con diverse velocità operative (ciclo da 40, 50, 60, 75 e 100 ns), era fabbricato con processo CMOS ed integrava in un unico chip VLSI tutti gli elementi necessari alla realizzazione di una FPU a 32/64 bit: l'unità logico/aritmetica, un moltiplicatore, un'unità per la divisione e l'estrazione di radice quadrata in hardware, 32 registri a 64 bit organizzati in un register file a 6 porte, ed infine la necessaria logica di controllo. Weitek ne produsse anche una versione a 32 bit conosciuta come 3164 ed altrettanto diffusa. Il 3364, contenuto in package ceramico PGA a 168 pin, è dotato di 3 porte a 32 bit, due per l'input, di cui una bidirezionale, ed una per il risultato (output); può essere usato in configurazione con 3 bus indipendenti a 32 bit oppure con un singolo bus a 64 bit. Il "fratello minore" 3164 ha invece 1 sola porta di input bidirezionale, sempre a 32 bit. Fu progettato da Weitek per le applicazioni scientifiche, tecniche ed ingegneristiche in cui fossero importanti sia le prestazioni in termini di calcoli al secondo (FLOPS) che il volume di dati elaborati (throughput). Idealmente questa FPU può essere associata all'unità di elaborazione per interi a 32 bit (IPU) Weitek XL-8137 con il relativo chip di controllo XL-8136: si ottiene così un processore completo con bus dati a 64 bit identificato da Weitek con la sigla XL-8364 (XL-8164 nel caso in cui la FPU sia il 3164). Nulla vieta però di associare il 3364 a processori oppure ALU integer di terze parti. Sulla scheda visibile qui è presente un'altra ALU floating-point single-chip dell'inizio degli anni Novanta, la meno conosciuta (rispetto al 3364) LSI Logic L64134. Questo componente, derivato dal predecessore L64133 rispetto al quale introduceva la piena compatibilità con lo standard IEEE-754, integrava un'ALU in virgola mobile a 32 bit, completa, associata ad un moltiplicatore hardware veloce a 32/64 bit in un unico chip PGA a 144 piedini. Fabbricato con processo HCMOS a 1 micron, il 64134 aveva prestazioni di picco a 32 bit paragonabili a quelle del Weitek 3164. Anche l'architettura interna era molto simile, così come le applicazioni tipiche (DSP, elaborazione d'immagine, workstation scientifiche). La parte centrale della scheda contiene 12 SRAM Cypress a due porte (dual-ported SRAM) da 2Kx8, 25 ns, in package PLCC a 52 pin.

Vedi: http://www.datasheetarchive.com/dl/Scans-091/DSAHI000178031.pdf (Weitek 3364), http://www.datasheetarchive.com/dl/Scans-061/DSA2IH0080647.pdf (L64134).

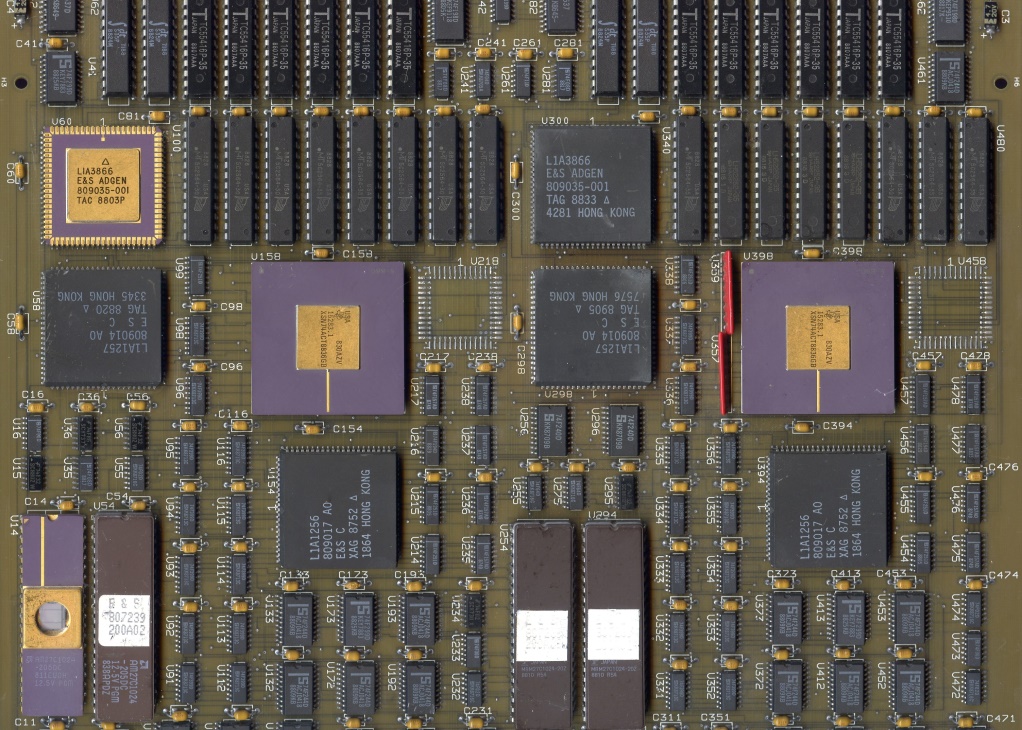

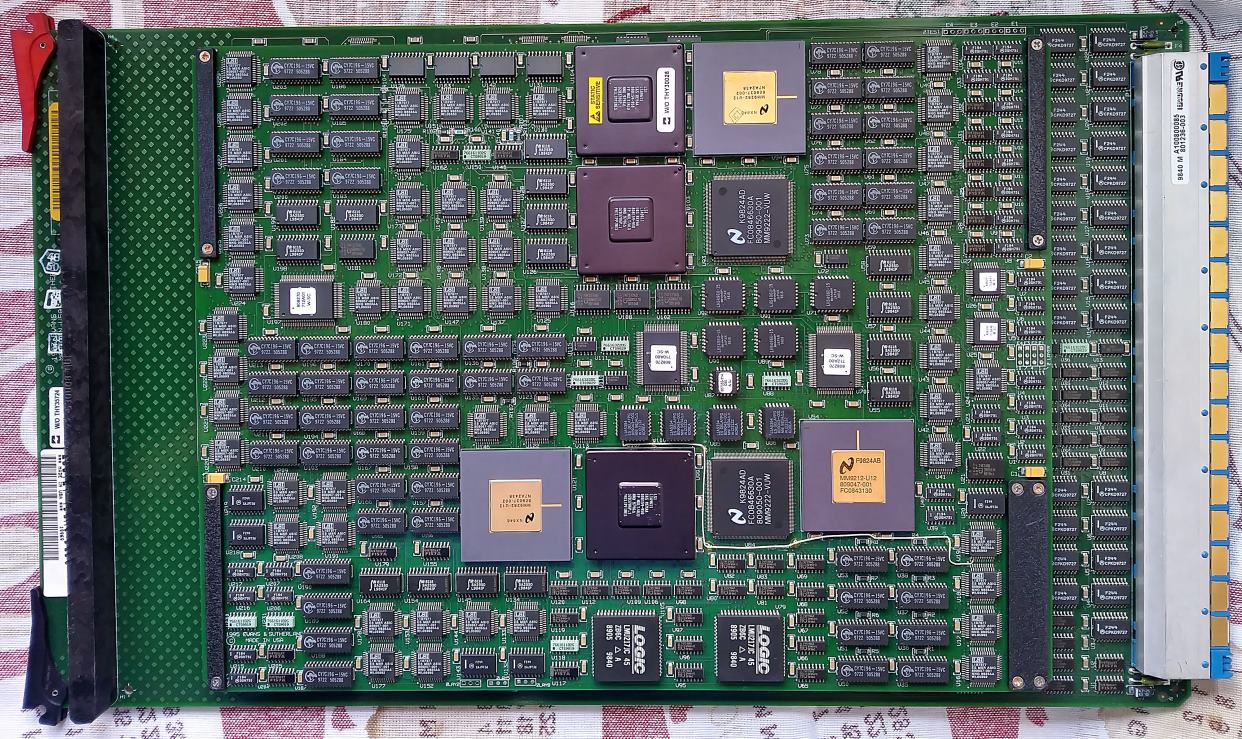

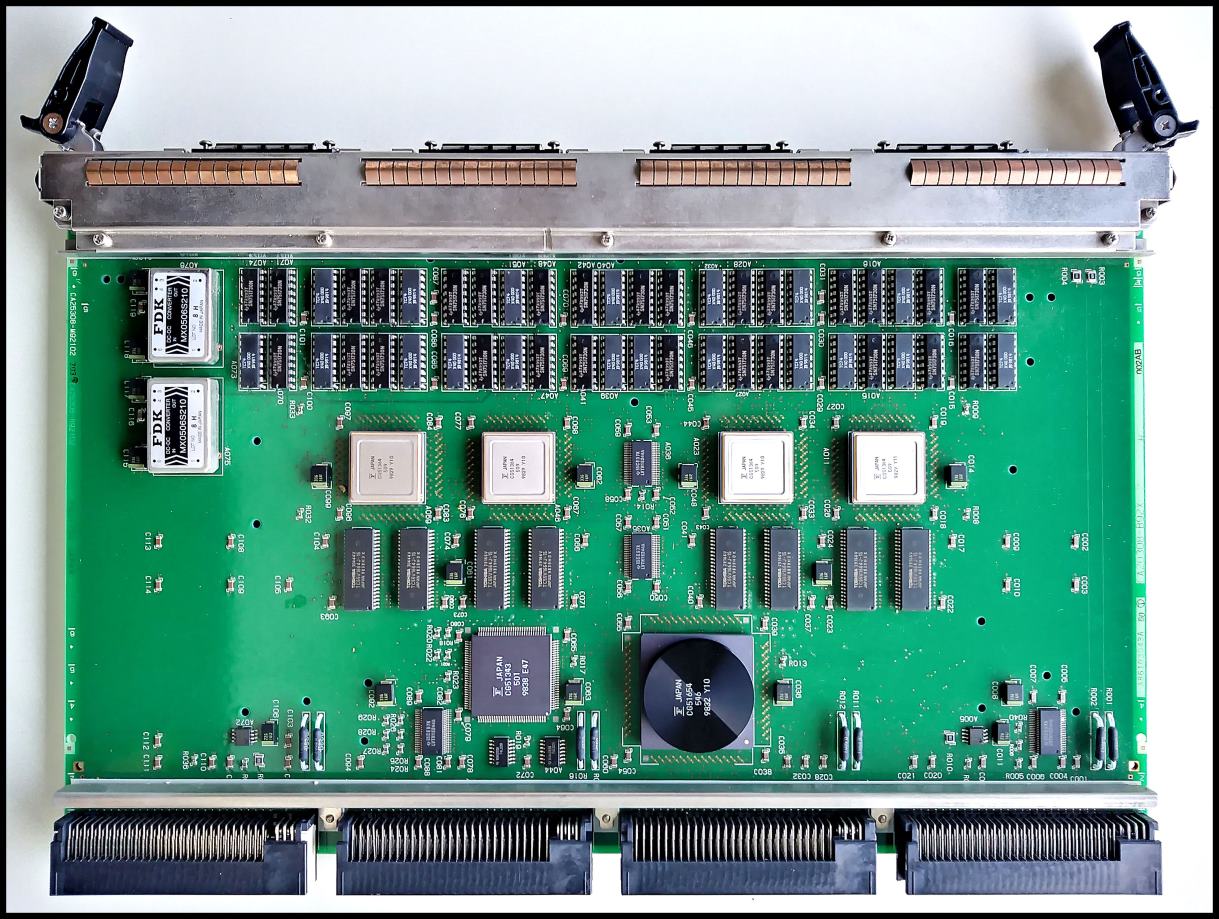

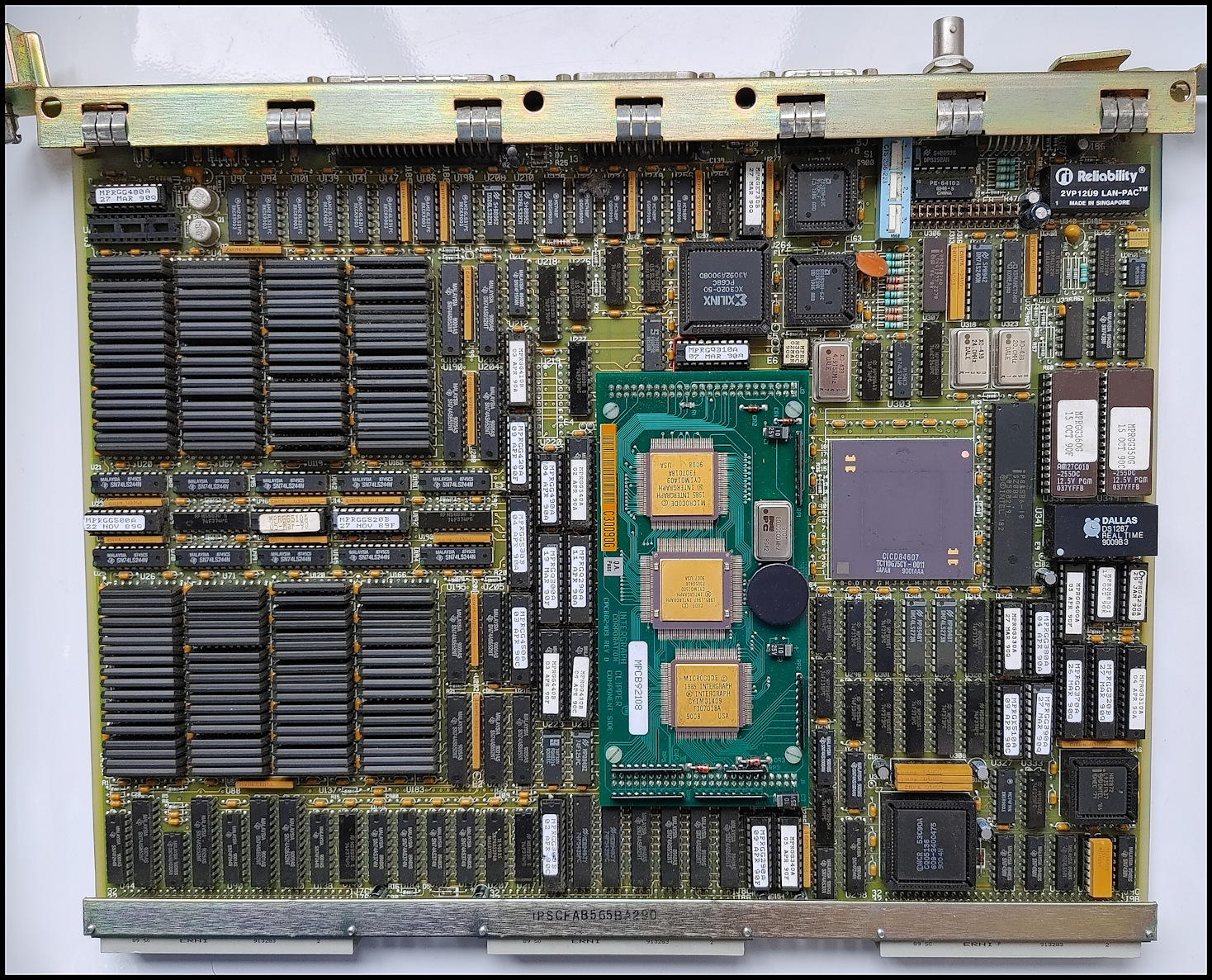

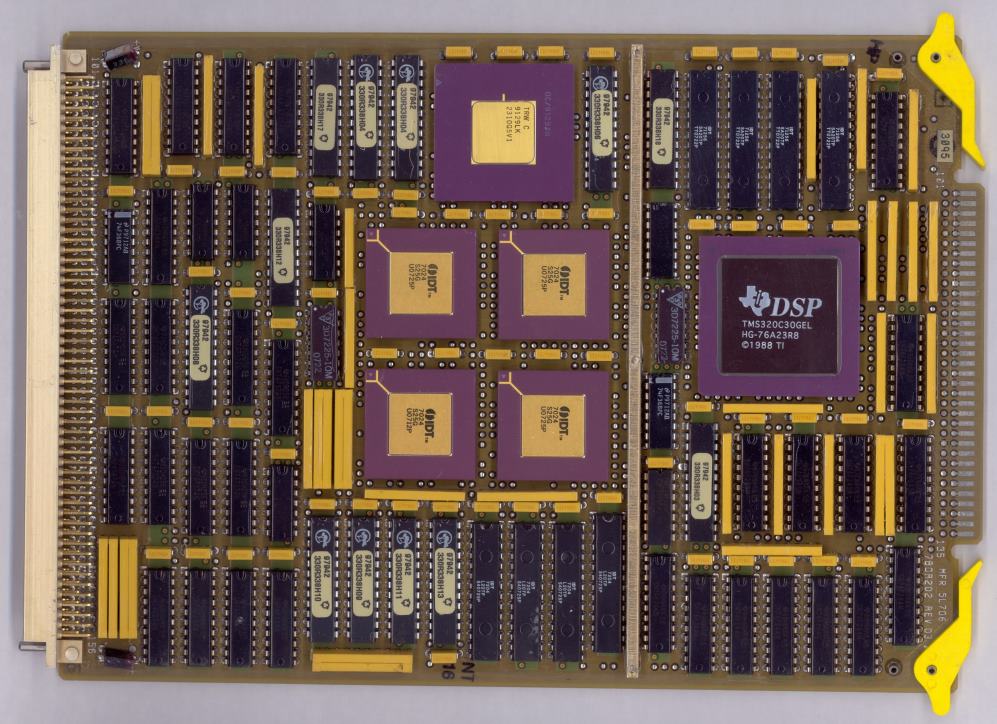

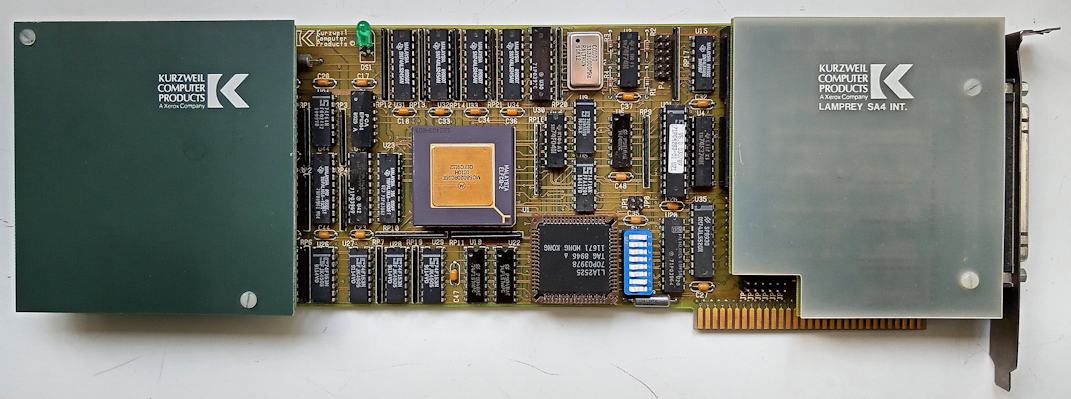

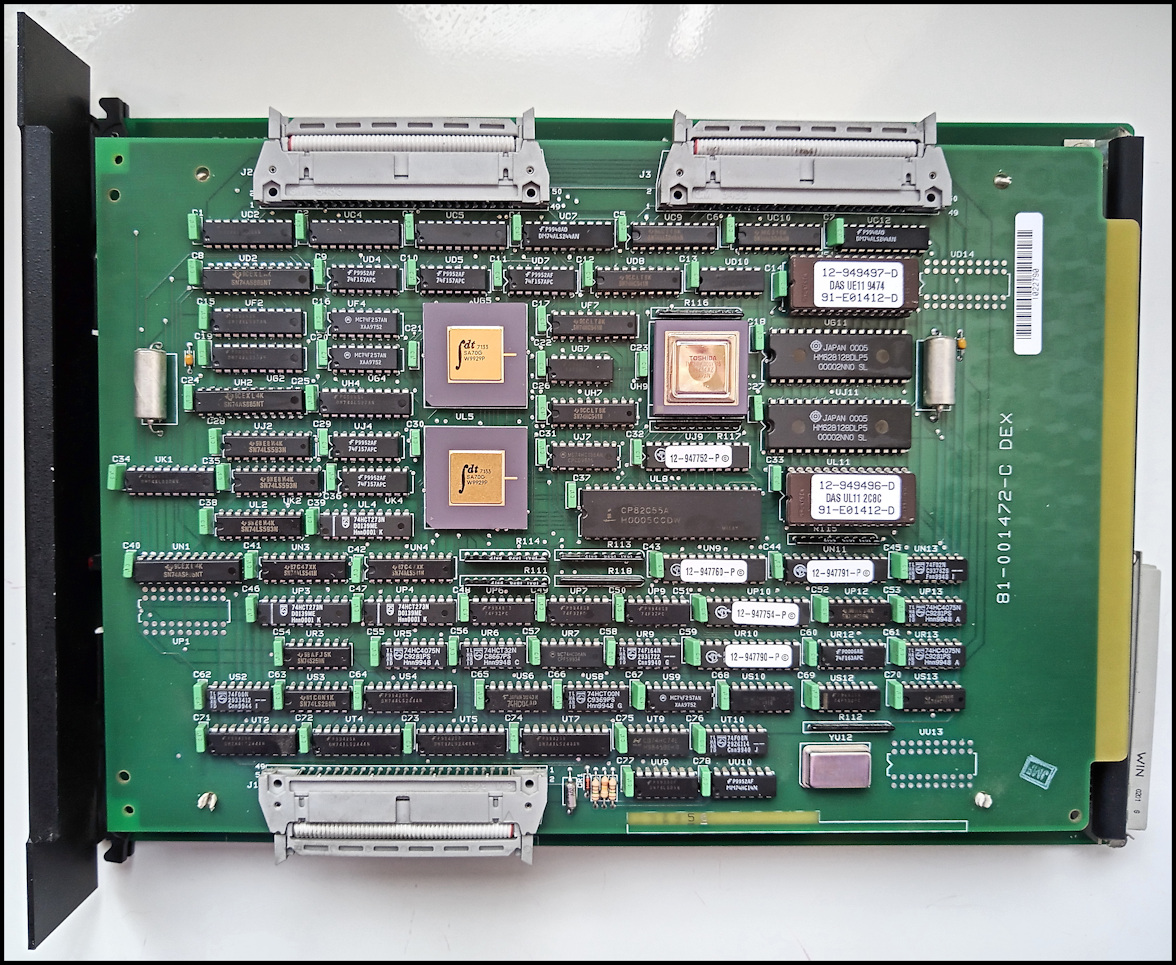

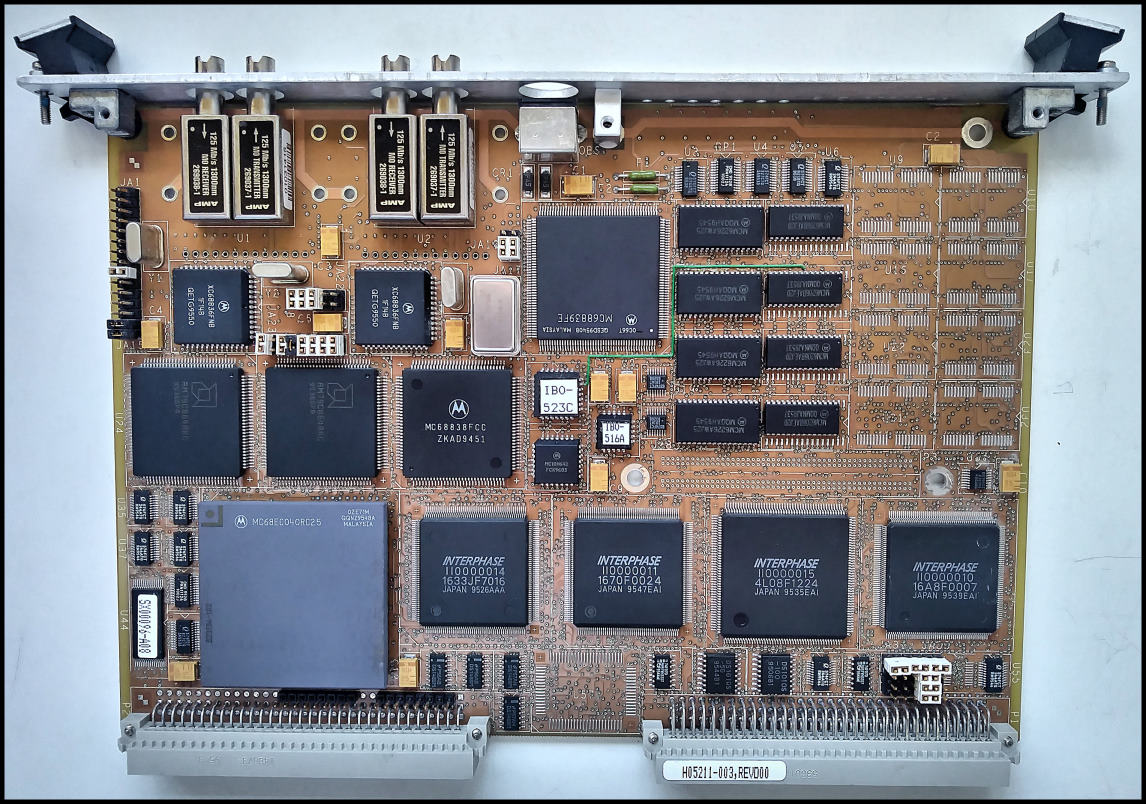

Scheda Vector Scanner con ASIC LSI Logic e National Semiconductor proveniente da una macchina Evans & Sutherland ESIG-3000 (1993, la scheda è del 1997), un generatore di immagini fotorealistiche ad alta risoluzione -in parole povere un processore grafico 3D- impiegato in diverse applicazioni nel corso degli anni Novanta come ad esempio simulatori di volo ed ambienti di realtà virtuale. Gli ASIC LSI Logic sono ALU/moltiplicatori 32×32 in virgola fissa. La potenza di calcolo è di circa 60 MIPS. Qui è visibile un'applicazione dell'ESIG-3000 da parte della NASA.

Vedi: http://www.iasa.com.au/folders/Publications/pdf_library/ospreypdfs/ar93.pdf (applicazioni dell'ESIG-3000 in simulatori di volo)

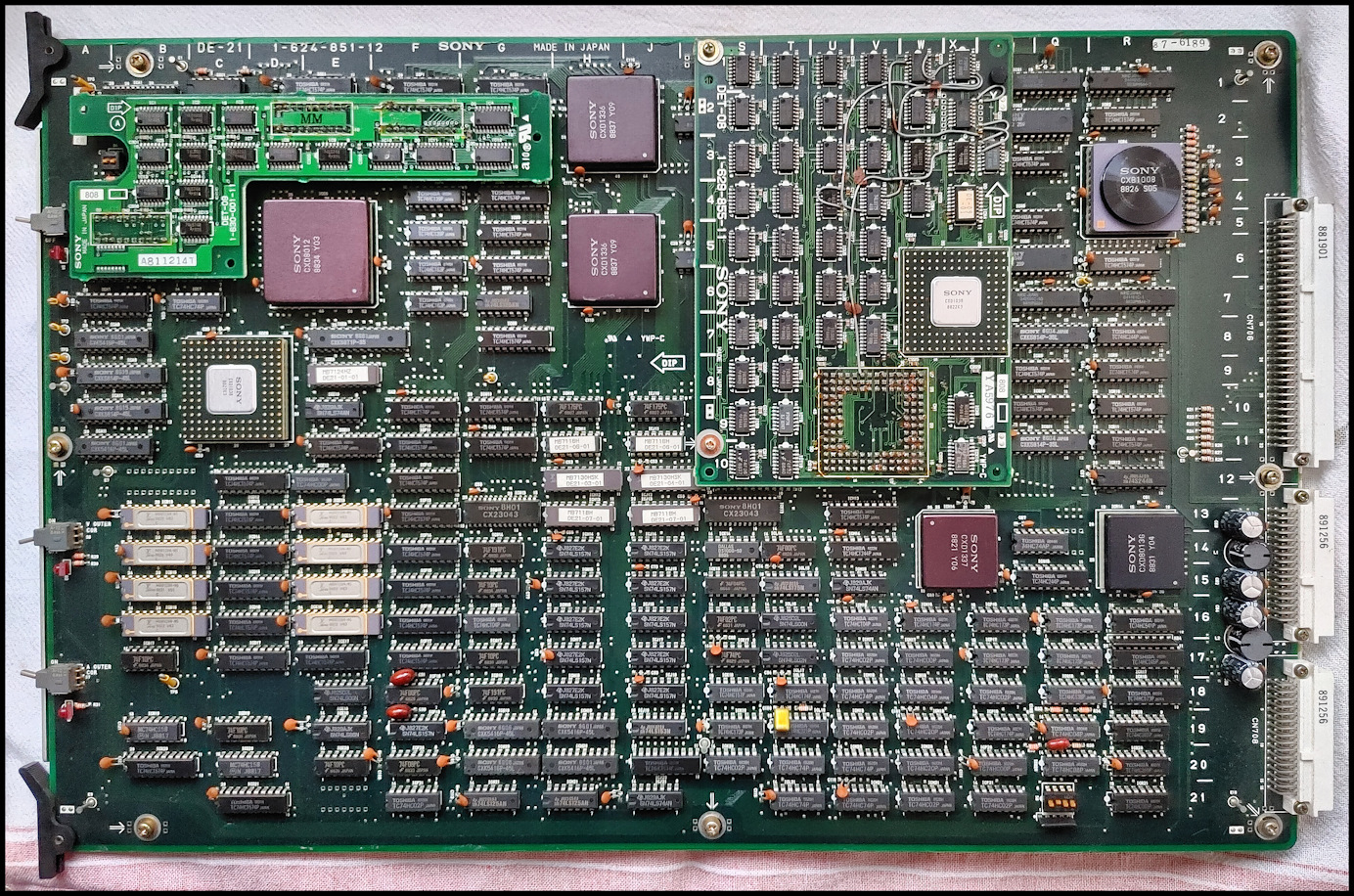

Scheda logica di videoregistratore professionale Sony realizzata con gate array LSI TTL e CMOS (1988).

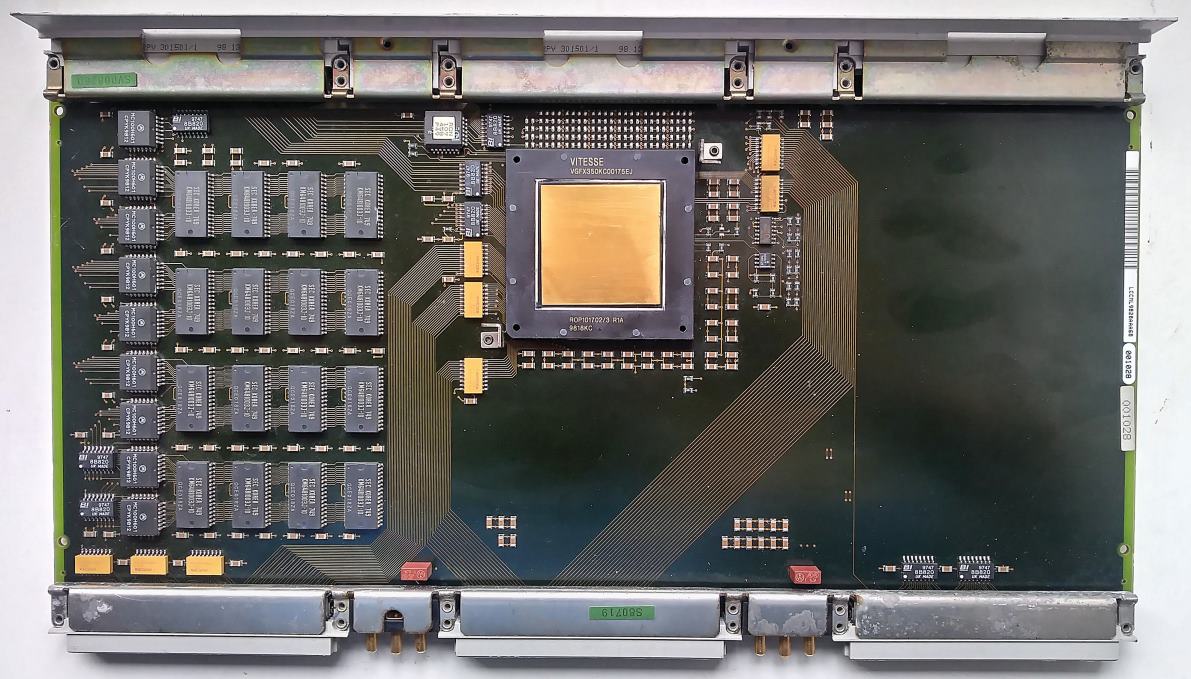

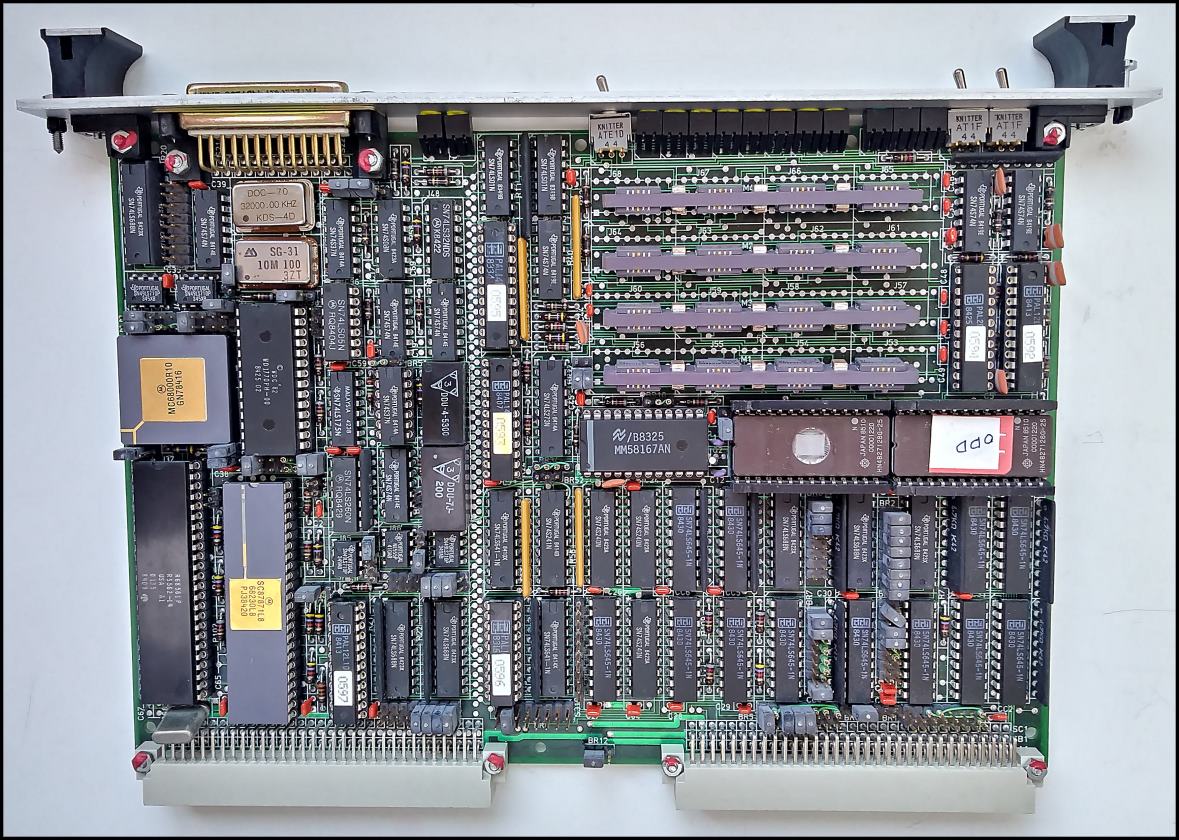

Scheda di centrale telefonica Ericsson con gate array all'Arseniuro di Gallio da 350.000 porte NAND equivalenti, 50 ns, Vitesse VGFX350.

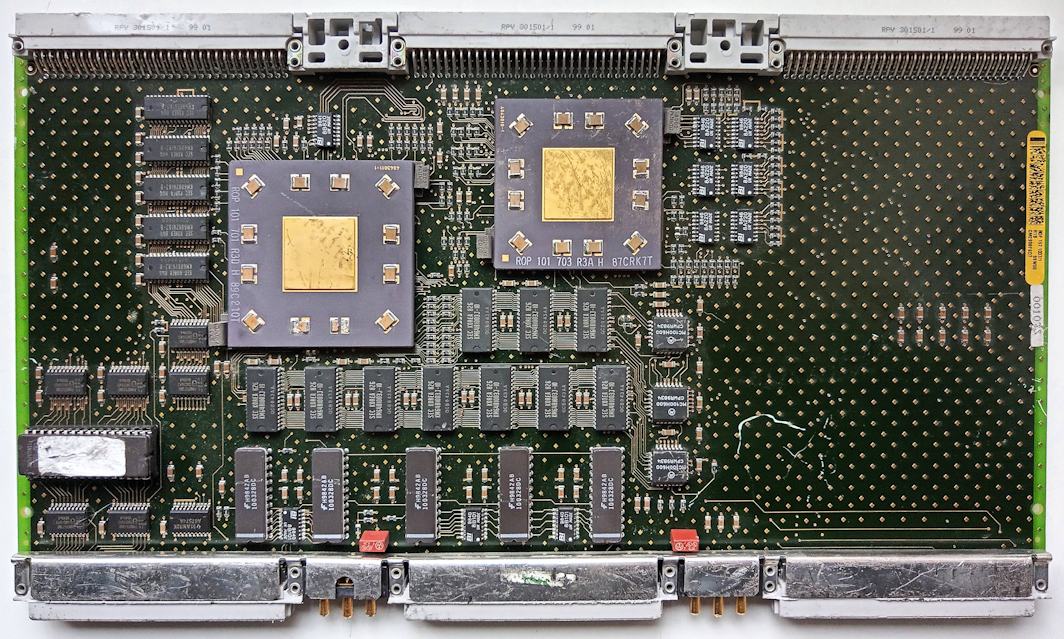

Scheda proveniente dallo stesso tipo di apparato con gate array CMOS della Texas Instruments (1997).

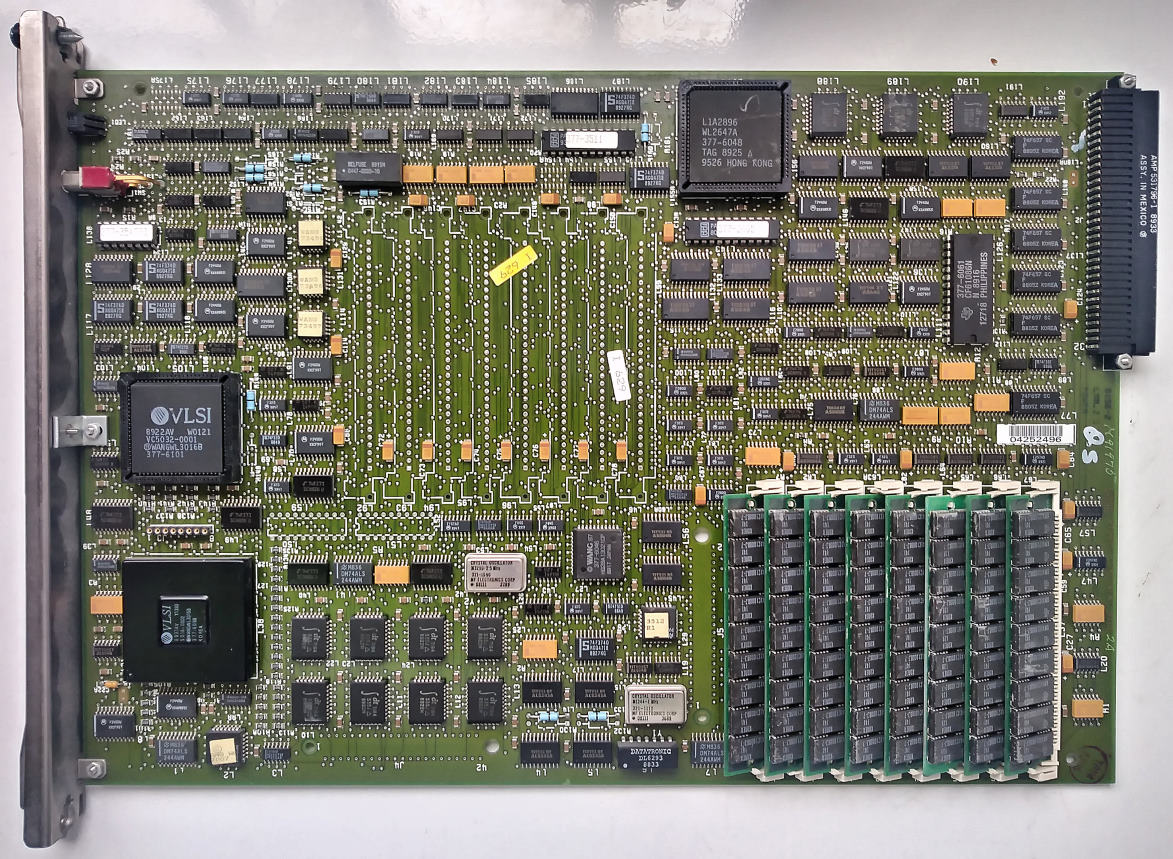

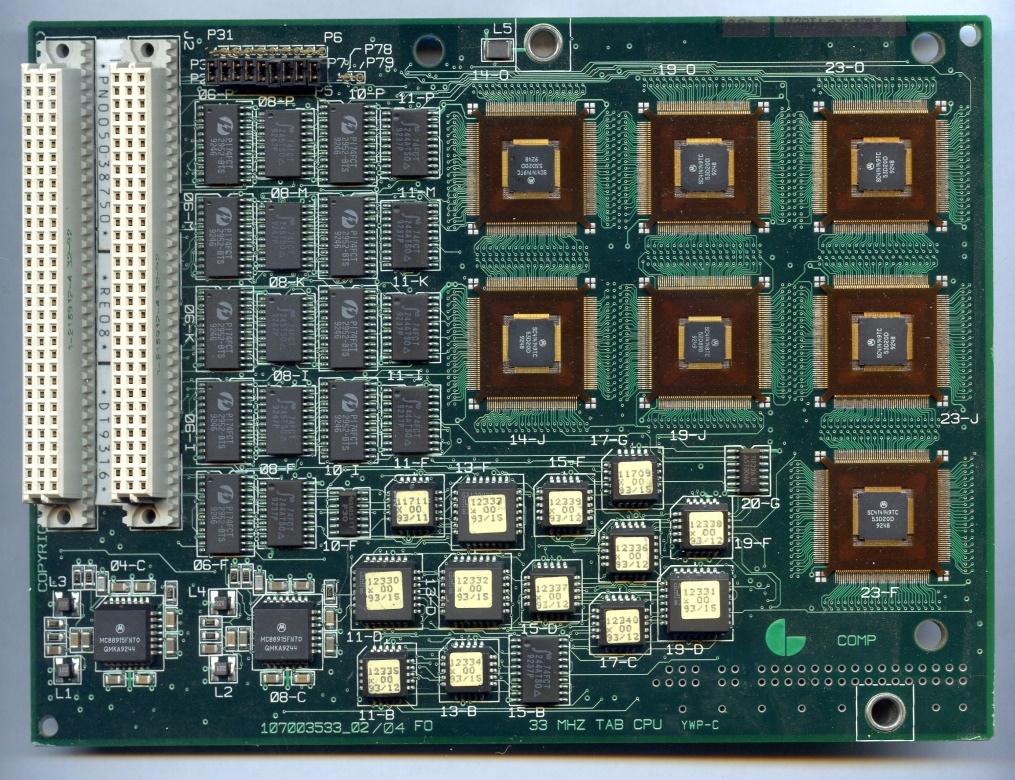

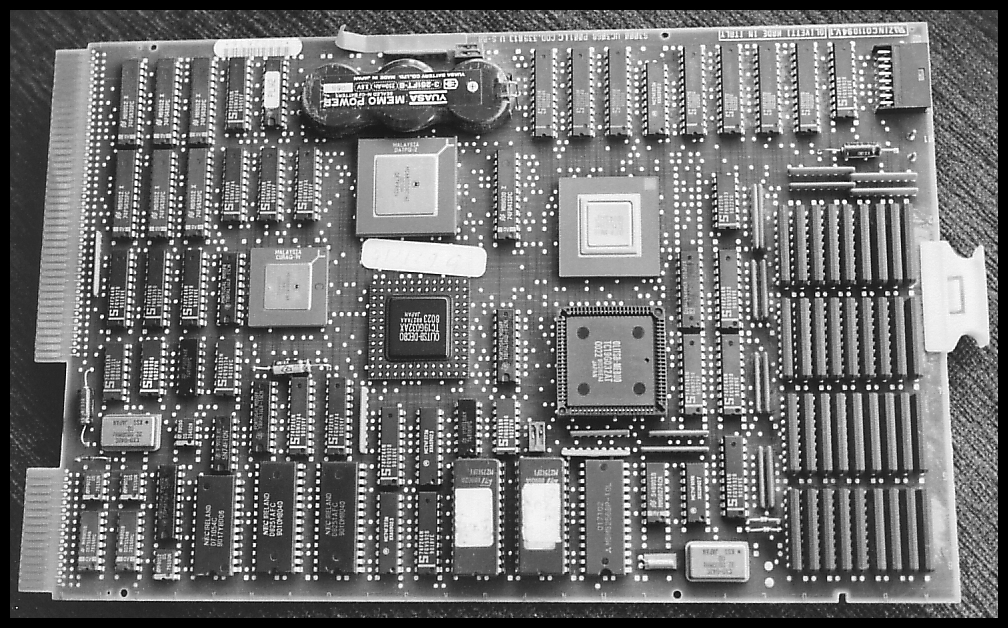

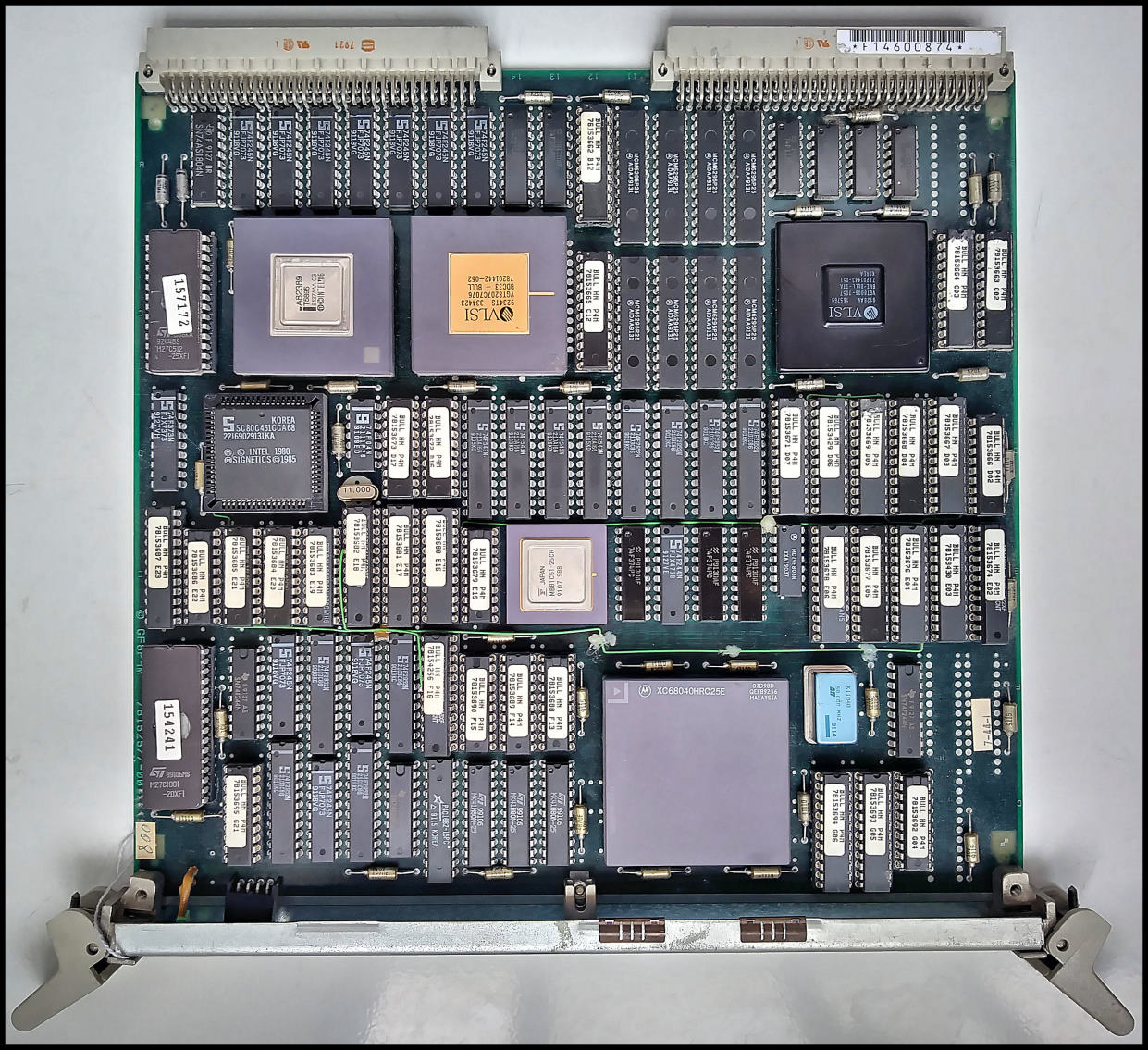

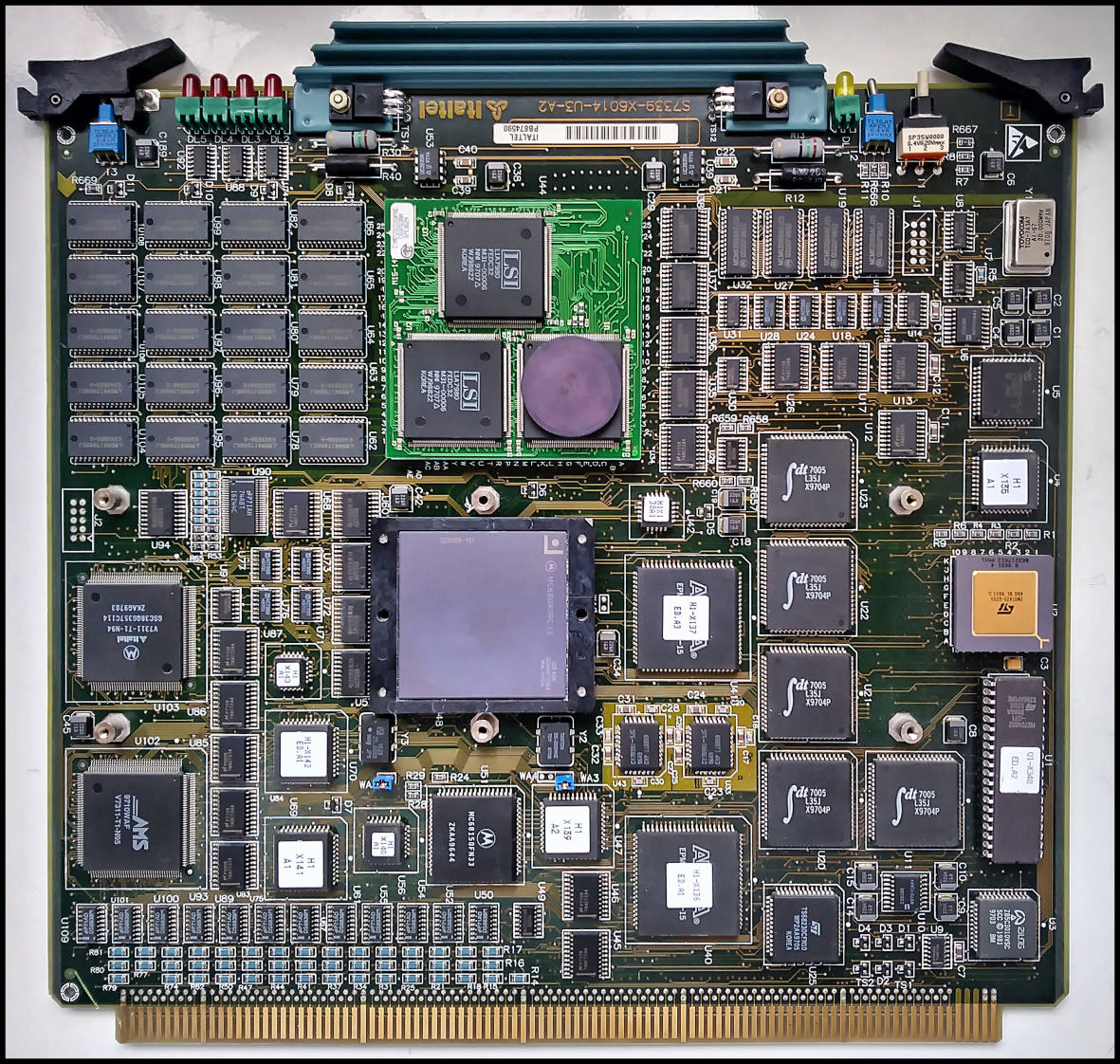

Scheda processore di minicomputer Wang VS5000 (1989) in cui la CPU è realizzata con ASIC CMOS fabbricati da VLSI Inc.

Scheda CPU di minicomputer Prime 5370 (1991). Prime Computer Inc., alternativamente scritto "PR1ME", è stato un produttore statunitense di minicomputer a 16 e 32 bit attivo tra il 1972 ed il 1992. I sistemi Prime erano equipaggiati con CPU proprietarie realizzate dapprima con logica TTL a media scala di integrazione, poi con gate array ECL ed infine con ASIC VLSI CMOS. Si trattava di macchine multiutente di fascia alta orientate in primo luogo al CAD/CAM (settore nel quale la Prime entrò grazie alla collaborazione con la Ford Motor Company, facendo concorrenza alla CDC ed alla DEC) e alle applicazioni di database. Il sistema operativo, denominato PRIMOS, è interessante per il fatto di essere stato uno dei pochissimi sistemi operativi -forse l'unico- sviluppato con il linguaggio FORTRAN IV (in seguito Prime utilizzò i linguaggi PL/1 e Modula-2, ma mai il C). Lo stesso hardware delle macchine Prime era ottimizzato per eseguire codice FORTRAN. Fin dall'inizio degli anni Ottanta nella configurazione di base di questi sistemi rientravano una o più connessioni di rete locale secondo uno standard proprietario derivato dal Token Ring e detto "PrimeNet". Il 5370 apparteneva alla fascia di macchine Prime più alta ed offriva prestazioni comparabili a quelle delle macchine ECL quali il modello 6450 ad un prezzo inferiore di circa la metà. La velocità di elaborazione dichiarata era di circa 17 Dhrystone MIPS. Il processore del 5370 era costituito da 2 CPU identiche a 32 bit, ciascuna con la propria memoria cache, realizzate con gate array CMOS da 50.000 gate. Non si trattava in realtà di una vera e propria macchina SMP quanto piuttosto di un sistema asimmetrico a due processori, dei quali uno dedicato in esclusiva all'esecuzione del sistema operativo, che operava nello stesso tempo come sistema fault-tolerant potendo funzionare anche con una sola CPU qualora l'altra si fosse guastata. La memoria RAM andava da un minimo di 64 ad un massimo di 128 MB; la macchina poteva essere dotata di più dischi SCSI o ESDI da 5,25 pollici (capacità unitaria di 637 MB) fino ad un massimo di 32 GB. La scheda della CPU era dotata di due bus di I/O indipendenti a 32 bit, un bus dedicato di collegamento con la memoria ed un microprocessore di gestione a 16 bit. I possessori dei modelli meno potenti della famiglia Prime 5000 potevano effettuare l'upgrade delle loro macchine installandovi la sola scheda CPU ed ottenendo così un sistema dalle prestazioni pari a quelle del 5370. A partire dal mese di Luglio del 1992 Prime cessò la produzione di minicomputer per dedicarsi unicamente al software, finché nel 1998 venne assorbita dalla Parametric Technology Corporation.

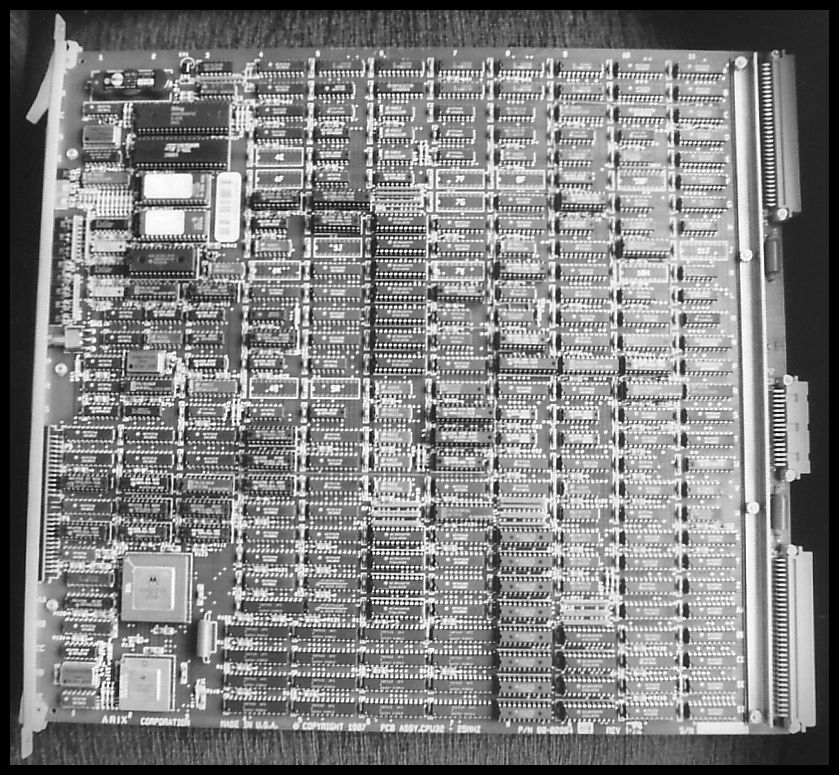

Scheda processore di un server Prime 2950 (1990/1): la CPU è realizzata con 4 gate array VLSI CMOS di Motorola, da 7.500 gate NAND equivalenti ciascuno.

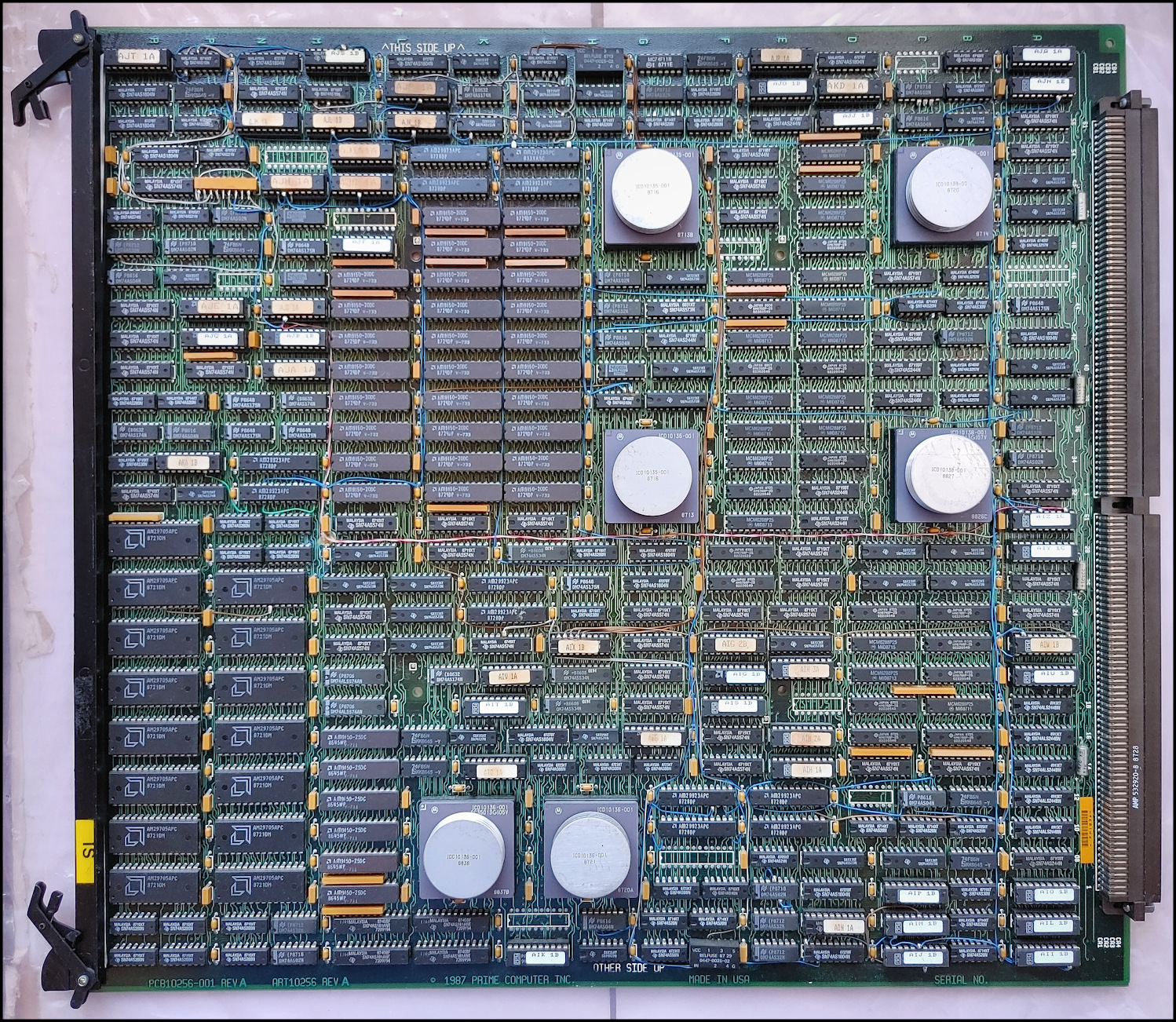

Scheda CPU di minicomputer Prime 4000 (1987), fabbricata, come la precedente, con gate array VLSI Motorola.

Scheda processore per centrale telefonica AT&T 5ESS con CPU WE32100 a 14 MHz. Il 32100 è una versione aggiornata e migliorata del WE32000, anche noto come Bellmac-32 prima del passaggio dei Laboratori Bell (Bell Labs) alla Western Electric, uno dei primissimi microprocessori monolitici a 32 bit messi in commercio (1985). E' stato prodotto fino alla fine degli anni Novanta ed ha trovato applicazioni soprattutto nei prodotti della AT&T. Si tratta di una tipica CPU con architettura CISC. Il 32100, come il predecessore 32000, è storicamente interessante anche perché è stato tra i primi microprocessori complessi ad essere progettati ed implementati con l'allora innovativa tecnica denominata "logica a domino" (domino logic).

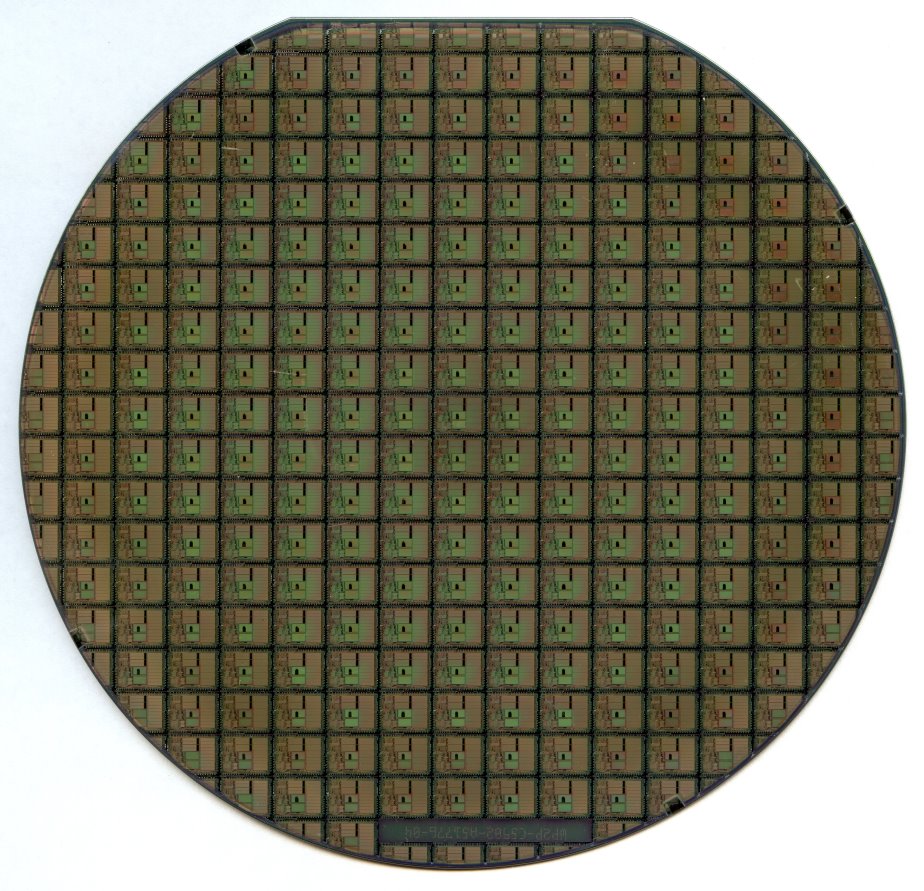

Wafer completo di integrati Vetronix MIC-320. Si tratta di un controller di bus per sistemi a CPU multipla e risorse distribuite utilizzato principalmente in campo militare in applicazioni dove l'affidabilità è caratteristica essenziale e viene ottenuta principalmente con la ridondanza dei dispositivi installati. Esso implementa il protocollo MIC che stato impiegato nel corso degli anni in numerosi apparati militari (ad es. il carro armato M1A2 Abrams). Come altri componenti di questa categoria il MIC-320 è stato per anni sottoposto a restrizioni sull'esportazione dagli USA (vedi http://www.exportlawblog.com/archives/450). La Vetronix Research è una società statunitense specializzata nella produzione di apparecchiature e componenti per la difesa e l'impiego in condizioni ambientali difficili.

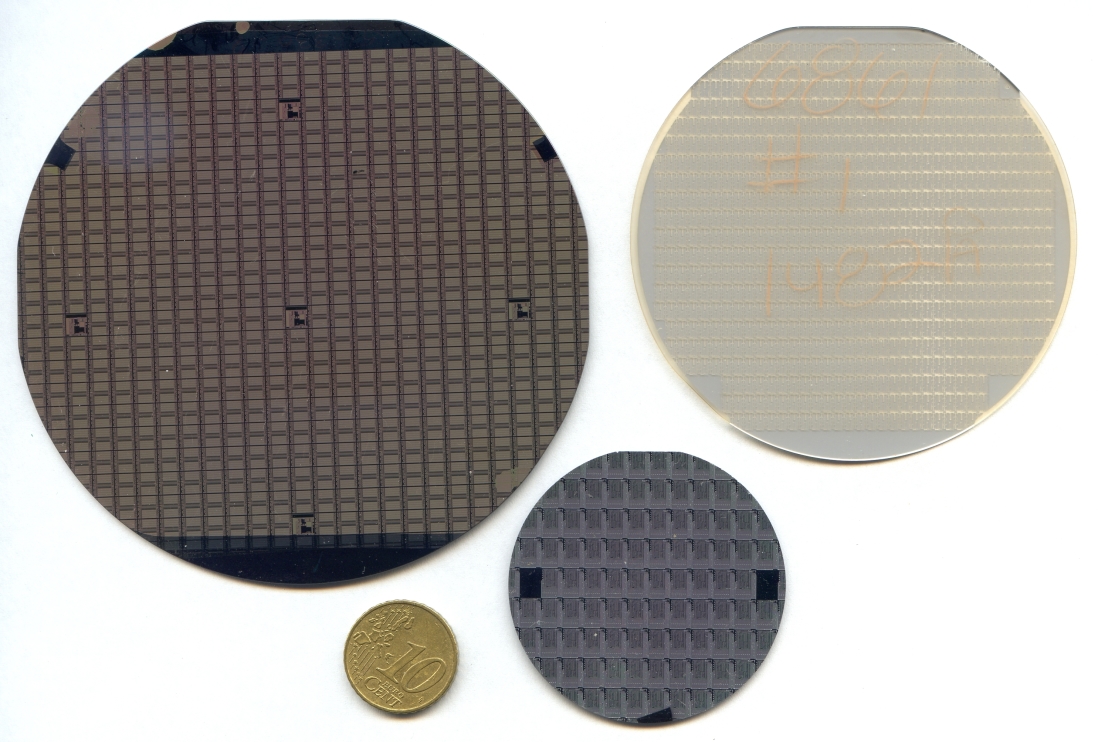

Tre wafer di diverse dimensioni, contenenti memorie DRAM (a sinistra ed in alto a destra) e circuiti logici LSI, in basso.

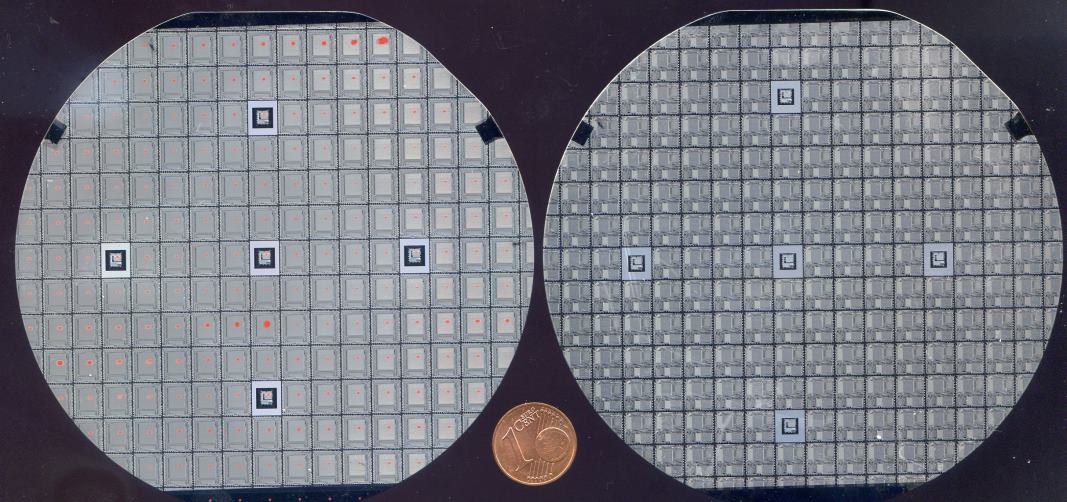

Coppia di wafer da 3 pollici contenenti memorie DRAM (a sinistra, il modello è sconosciuto) e, a destra, circuiti LSI NMOS fabbricati da Signetics. Entrambi risalgono agli anni Settanta. Nell'esemplare a sinistra si nota che quasi tutti i chip sono marcati come difettosi mediante una gocciolina di inchiostro rosso.

Wafer di chip Rockwell C5902 (circa 1998). Si tratta di ASIC VLSI CMOS contenenti una CPU a 16 bit, memoria RAM e ROM e varie porte di comunicazione, destinati principalmente al settore delle telecomunicazioni. In sostanza il C5902 è un System On Chip (SOC) che integra tutta la logica necessaria alla gestione di applicazioni quali centralini telefonici, apparati di comunicazione e fax, modem ISDN e così via. Gli integrati contenuti in questo wafer non hanno passato le prove di funzionalità e sono stati marcati come scartati con una gocciolina d'inchiostro.

Wafer da 8 pollici contenente gate array CMOS VLSI, molto probabilmente LSI Logic.

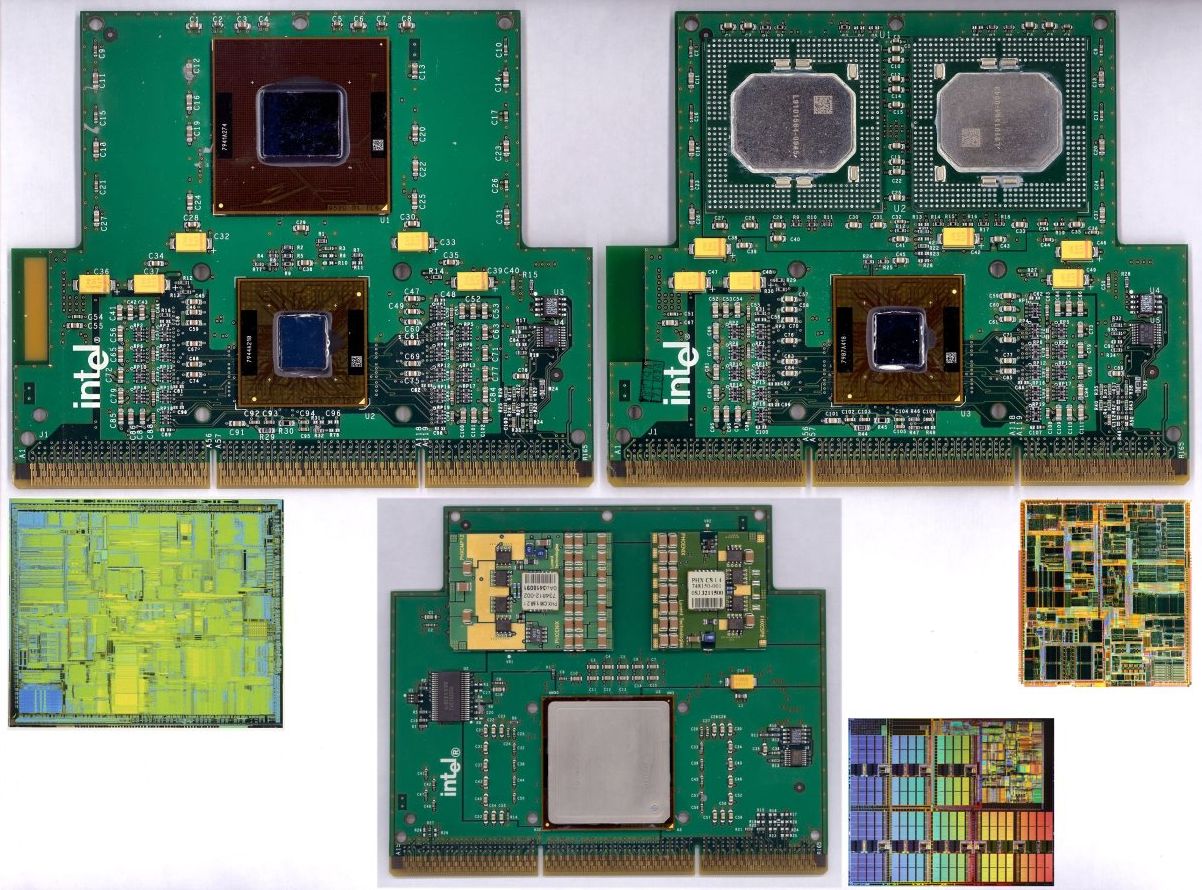

Le tre CPU Intel Xeon con architettura P6: Tanner a 500 MHz/FSB a 100 MHz con core derivato da quello del Pentium III (in alto a sinistra); Drake a 400 MHz/FSB a 100 MHz, 2 MB di cache, core Pentium II Deschutes (in alto a destra); in basso, non raffigurato in scala, Cascades con core Pentium III Coppermine a 900 MHz, FSB a 133 MHz e 1 MB di cache. La corretta sequenza storica è quindi dall'alto a destra in senso antiorario. Il "Drake" è stato introdotto il 29.6.1998 ed era fabbricato con processo a 250 nm: si tratta in assoluto del primo processore denominato "Xeon". E' contenuto in cartuccia SECC per Slot 2. Lo Xeon "Tanner" venne invece introdotto il 16.3.1999; era anch'esso fabbricato con processo a 250 nm e contenuto in cartuccia SECC/Slot 2 a 330 contatti. Infine lo Xeon "Cascades" fu introdotto da Intel il 25.10.1999: era fabbricato con processo a 180 nm e a differenza dei predecessori incorporava la cache L2 nel chip della CPU. Qui è riprodotta la versione a 900 MHz -core Coppermine- con 2 MB di cache L2. Questa CPU può funzionare in configurazioni SMP a 8 processori mentre gli Xeon Drake e Tanner sono limitati a 4 vie (la limitazione può comunque essere superata con chipset specifici). Facendo riferimento alla foto sopra, nel Drake e nel Tanner la CPU è costituita dal chip in basso mentre quelli in alto contengono la cache. Nel caso dello Xeon Drake qui visibile ci sono 2 chip di cache da 1 MB ciascuno.

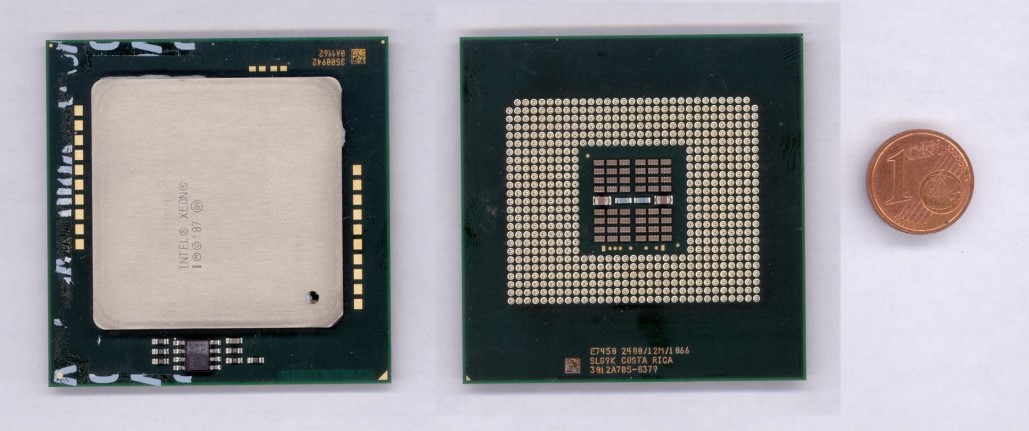

Processore Intel Xeon E7450/SLG9K a 6 core/12 MB di cache, 2,4 GHz e FSB a 1.066 MHz (Socket mPGA-604). Questo processore introdotto nel 2007 utilizza il core "Dunnington" a 45 nm (variante del Penryn) ed è stato la prima CPU Intel multicore, cioè con più di due core. La cache L3 è unificata per tutti i core ed è ampia 12 MB. Il numero totale di transistor è pari a circa 1,9 miliardi.

Engineering sample di processore Intel Xeon E7500 "Beckton" a 8 core, 1,87 GHz e 24 MB di cache L3. E' contenuto in package FC-LGA8 a 1567 punti di contatto. Le CPU della serie Beckton si basano sulla microarchitettura Nehalem, la stessa delle CPU Core i7, ed hanno la circuiteria di buffering integrata nel processore, potendo così utilizzare fino a 16 DIMM DDR3 standard in luogo delle più "calde" FB-DIMM. I modelli della serie 75xx hanno 4 interfacce QPI (Quick Path Interconnect), grazie alle quali possono essere adoperati in configurazioni con un massimo di 8 socket (64 core totali) contro i soli 2 socket massimi della serie 65xx. Contengono 8 cache L2 (una per ciascun core) da 256 KB ed una cache L3 unificata ampia 24 MB; sono fabbricati con processo P1266 a 45 nm. La microarchitettura Nehalem, presentata nel 2007, segnò la reintroduzione dell'hyperthreading e la scelta di cache di secondo livello più piccole accoppiate ad una cache L3 molto ampia e comune a tutti i core.

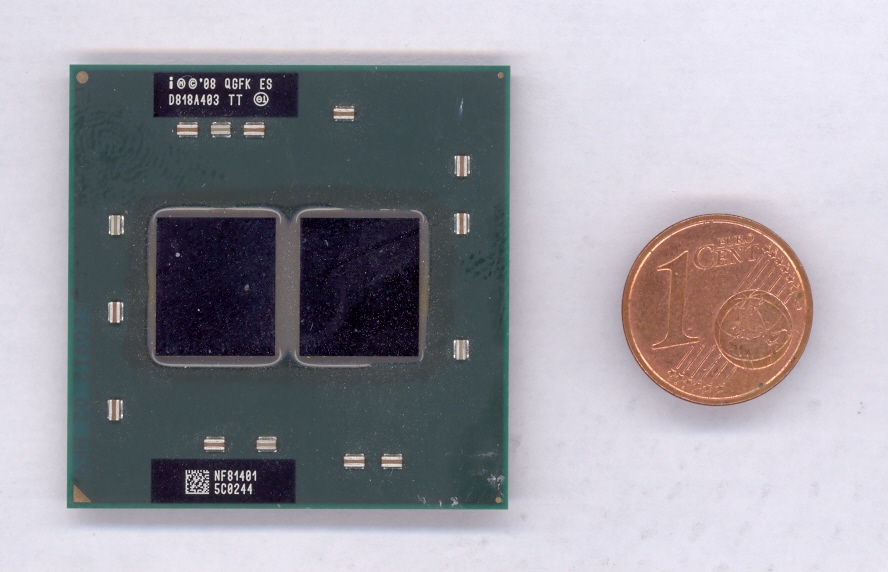

Misterioso engineering sample Intel del 2008 siglato QGFK: se ne trovano in vendita su Ebay con la medesima sigla identificati come prototipi della CPU Auburndale (mai commercializzata da Intel), ma è più probabile -dato che i due chip sono identici- che si tratti di un prototipo di un processore quad-core.