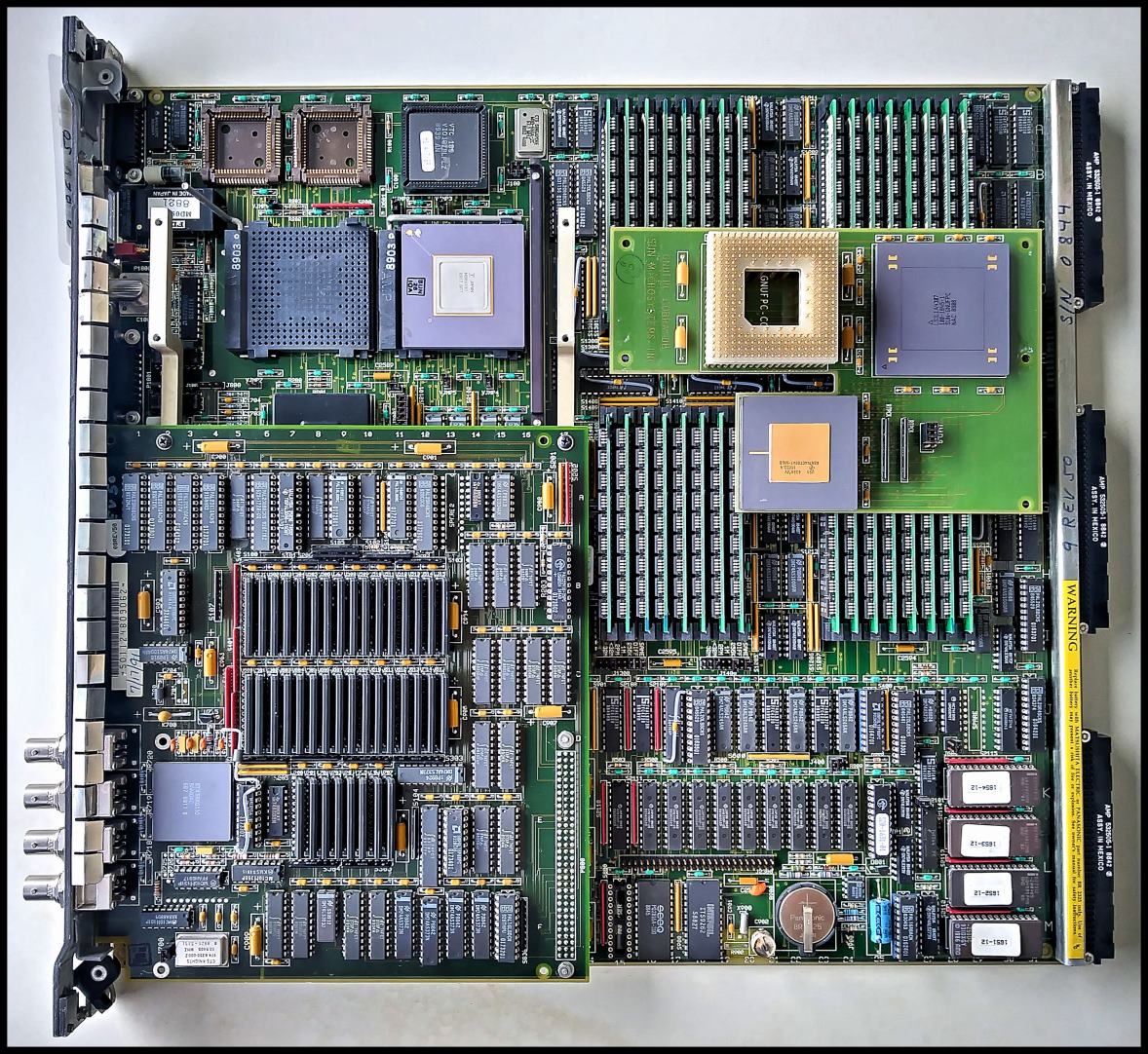

Schede con CPU SPARC di prima generazione/1st generation SPARC CPU boards (SPARC V7, Sun-4)

Sun 4/330, 4/110, 4/150

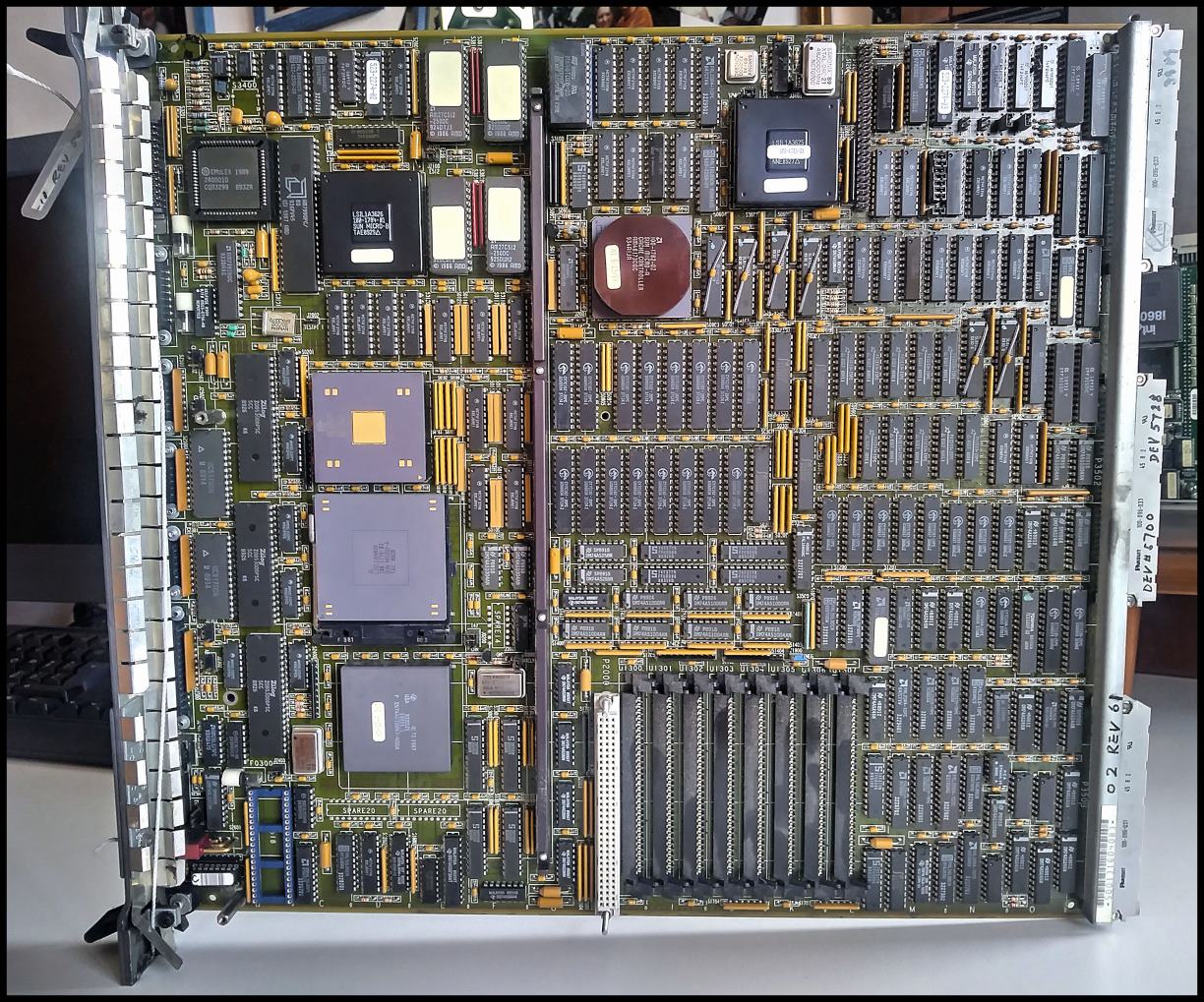

Scheda madre di una SPARCstation 330 "Stingray" (Sun SPARC 4/330), tipo Sun 4300, con unità di elaborazione SPARC Cypress CY7C601 a 25 MHz e FPU Texas Instruments 8847. Ulteriori chip di supporto (ASIC) includono in particolare la MMU, inserita su zoccolo ZIF tra la CPU e la FPU, ed il controller della cache (il chip AMD nella parte alta della scheda). Si tratta dell'implementazione forse più comune dell'architettura Sun-4 basata su processore SPARC V7. Supporta i sistemi operativi SunOS dalla versione 3.02 e Solaris dalla versione 2.1 alla 2.4. In questo esemplare il framebuffer è stato tolto prima della foto.

Vedi: https://commons.wikimedia.org/wiki/File:Museo_de_Inform%C3%A1tica_Hist%C3%B3rica_(MIH)_-_UNIZAR_-_Sun_Sparcstation_330_motherboard_-_full_view.jpg, http://www.obsolyte.com/sunPICS/sparc_vme/sun4_330_card.jpg.

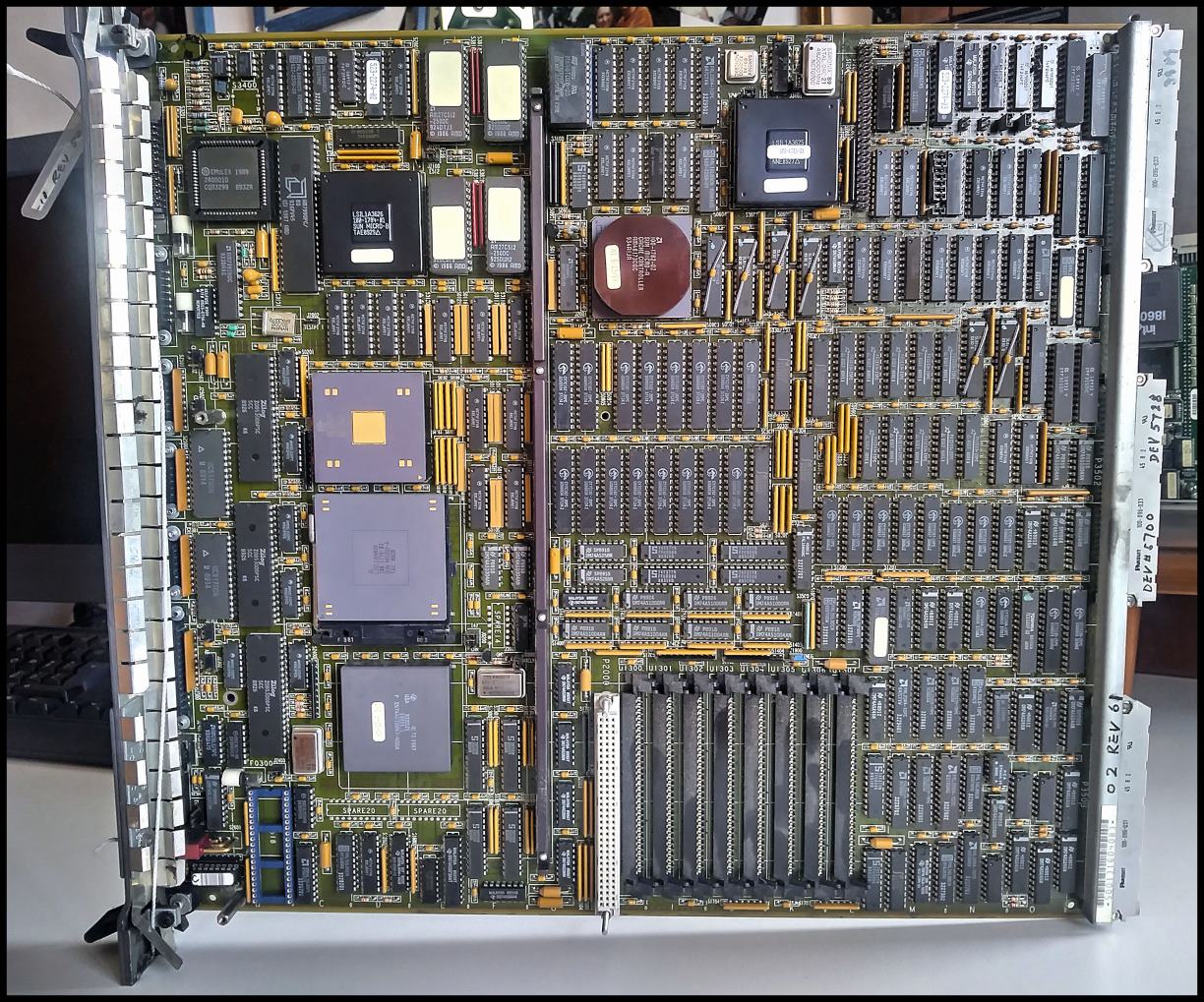

Scheda CPU di una SPARCstation Sun 4/110, 1989/1990. I componenti di base sono i medesimi della 4/330, in particolare la CPU e la FPU che però è montata su una daughterboard (scheda aggiuntiva, in basso). Immediatamente a sinistra, lo spazio per l'eventuale doppio zoccolo dell'unità in virgola mobile Weitek (ALU e moltiplicatore).

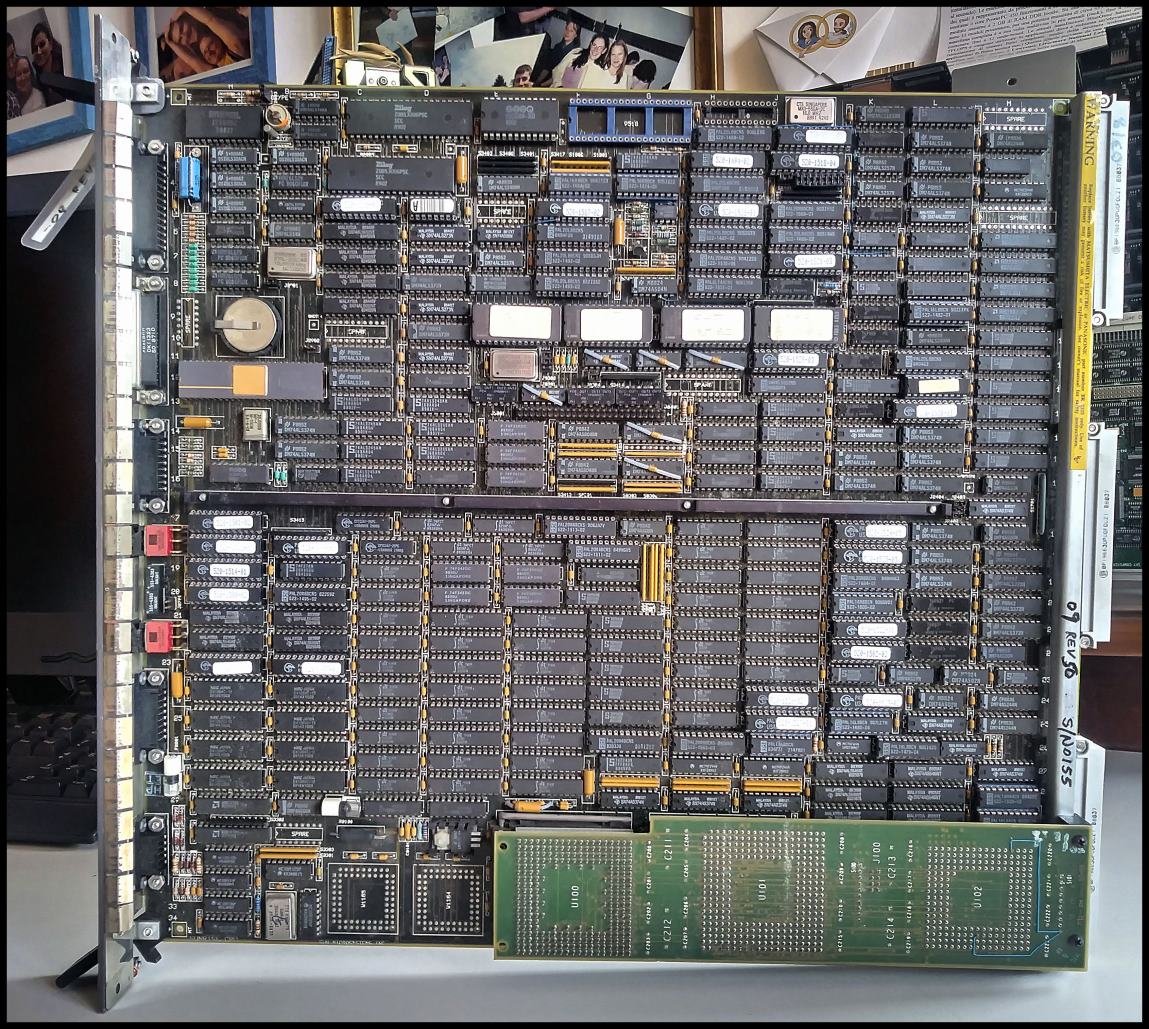

Scheda CPU di una SPARCstation Sun 4/150 "Cobra" del 1989 con CPU SPARC V7 Fujitsu MB86900 a 14,3 MHz, FPU Texas Instruments TI8847 su scheda opzionale (è possibile in alternativa montare una FPU Weitek 1164/1164, in alto a sinistra i due zoccoli liberi).

Il Fujitsu MB86900 era un microprocessore con set di istruzioni SPARC V7 ed ha rappresentato la prima implementazione commerciale single-chip di questa architettura. Veniva fabbricato con processo CMOS a 1,2 micron, 3 livelli di interconnessione in Alluminio, lo stesso processo utilizzato per l’unità in virgola mobile MB86910. L’insieme dei due chip integrava circa 20.000 porte logiche equivalenti; la CPU da sola ne conteneva approssimativamente 12.000, corrispondenti a circa 110.000 transistor. Un tipico processore CISC dello stesso periodo quale l’Intel 80386 ne integrava invece più di 250.000. Il package è di tipo PGA a 256 pin. L’MB86900 è stato impiegato, fra l’altro, nella prima workstation SPARC commerciale, la Sun 4/110 "Cobra" e nel primo server con CPU SPARC (Sun 4/260). La tecnologia di produzione permetteva una frequenza massima di clock di 33 MHz; accoppiato ad una cache di dimensioni adeguate, questo processore poteva raggiungere i 20 MIPS. Più comunemente, tuttavia, le macchine con esso equipaggiate offrivano prestazioni comprese tra 10 e 15 MIPS a fronte di un ciclo macchina tipico di 60 ns. Circa un quarto della logica interna dell’86900 è occupata dal register file. I gate (porte logiche) che costituiscono l’unità di elaborazione sono gerarchicamente suddivisi in blocchi, sotto-blocchi e sotto-sotto-blocchi per consentire un calcolo preciso dei ritardi di propagazione (e dunque dei tempi di esecuzione delle varie istruzioni). Funzionalmente l’86900 risulta suddiviso in 4 unità:

- Register File Unit, che contiene 128 registri d’uso generale a 32 bit. Delle 32 finestre di registri possibili ne vengono implementate 7;

- Execution Unit, che contiene una ALU ed uno shifter a 32 bit con la relativa logica di controllo ed i registri locali. La pipeline dell’unità di esecuzione è formata da 4 stadi e prevede due distinti livelli di inoltro (forwarding) o bypass;

- Instruction Fetch Unit, che provvede alla generazione degli indirizzi e viene usata nella fase di Decode (decodifica dell’istruzione) per generare gli indirizzi di salto ed in quella di Execute (esecuzione) per generare gli indirizzi degli operandi. Vi sono 4 registri locali Program Counter corrispondenti ciascuno ad un distinto stadio della pipeline dell’unità di esecuzione. L’unità IFU contiene 4 ulteriori registri (Trap Base Register, Trap Type Register, Y register -utilizzato durante le moltiplicazioni- e Window Invalid Mask Register);

- Control Unit, che controlla l’unità di esecuzione e contiene fra l’altro il registro dello stato della CPU (Processor Status Register), la logica di gestione delle eccezioni e quella di interfaccia con l’esterno.

Le unità di esecuzione e di Instruction Fetch comprendono circa 3.800 gate NAND-equivalenti ciascuna, mentre altri 4.200 gate sono impiegati nell’unità di controllo. Nel suo complesso dunque l’86900 contiene circa 12.000 gate equivalenti e 4.000 bit di registri. La maggior parte delle istruzioni può essere eseguita dal processore in un solo ciclo di clock; vi sono tuttavia alcune istruzioni che ne richiedono due o più (la media globale è di circa 1,5 cicli per istruzione). Le istruzioni più complesse vengono convertite internamente in sequenze di operazioni atomiche da 1 ciclo di clock ciascuna.

Esternamente la CPU 86900 presenta 3 distinti bus, tutti a 32 bit: quello dei dati e delle istruzioni (I/D bus), il bus di collegamento con la FPU (F bus) ed il bus indirizzi (Address bus). Il bus I/D è bidirezionale e collega direttamente la CPU alla cache; quello degli indirizzi è diviso in due gruppi, AL (Address Low) corrispondente ai bit da 0 a 16 e AH (Address High) che corrisponde ai bit da 17 a 31. Il progetto del processore 86900 è iniziato nel Luglio 1985 ed ha portato ai primi esemplari funzionanti nell’Aprile 1986. La CPU è stata progettata da Anant Agrawal e Masood Namjoo, entrambi della Fujitsu.Per contro un altro processore SPARC V7, il Cypress CY7C601, venne progettato tra la prima parte del 1987 e la metà del 1988 e poteva raggiungere la frequenza di 40 MHz. Si trattava di una CPU cosiddetta di seconda generazione, in quanto commercializzata successivamente al pionieristico 86900. A differenza di quest’ultimo, in gran parte un gate array progettato e realizzato con le stesse tecniche degli ordinari ASIC, il 7C601 era un dispositivo full-custom. Non aveva alcuna cache interna e quella esterna era tipicamente di 64 KB, write-back, completamente associativa. Come l’86900, il 7C601 eseguiva in media un’istruzione ogni 1,5 cicli di clock ed aveva una pipeline interna a 4 stadi. Era fabbricato con processo CMOS a 0,8 micron e integrava 1,8 milioni di transistor, circa 600.000 in più rispetto alla CPU Intel 80486 realizzata all’incirca nel medesimo periodo. Il package è un PGA a 207 pin. Poteva essere interfacciato tanto con una FPU Weitek 1164/1165 quanto con una Texas Instruments 8847 senza necessità di logica aggiuntiva. A seconda del tipo di FPU utilizzato le prestazioni in virgola mobile, sia per l’86900 che per il 7C601, variavano tra 1,1 ed 1,8 MFLOPS a doppia precisione. Va detto che l’8847 offriva una velocità di esecuzione circa tripla rispetto a quella della FPU 86910, realizzata con la stessa tecnica della CPU 86900.

Vedi: http://www.alyon.org/InfosTechniques/informatique/SunHardwareReference/sunfaq.html.

Vedi: http://oldcomputers-ddns.org/public/pub/rechner/other_hardware/sun/sparc_4-330/sun-4x.pdf.